[導讀] 基于ZYNQ實現復雜嵌入式系統(tǒng)非常便利,其應用領域也越來越廣泛,本文來從對ZYNQ芯片架構的理解來談談個人體會。

俯瞰zynq

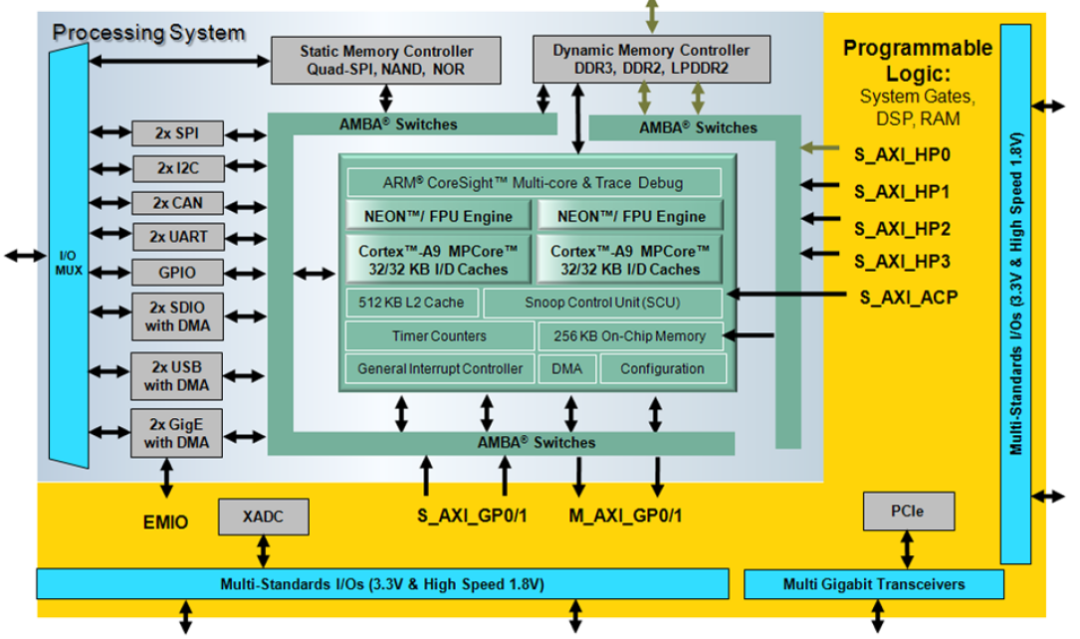

ZYNQ主要由兩大部分組成:

處理系統(tǒng)PS(Processing System):上圖左上部分即是PS部分,包括:

同構雙核ARM Cortex A9的對稱多處理器 (Symmetric Multi-Processing,SMP)

豐富的外設,2×SPI,2×I2C,2×CAN,2×UART,2×SDIO,2×USB,2×GigE,GPIO

靜態(tài)存儲控制器:Quad-SPI,NAND,NOR

動態(tài)存儲控制器:DDR3,DDR2,LPDDR2

可編程邏輯PL(Programmable logic):兼容賽靈思7系列FPGA

基于Artix的芯片:Z-7010以及Z-7020

基于Kintex的芯片:Z-7030以及Z-7045

ZYNQ處理系統(tǒng)端PS所有的外設都連接在AMBA(Advanced Microcontroller Bus Architecture)總線,而基于FPGA設計的IP則可以通過AXI接口掛載在AMBA總線上,從而實現內部各組件的互聯互通。這里涉及到兩個概念:

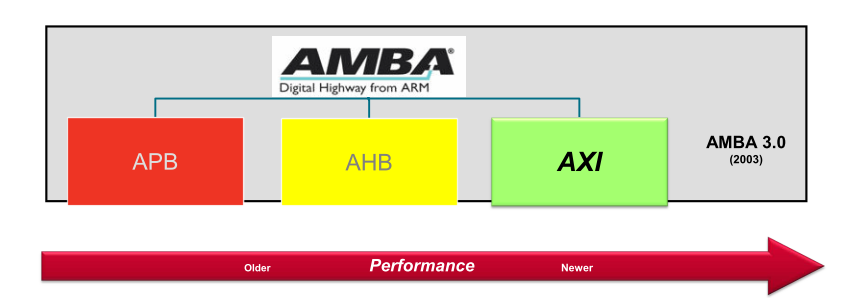

AMBA總線,熟悉ARM架構的朋友應該都大致了解, AMBA是ARM公司的注冊商標。是一種用于片上系統(tǒng)(SoC)設計中功能塊的連接和管理的開放標準片上互連規(guī)范。它促進了具有總線結構及多控制器或組件的多核處理器設計開發(fā)。自成立以來,AMBA已廣為應用,遠遠超出了微控制器設備領域。如今,AMBA已廣泛用于各種ASIC和SoC部件,包括在現代便攜式移動設備中使用的應用處理器。

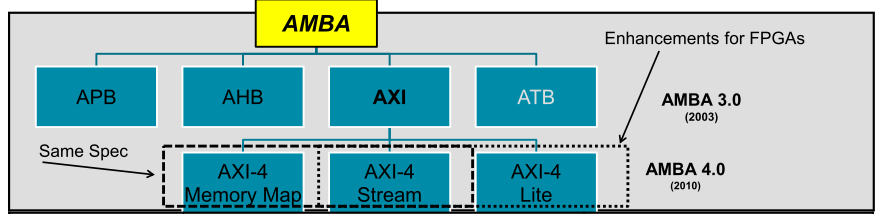

高級可擴展接口AXI(Advanced eXtensible Interface):是ARM公司AMBA 3.0 和AMBA 4.0規(guī)范的一部分,是并行高性能,同步,高頻,多主機,多從機通訊接口,主要設計用于片上通訊。為啥說AXI是AMBA的一部分,看看下面兩個圖就可以比較清晰的了解。

ZYNQ的高度靈活性

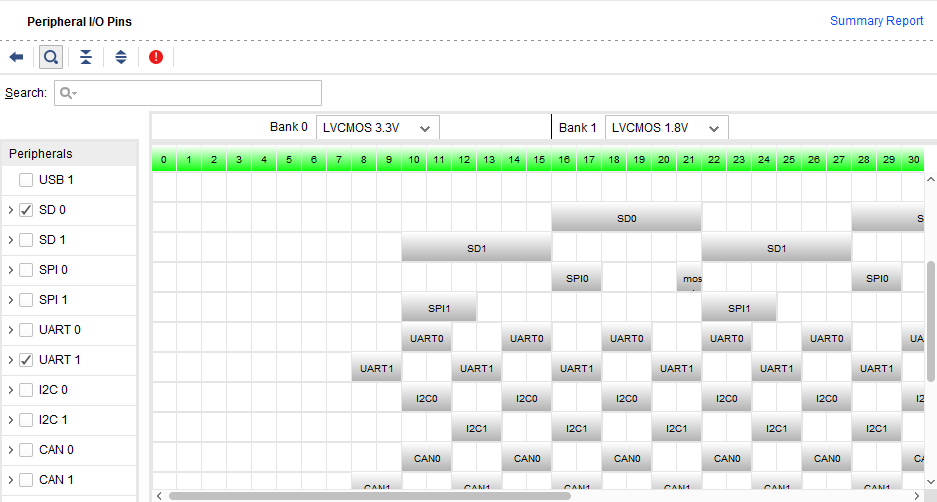

靈活的PS端IO復用

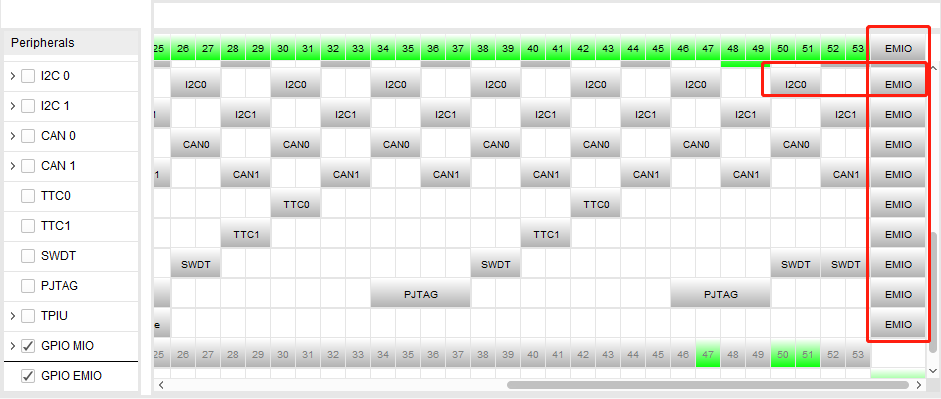

Multiplexed I/O (MIO):PS端外設IO復用,這是什么概念呢?前面介紹了ZYNQ主要分PS/PL兩大組成模塊,PS端前面介紹的外設如USB/CAN/GPIO/UART等都必要需要引腳與外界打交道,這里所謂的復用與常見的單片機、處理器里引腳復用的概念一樣。但是(這里劃重點),ZYNQ具有高達54個PS引腳支持MIO,MIO具有非常高的靈活度以達到靈活配置,這給硬件設計、PCB布板帶來了極大的便利!,MIO的配置利用vivado軟件可以實現靈活配置,如下圖所示。

硬件工程師往往發(fā)現對一個復雜的系統(tǒng)的布局布線,常常會很困難,也常因為不合理的布局布線而陷入EMC深坑。ZYNQ的IO引腳高度靈活性,無疑在電路設計方面提供極大的方便,可實現非常靈活的PCB布局布線。從而在EMC性能改善方面帶來了很大便利。

靈活的PS-PL互連接口

Extended Multiplexed I/O (EMIO):擴展MIO,如果想通過PS來訪問PL又不想浪費AXI總線時,就可以通過EMIO接口來訪問PL。54個I/O中,其中一部分只能用于MIO,大部分可以用于MIO或EMIO,少量引腳只能通過EMIO訪問。

如上圖,比如I2C0則可以通過EMIO映射到PL端的引腳輸出,這無疑又增加了更多的靈活性!

PS-PL接口HP0-HP3:如上架構圖中AXI high-performance slave ports (HP0-HP3) 實現了PS-PL的接口

可配置的32位或64位數據寬度

只能訪問片上存儲器OCM(On chip memory)和DDR

AXI FIFO接口(AFI)利用1KB FIFOs來緩沖大數據傳輸

PS-PL接口GP0-GP1:如上架構圖中AXI general-purpose ports

兩個PS主接口連接到PL的兩個從設備

32位數據寬度

一個連接到CPU內存的64位加速器一致端口(ACP)AXI從接口,ACP 是 SCU (一致性控制單元)上的一個 64 位從機接口,實現從 PL 到 PS 的異步 cache 一致性接入點。ACP 是可以被很多 PL 主機所訪問的,用以實現和 APU 處理器相同的方式訪問存儲子系統(tǒng)。這能達到提升整體性能、改善功耗和簡化軟件的效果。ACP 接口的表現和標準的 AXI 從機接口是一樣的,支持大多數標準讀和寫的操作而不需要在 PL 部件中加入額外的一致性操作。

處理器事件總線信號事件信息到CPU

PL外設IP中斷到PS通用中斷控制器(GIC)

四個DMA通道RDY/ACK信號

擴展多路復用I/O (EMIO)允許PS外設端口訪問PL邏輯和設備I/O引腳。

時鐘以及復位信號:

四個PS時鐘帶使能控制連接到PL

四個PS復位信號連接到PL

靈活的時鐘系統(tǒng)

PS時鐘源:

PS端具有4個外部時鐘源引腳

PS端具有3個PLL時鐘模塊

PS端具有4個時鐘源可輸出到PL

PL端具有7個時鐘源

PL端時鐘源域相對PS端不同

PL端時鐘可靈活來自PL端外部引腳,因為FPGA的硬可編程性,完全靈活配置

也可使用PS端的4個時鐘源

注意

PL和PS之間的時鐘同步是由PS端處理

PL不能提供時鐘給PS使用

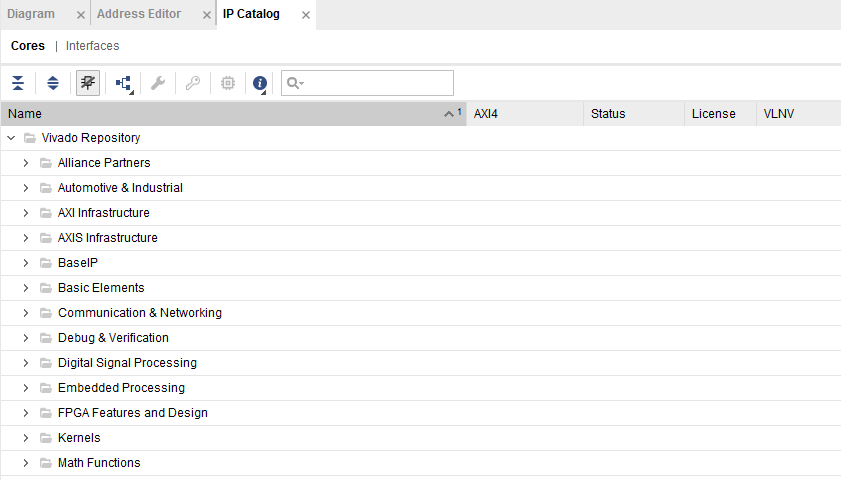

豐富的IP庫

Zynq 是一種SoC,具有大量的標準 IP,這些部件不再需要重新設計而直接可用。以這樣的方式提升了設計抽象層級,加上重用預先測試和驗證過的部件,開發(fā)將被加速,而成本則可以降低。就像常說的:“ 為什么要重新發(fā)明輪子呢?”。

Vivado內置了大量的IP可供使用,比如數學計算IP,信號處理IP、圖像視頻處理IP,通信互連(以太網、DDS、調制、軟件無線電、錯誤校驗)、處理器IP(MicroBlaze等)、甚至人工智能算法IP。

比如信號處理IP,由于采用FPGA硬邏輯實現信號處理無需CPU計算,對于實現復雜的信號運算(比如實現一個非常高階的FIR濾波、多點FFT計算)具有非常大優(yōu)勢。

雙ARM硬核處理器

如架構圖,ZYNQ內置了雙ARM Cortex-A9硬核,對軟件設計提供了極大的靈活性,在該處理器上可運行Linux,Android等復雜的操作系統(tǒng),相比常規(guī)FPGA嵌軟核IP的做法具有更強大的運算處理能力,你可能會說其處理器的運算能力相比時下的其他ARM芯片或稍有不足,但基本能滿足常規(guī)的醫(yī)療、工業(yè)領域等嵌入式系統(tǒng)應用需求。

PL/PS的有機結合

通過前面的簡要分析介紹,不難發(fā)現PL可編程硬件邏輯及處理器單元的結合做的非常好。

PL端:可設計出高靈活的外設系統(tǒng),同時可編程硬件邏輯電路,可實現真正的硬并行處理、硬實時系統(tǒng)

PS端:PL端與PS的有機結合,有可實現對這種高靈活、硬并行、硬實時處理系統(tǒng)實現集中軟件管理

試想,如果一個系統(tǒng)需要實現硬實時、硬并行,復雜外設互連系統(tǒng):

或許會采用多微控制器(比如單片機)+處理器方案,微處理器實現實時需求,處理器運行Linux實現上層業(yè)務邏輯的方式。

或者采用FPGA+處理器來實現。

這兩種方案技術復雜度都非常高,硬件電路PCB設計比較復雜,軟件開發(fā)以及維護也會增加復雜度。而ZYNQ則可以很好的解決此類系統(tǒng)設計需求,真正做到system on chip,這也是SOC的一個很好的體現。

總結一下

ZYNQ這種高度靈活性,豐富的外設,豐富的IP庫,以及vivado強大易用的開發(fā)環(huán)境,對使用ZYNQ進行嵌入式系統(tǒng)設計帶來了非常多優(yōu)勢。

審核編輯 :李倩

-

芯片

+關注

關注

463文章

54010瀏覽量

466080 -

嵌入式系統(tǒng)

+關注

關注

41文章

3747瀏覽量

133638 -

Zynq

+關注

關注

10文章

630瀏覽量

49450

原文標題:從ZYNQ芯片架構談談其為何如此誘人

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

電能質量在線監(jiān)測裝置的核心芯片架構對裝置性能有哪些影響?

【VPX650 】青翼凌云科技基于 VPX 系統(tǒng)架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

ZYNQ UltraScalePlus RFSOC QSPI Flash固化常見問題說明

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

CH367連接zynq問題

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構分析」閱讀體驗】+NVlink技術從應用到原理

正點原子Z20 ZYNQ 開發(fā)板發(fā)布!板載FMC LPC、LVDS LCD和WIFI&藍牙等接口,資料豐富!

Zynq7000處理器的配置詳解

ZYNQ芯片架構的理解

ZYNQ芯片架構的理解

評論