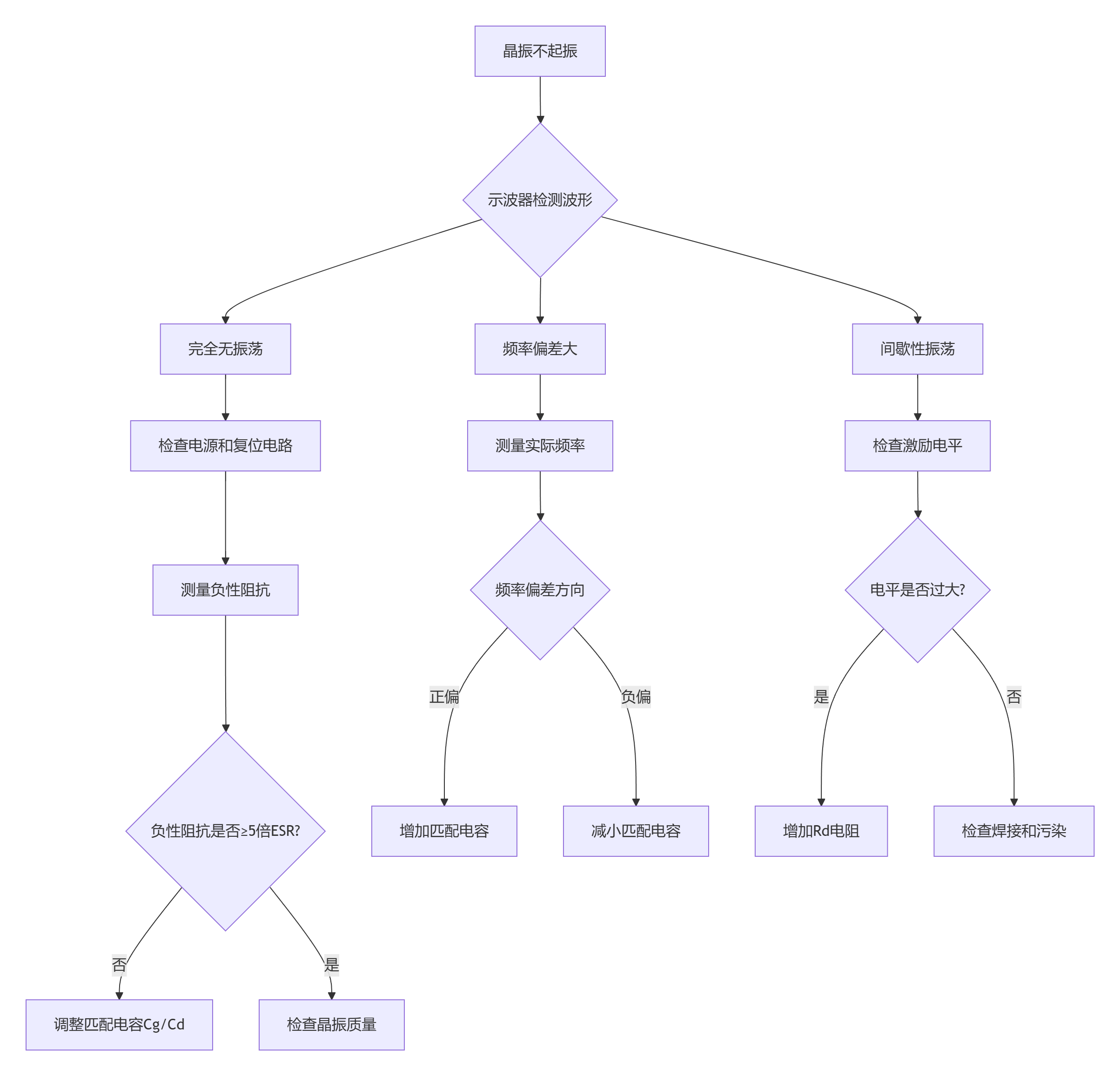

無源晶振(晶體)是數字電路的“心臟”,其設計質量直接決定系統的穩定性和可靠性。SOSET索斯特為您總結了這張檢查流程圖,幫你快速把握核心設計環節:

?

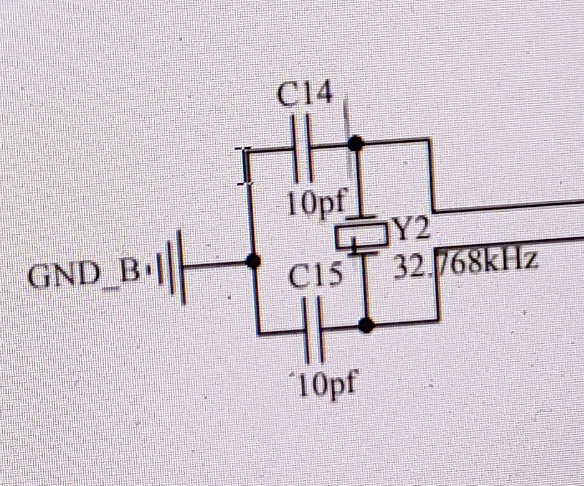

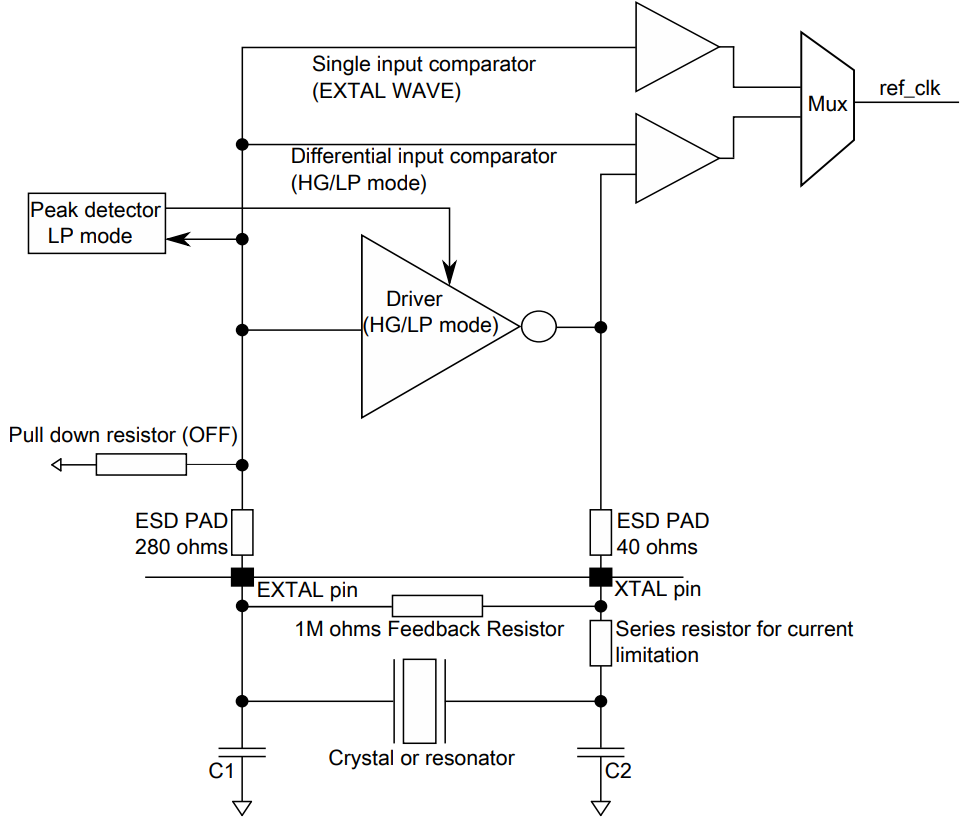

電路參考1

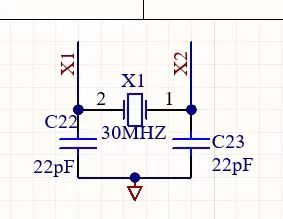

電路參考1 電路參考2

電路參考2下面我們來詳細探討每個環節的關鍵要點。

?? ??核心參數匹配??

??負載電容(CL)匹配??是無源晶振設計的核心。晶振的標稱頻率是在特定負載電容下校準的。失配會導致??頻率偏移??。計算時需考慮:

- ??公式??:最常用的簡化公式為 CL = (C1 * C2) / (C1 + C2) + Cstray。其中 C1 和 C2 為外部匹配電容,Cstray 為PCB走線和芯片引腳的寄生電容,通常為 ??3pF至5pF??。若 C1 = C2,則可簡化為 CL = C1/2 + Cstray。

- ??電容選型??:優先選擇 ??NP0/C0G?? 材質的電容,其溫度穩定性好。容值常見于6pF至30pF之間。

- ??頻率微調??:若實測頻率偏差較大,可通過微調C1、C2容值來校正。通常負載電容每增加1pF,頻率會降低約0.5ppm。

??激勵功率(DL)?? 需控制在晶振規格書限定的范圍內。過驅動可能導致晶振??機械損傷??甚至??早期失效??。可通過串聯一個限流電阻(Rext,通常為0-1kΩ)來調整。使用示波器觀察波形,若正弦波峰峰被削平,說明可能過驅,需調整Rext。??負性阻抗(-R)?? 是評估振蕩電路穩定性的關鍵指標。為確保在各種條件下(如溫度變化、老化)都能穩定起振,電路的負阻絕對值應至少為晶振等效串聯電阻(ESR)的 ??5倍?? 以上。可通過??負阻測試??驗證:在晶振回路中串聯一個可變電阻Rtest,逐漸增大其阻值直至振蕩停止,則負性阻抗 |-R| ≈ Rtest + ESR。

??PCB布局布線要點??

優秀的PCB布局對降低EMI和保證穩定性至關重要。

- ??位置與走線??:晶振務必??靠近MCU??的時鐘引腳放置,走線長度建議??小于10mm??。XIN和XOUT走線應??等長、并行走線??,類似差分對,線寬8-12mil,間距≥3倍線寬。??嚴禁在時鐘信號路徑上使用過孔??。

- ??隔離與包地??:晶振下方及周圍??禁止布設其他信號線??,特別是高頻信號線。晶振周圍用??接地銅箔??包圍(屏蔽環),并每隔100-150mil放置接地過孔,形成法拉第籠屏蔽效應。

- ??電源去耦??:為MCU的振蕩器電路電源引腳提供??潔凈的電源??。通常需要在電源引腳附近放置一個??0.1μF??的去耦電容,有時還會并聯一個更小容值的電容(如0.01μF)以濾除高頻噪聲。

??振蕩電路穩定性保障??

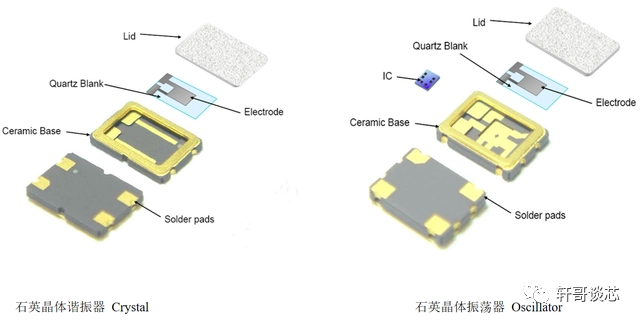

- ??反饋電阻(Rf)??:多數MCU內部已集成(通常1-10MΩ)。它使反相器工作在線性區,提供增益,對啟動有幫助。若發現低溫下起振困難,可嘗試在外部并聯1MΩ電阻以增強負性阻抗,改善啟動特性。

- ??啟動特性??:負載電容CL越小,負性阻抗越大,啟動通常越快,但頻率穩定性可能稍差;CL越大,啟動可能稍慢,但振蕩更穩定,遠端相位噪聲可能更好。需根據應用權衡。

- ??溫度影響??:明確應用的工作溫度范圍,選擇相應等級的晶振(如工業級-40℃至+85℃)。對于溫度變化大的環境,需關注晶振的??溫度頻差??參數,或考慮選用有源晶振(如TCXO)。

??測試驗證與故障排查??

設計完成后,必須進行實測驗證。下表匯總了常見問題及對策:

常見問題 | 可能原因 | 解決思路 |

|---|---|---|

??不起振?? | 負載電容嚴重不匹配、負性阻抗裕量不足、PCB布局不良、MCU振蕩器配置錯誤 | 檢查電路配置和參數計算,優化PCB布局,驗證軟件配置 |

??頻率偏差大?? | 負載電容不匹配、晶振本身精度不足、激勵功率不當 | 微調匹配電容容值、檢查晶振精度規格、用示波器觀察波形調整Rext |

??低溫啟動失敗?? | 負性阻抗裕量不足 | 嘗試并聯1MΩ反饋電阻、適當減小負載電容CL以增大負性阻抗 |

??常溫工作正常,運行一段時間后偶發死機?? | 振蕩裕量不足,在溫度、電壓波動或器件老化時臨界失振 | 進行負阻測試,確保負性阻抗絕對值至少為晶振ESR的5倍以上 |

??EMC輻射超標?? | 晶振回路成為輻射天線、電源去耦不足 | 優化PCB布局(包地、屏蔽)、在電源線或信號線上增加磁珠濾波、確保屏蔽罩良好接地 |

測試時,建議使用高阻抗探頭(如10MΩ阻抗,≤5pF電容)的示波器,帶寬至少為晶振頻率的5倍,以減少測量對電路的影響。

關鍵總結

無源晶振設計是一個系統工程,關鍵在于??精確的參數匹配(尤其是負載電容)、嚴謹的PCB布局布線(最短路徑、完整包地)、以及充分的振蕩裕量驗證(負阻測試)??。設計時務必仔細查閱MCU和晶振的數據手冊,理論計算與實測迭代結合,才能打造出穩定可靠的“心臟”。希望這些要點能對你的設計有所幫助!如果你在具體應用中遇到特殊挑戰,歡迎進一步討論。

-

電路設計

+關注

關注

6745文章

2743瀏覽量

220033 -

無源晶振

+關注

關注

1文章

894瀏覽量

17925 -

晶振電路設計

+關注

關注

0文章

5瀏覽量

5509

發布評論請先 登錄

無源晶振的等效電路與電路結構解析

SOSET索斯特分享:無源晶振電路設計指南

SOSET索斯特分享:無源晶振電路設計指南

評論