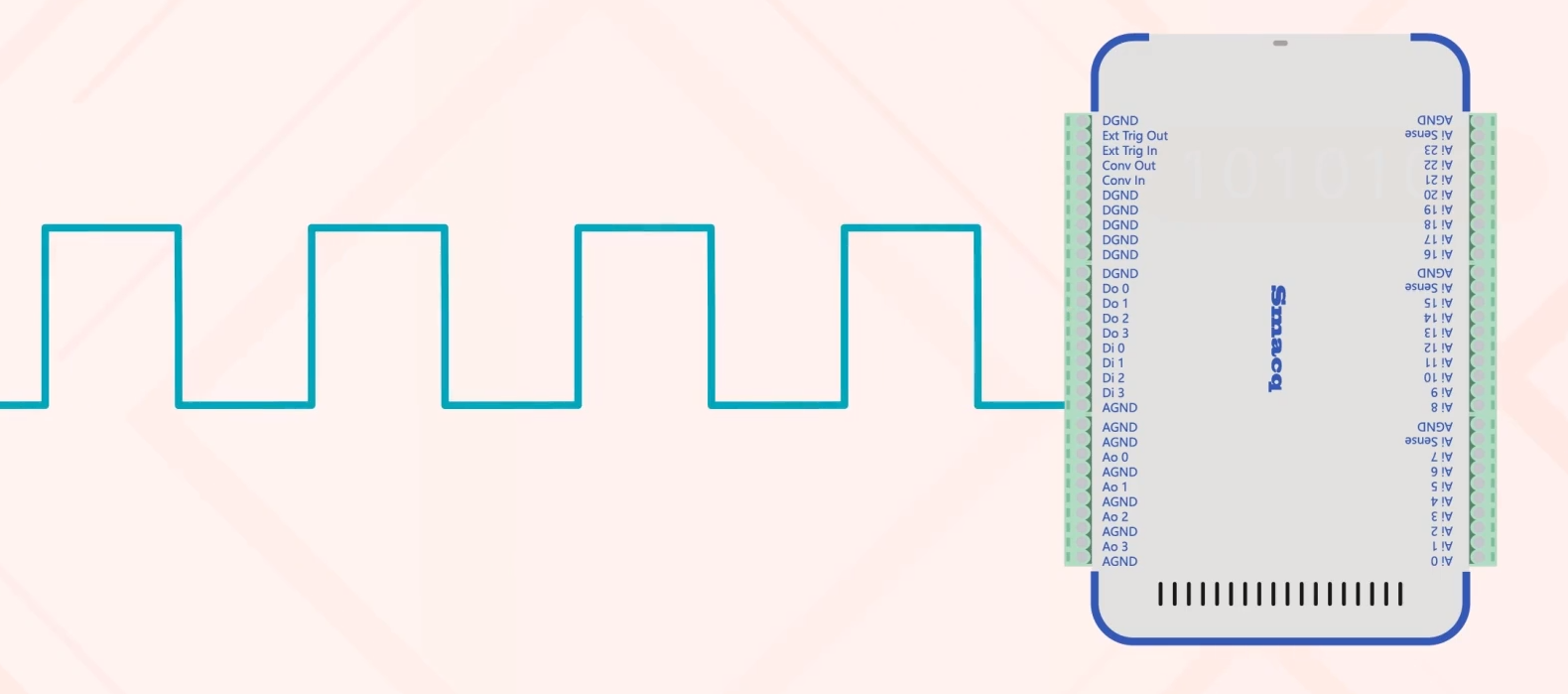

在上期模擬信號文章的最后,我們向大家提了一個問題:方波脈沖信號是模擬信號還是數字信號?

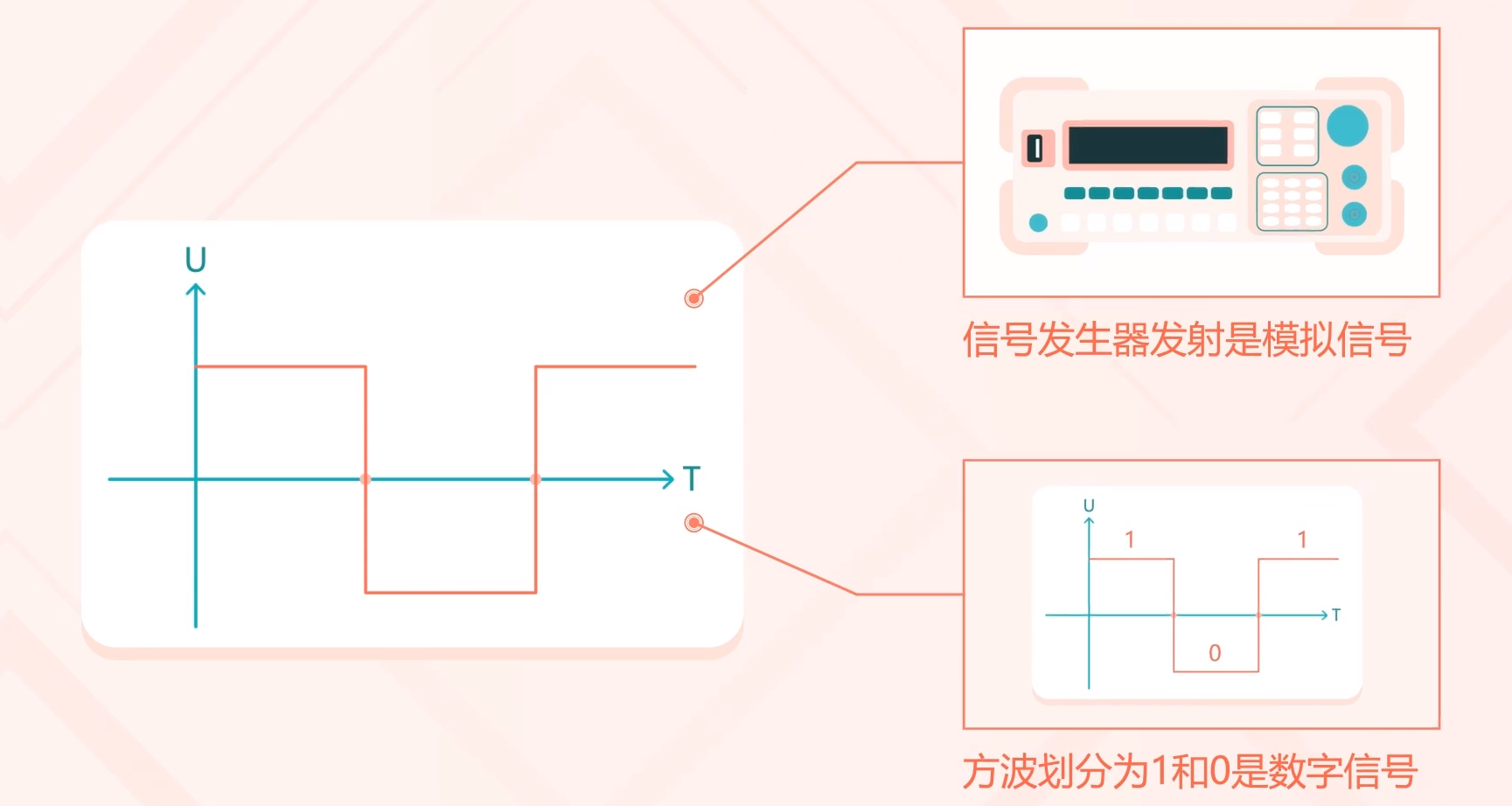

其實它是什么信號要看它是怎樣表示的,以這個方波舉例,當方波從信號發生器中發射出來,它是一個模擬信號。當我們根據它的高低電平,把這個方波劃分為1和0的時候,它就成為了數字信號。

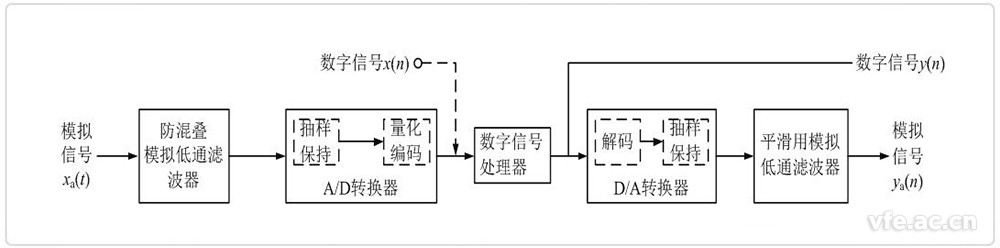

那么一個模擬信號是怎樣轉化為數字信號的呢?

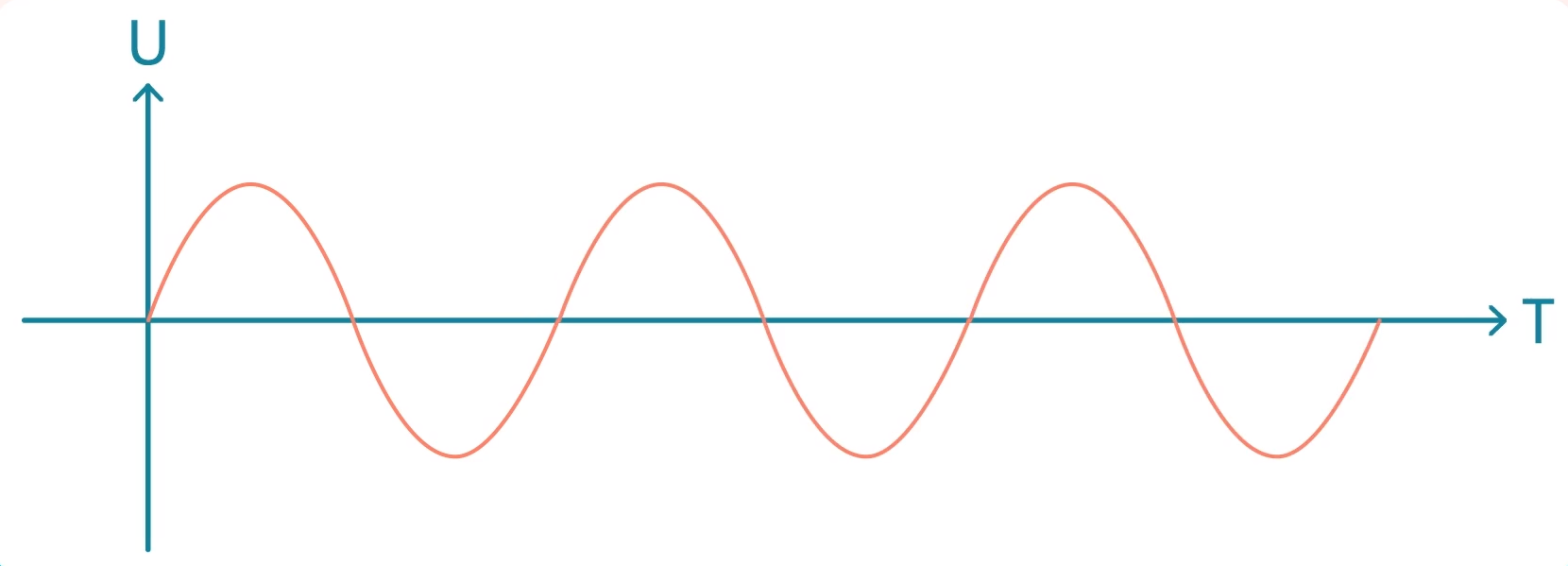

大家已經知道模擬信號在時間及幅度值上均是連續的。

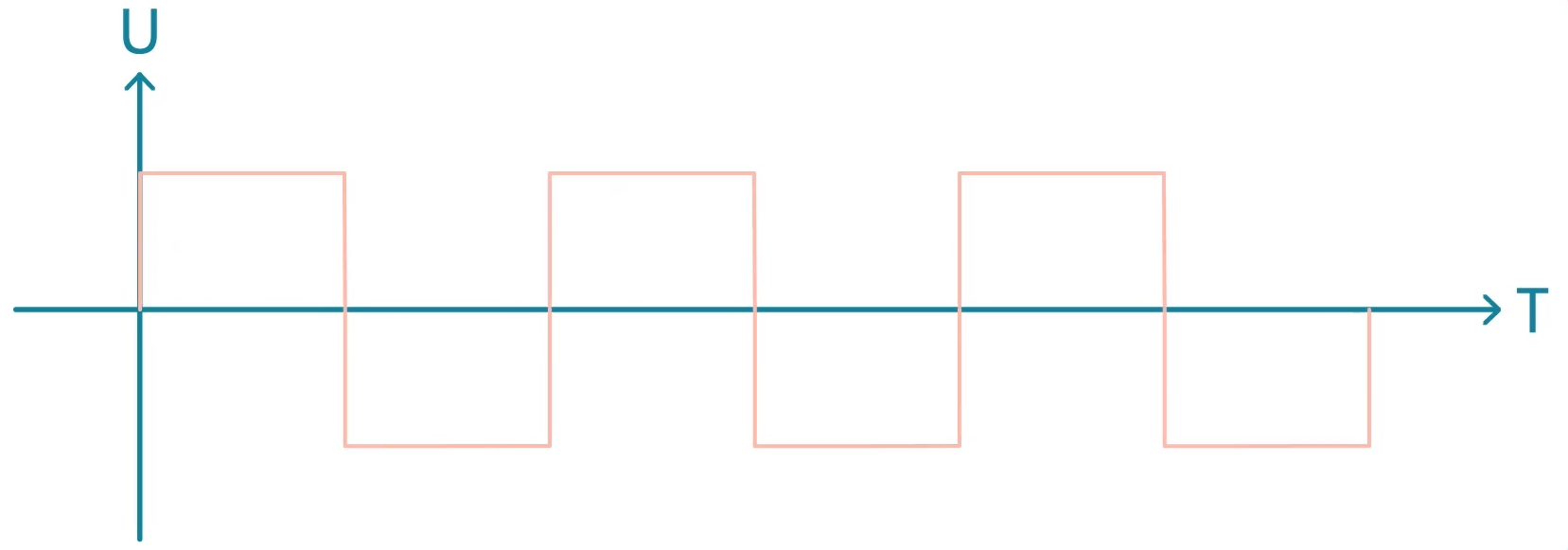

而與其對應的數字信號在時間及幅度值上都是離散的。

自然界中當然不存在這樣的信號,所以只有經過人為加工,才能使信號離散化。加工的具體過程就是:采樣、量化、編碼,模擬信號只有經過這三個步驟的處理才會被認定為數字信號。(采樣、量化、編碼的過程我們會在后面的文章中敘述,這里先行略過。)

二、0、1的判斷標準

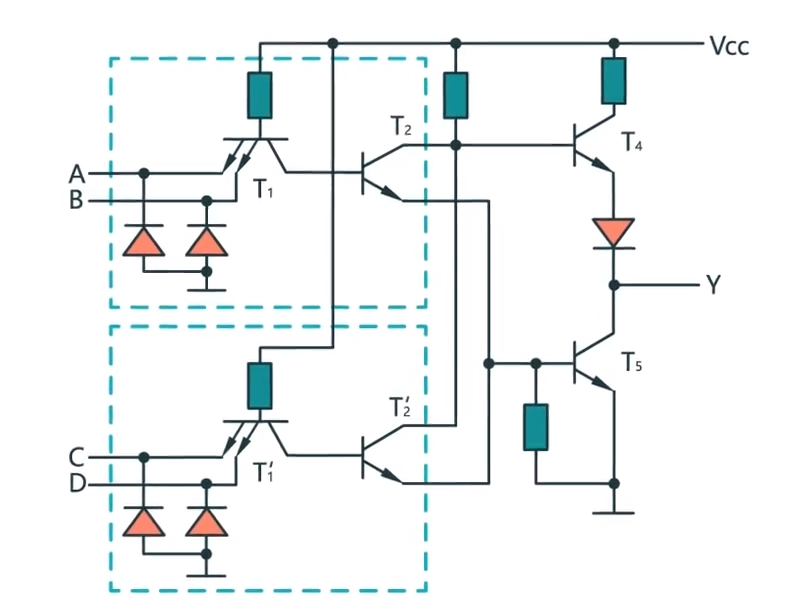

雖然轉換后的數字信號只有“0”、“1”兩種狀態,但它仍是以電壓電流的形式運行在電路當中。所以我們就需要一些標準來判斷數字信號是“0”還是“1”。例如TTL電路,它是晶體管-晶體管邏輯電路(Transistor-Transistor Logic)的縮寫,這里的晶體管是指雙極性晶體管(BJT),也就是三極管。

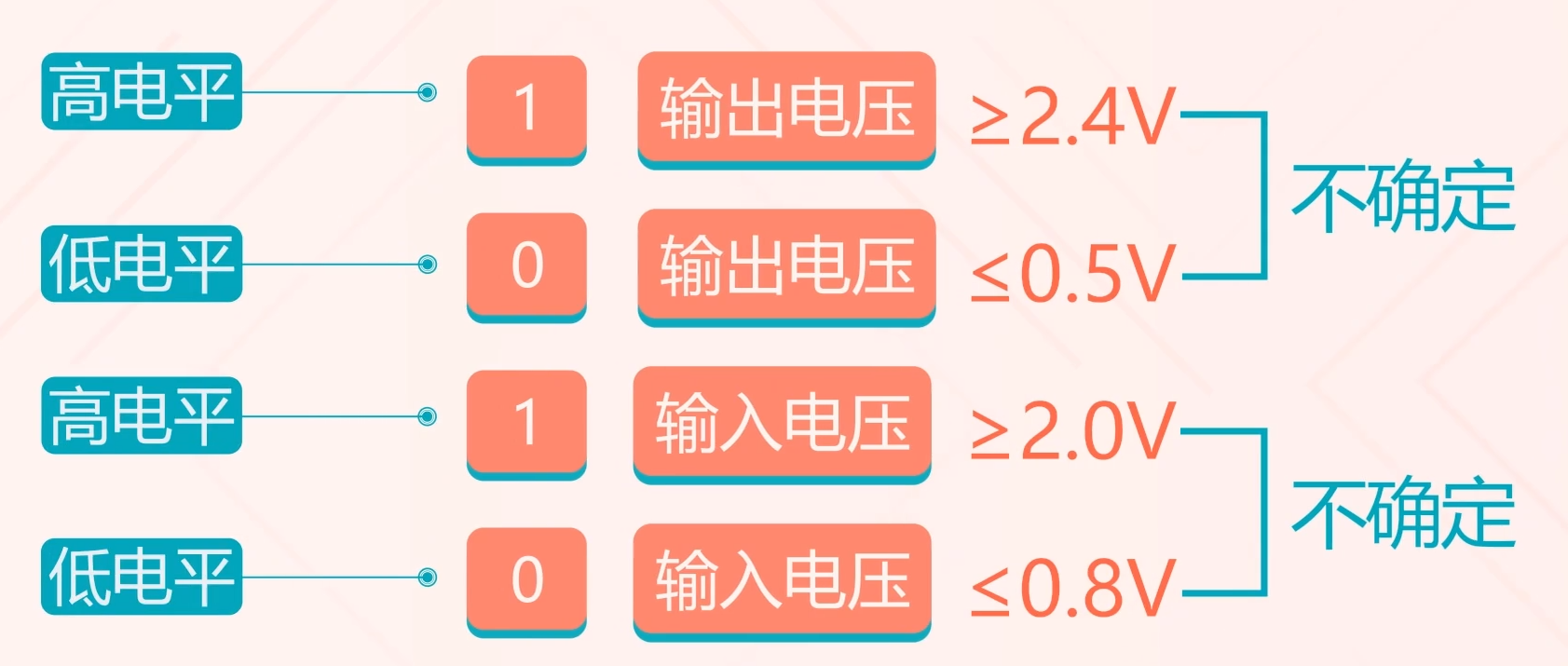

TTL電平信號規定,+5V等價與“1”(高電平),0V等價于“0” (低電平)。這樣的數據通信及電平規定方式,被稱作TTL信號系統。不過在具體應用中,高低電平的判斷是一個范圍值。以電路中使用5V電源為例,當輸出電壓大于等于2.4V時,表示“1”;小于等于0.5V時,表示“0”。當輸入電壓大于等于2.0V時,表示“1”;小于等于0.8V時,表示“0”。

但是為了改善噪聲容限、減小功耗、提高運行速度,就將電壓砍掉了一部分,于是就有了LVTTL電路。它又分為3.3V、2.5V以及更低電壓的LVTTL(Low Voltage TTL)。

以3.3V LVTTL為例,它的電源是3.3V;輸出的高電平大于等于2.4V,低電平小于等于0.4V;輸入的高電平大于等于2V,低電平小于等于0.8V。如果電壓值在0.4V到2.4V之間,是不確定的狀態,電路不能清楚的判斷它是高電平還是低電平。這樣的情況在電路中是不應該出現的。

三、數字電路

現在我們已經大致清楚了數字信號的產生以及在電路中如何傳輸,但它只有“0”和“1”兩種狀態,怎么才能將其應用于實際生活,解決復雜問題呢?這就要依靠數字電路了,它是一種用數字信號完成對數字量進行算術運算和邏輯運算的電路。

可以分為組合邏輯電路和時序邏輯電路兩大類。

1、組合邏輯電路

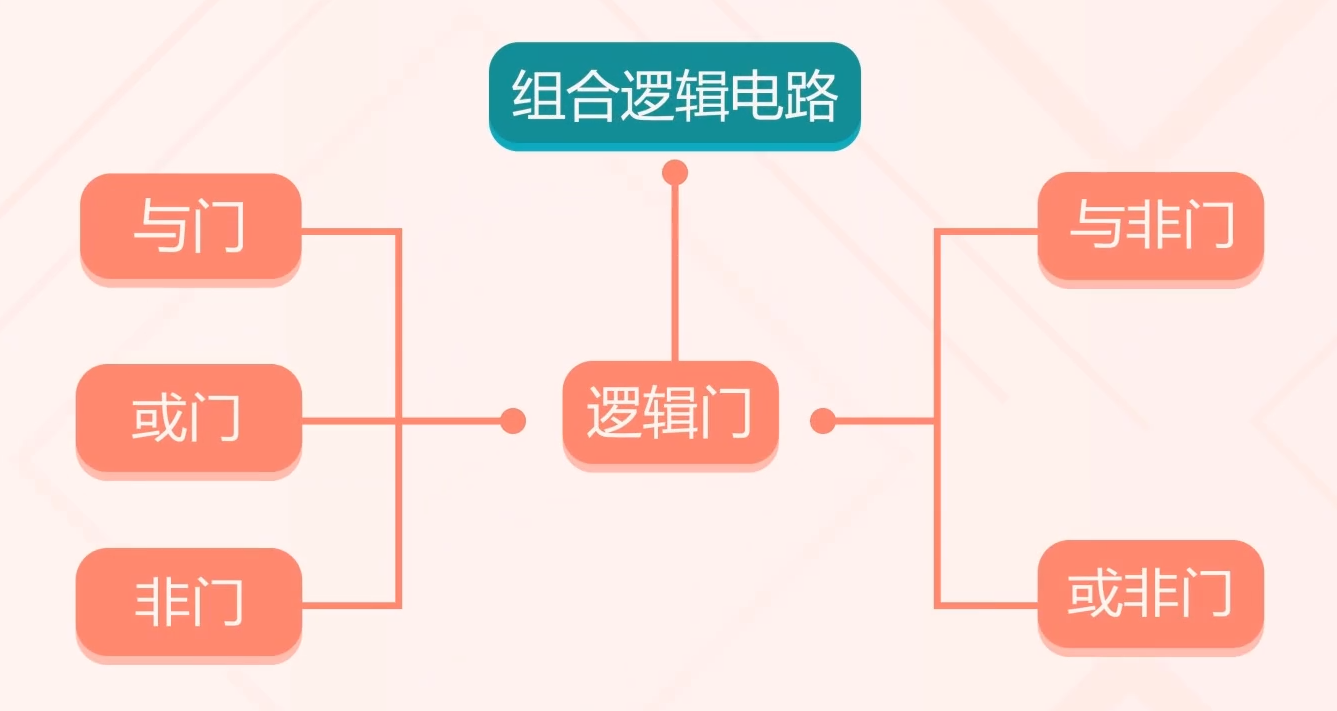

組合邏輯電路由邏輯門構成,所以先介紹幾種簡單的門電路以便于大家理解。邏輯門可以分為與門、或門、非門、與非門和或非門等多種邏輯門。

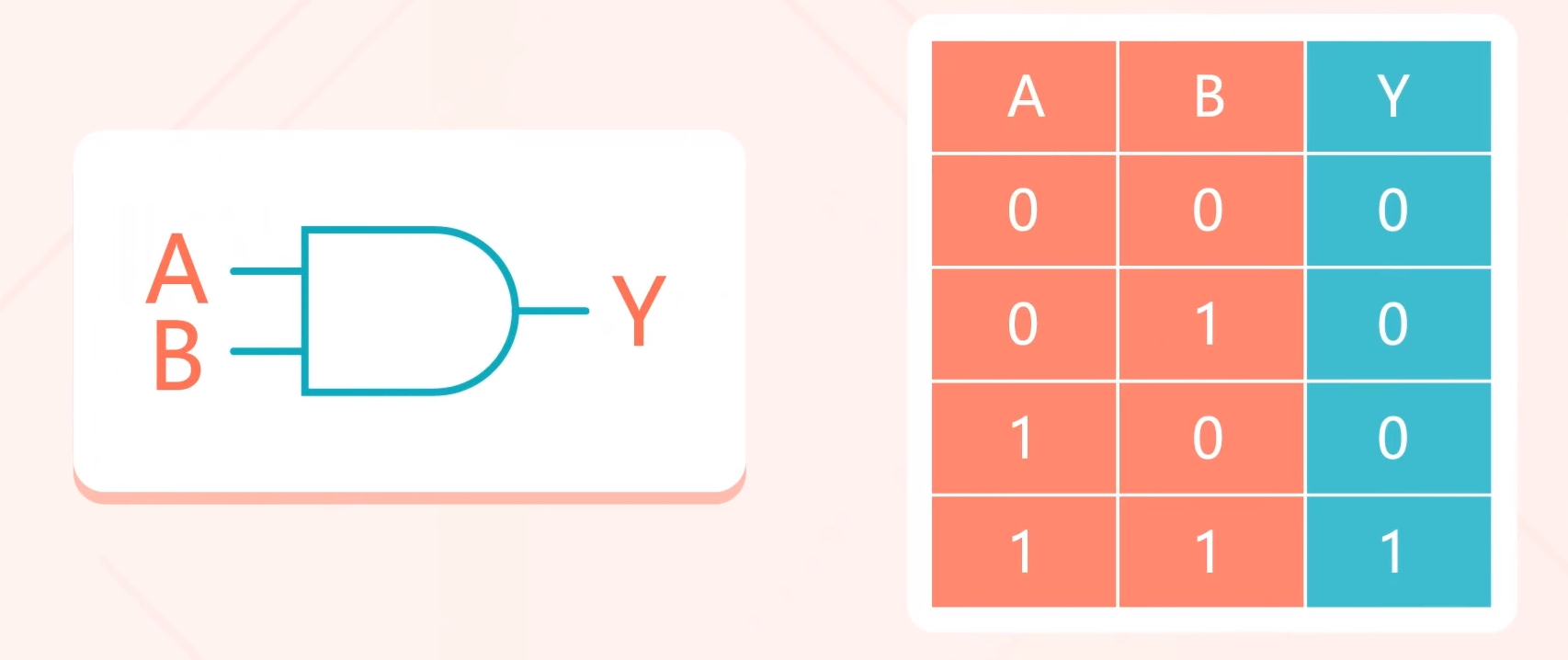

與門的符號表示如下圖所示,將A、B作為與門的兩個輸入,Y作為輸出。就可以寫出它的真值表。(真值表通俗來說就是將各種輸入信號狀態與對應的輸出信號匯聚到一張表格中。它有很更重要的作用,但這里就不展開說明了。)

其含義是:只有輸入A、B均是1,輸出Y才是1。

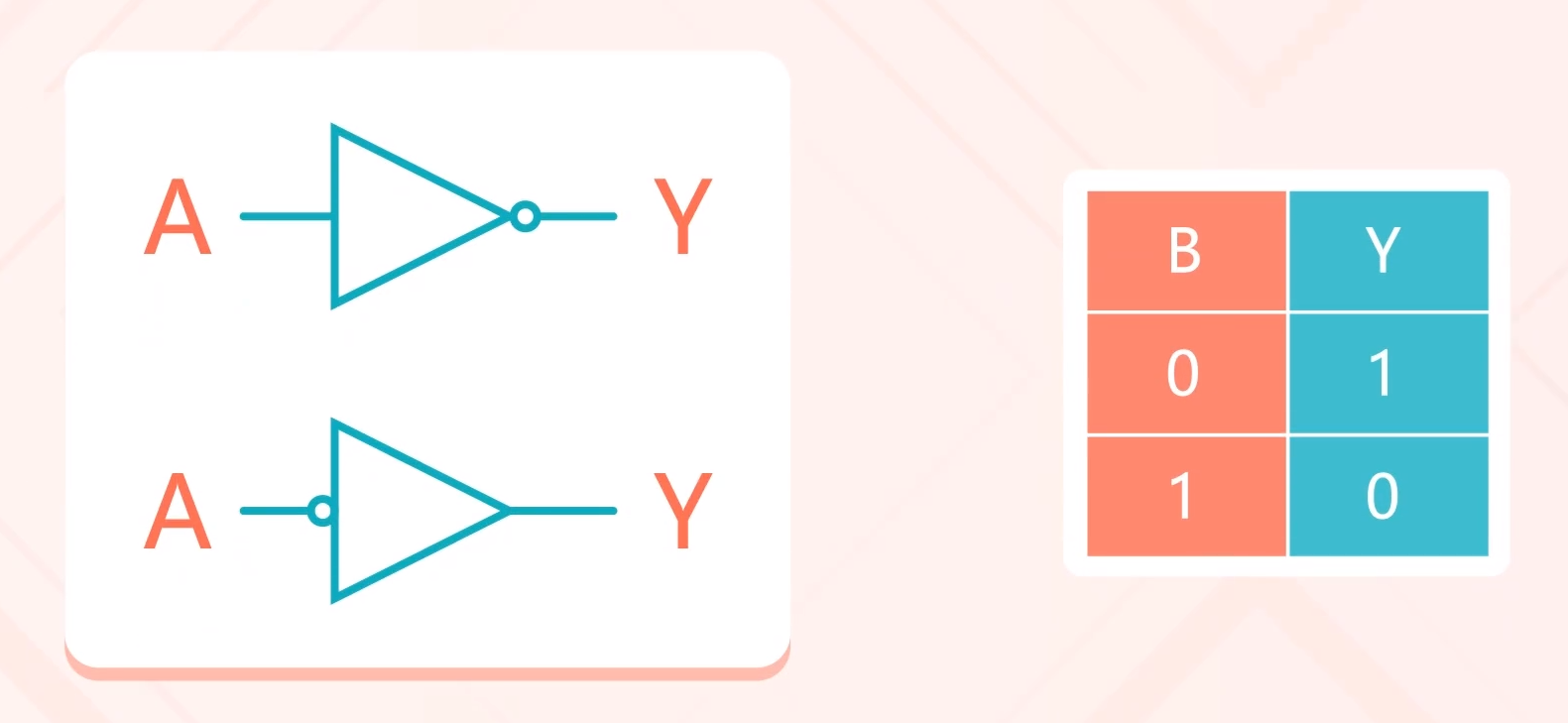

非門的符號及其真值表如下圖所示。

其含義是:對輸入狀態取反。

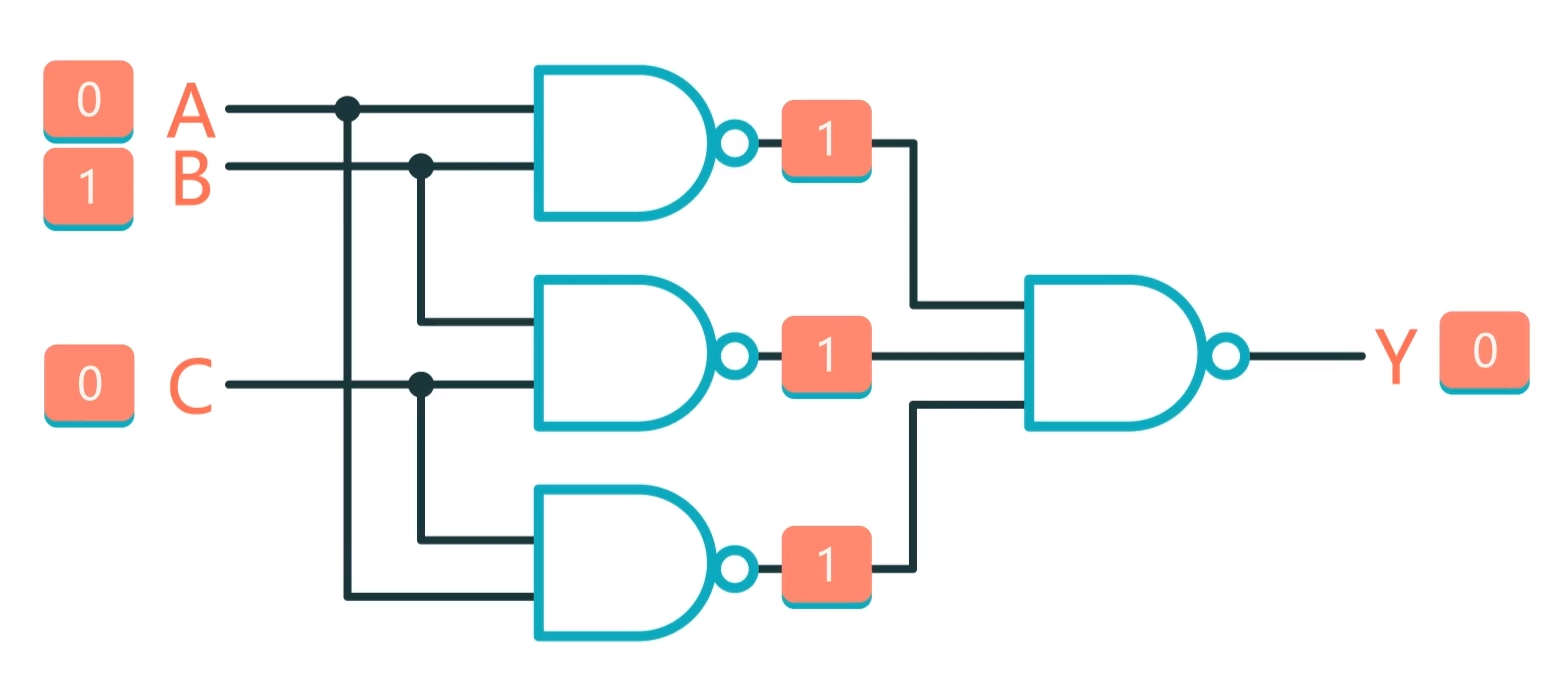

接下來我們就可以用這兩種邏輯門構建一個組合邏輯電路。如下圖所示:(圖像中的符號其實就是與門和非門的結合,非門被簡化為一個小圓圈,這樣的畫法也可以延伸到其他的電路圖像中。)

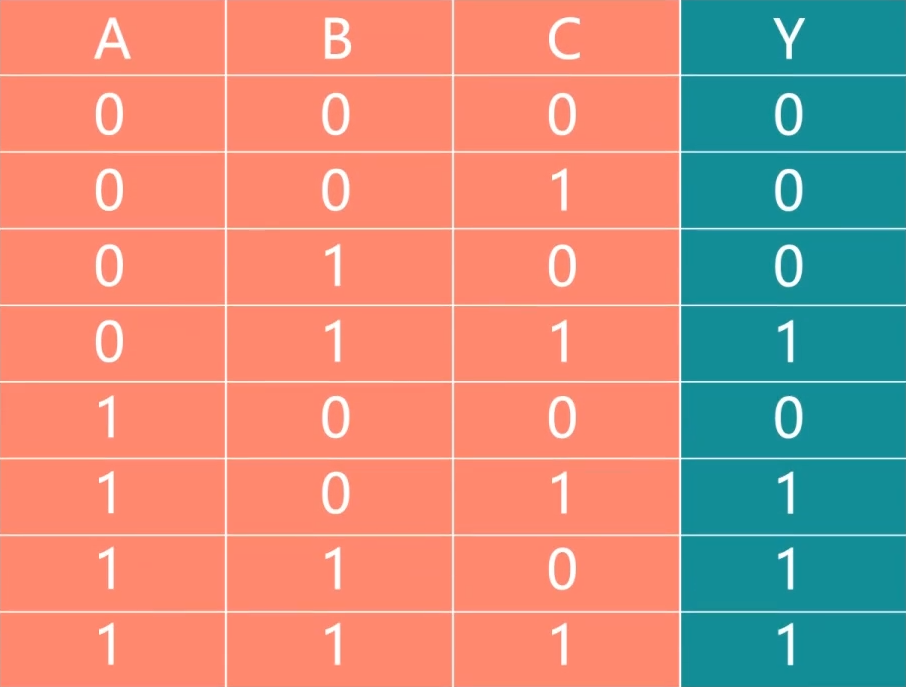

假設將A、B、C置為0、1、0。經過與非門(與門加非門)后輸出1、1、1,再經過一個與非門后,輸出Y=0。遍歷輸入信號的所有可能,就可以列出此電路的真值表。

通過真值表可以看出,當輸入A、B、C中只有一個1或沒有1時,Y輸出0。當輸入有兩個或兩個以上的1時,Y輸出1。這就是將這個電路稱為判決電路的原因。在這個電路中,A、B、C三個輸入經過4個與非門后得到了輸出Y。整個電路從左至右依次進行,沒有輸出回流到某一級的輸入中,也就是沒有反饋。所以我們可以說,在這個電路中,任一時刻的輸出狀態只決定于該時刻各輸入狀態的組合,而與電路的原狀態無關。像這樣的電路就是組合邏輯電路,其中沒有記憶單元,沒有反饋電路。

這也是組合邏輯電路與時序邏輯電路的主要區別。下面為大家列舉兩個常見的較為復雜的組合邏輯電路。

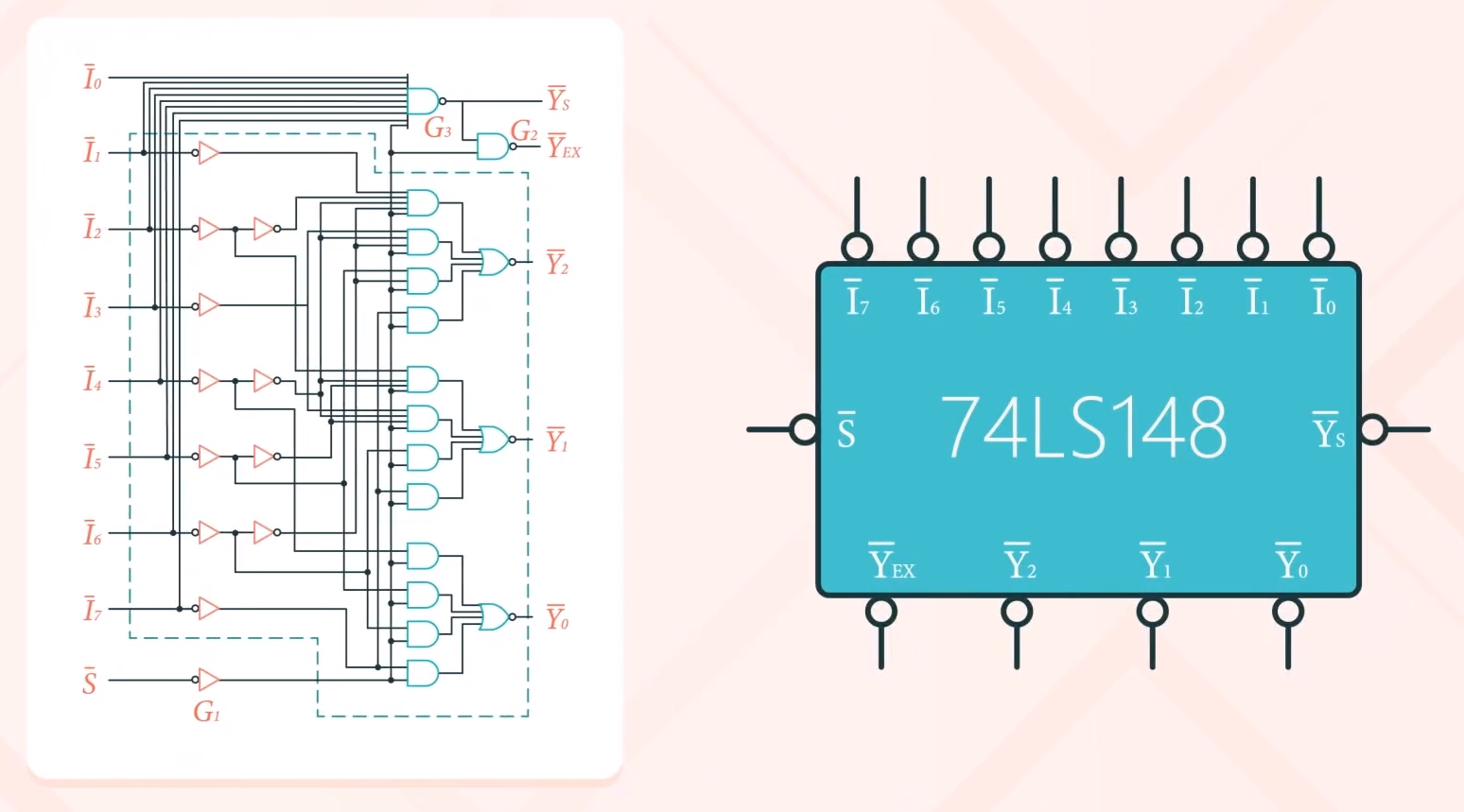

編碼器電路,在數字電路中用二進制代碼表示有關的信號稱為二進制編碼。實現編碼操作的電路就是編碼器。如圖所示是一個8線-3線優先編碼器(74LS148),及其符號表示。

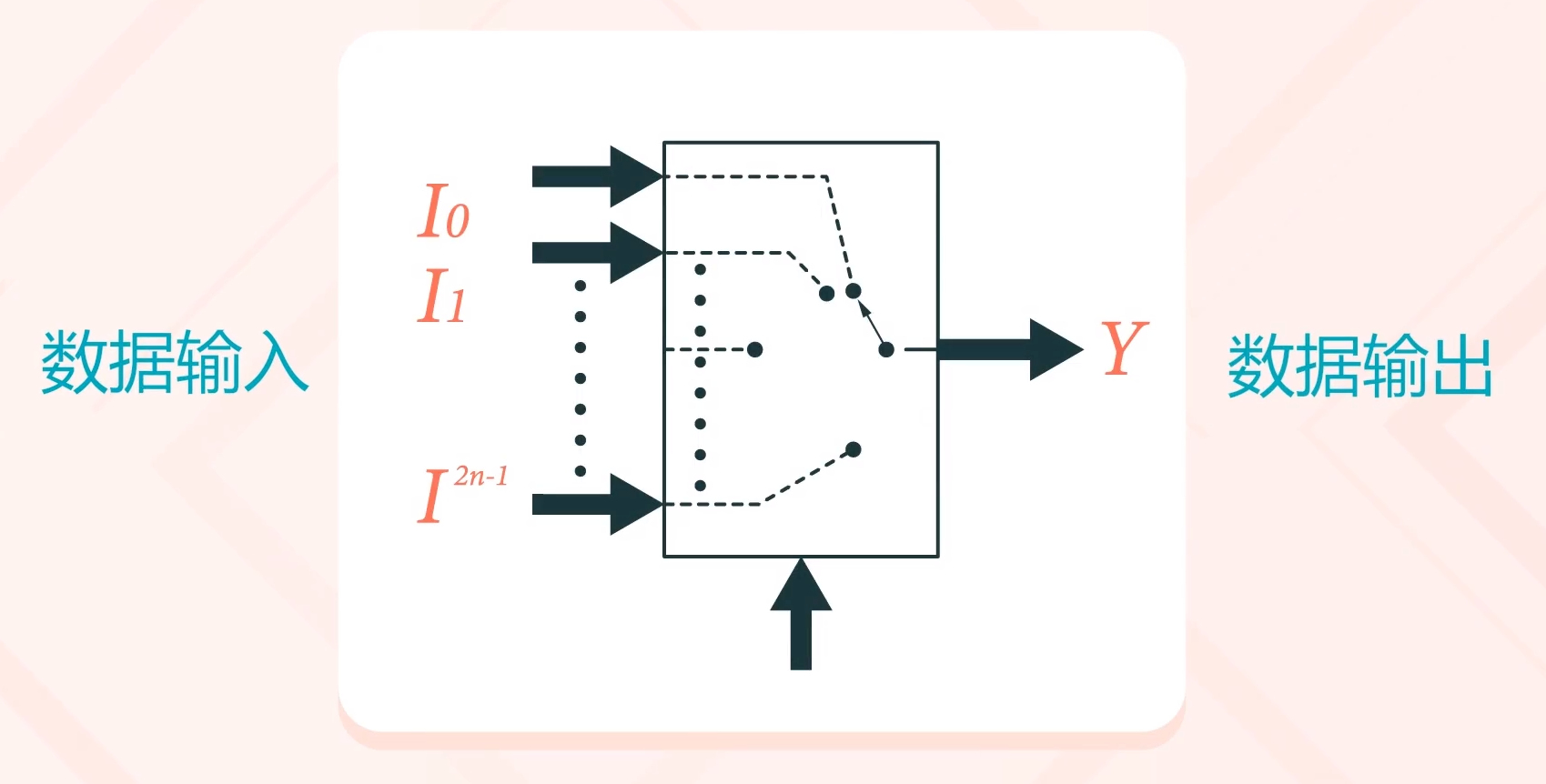

數據選擇器又稱多路選擇器(MUX)。每次在地址輸入的控制下,從多路輸入數據中選擇一路輸出。

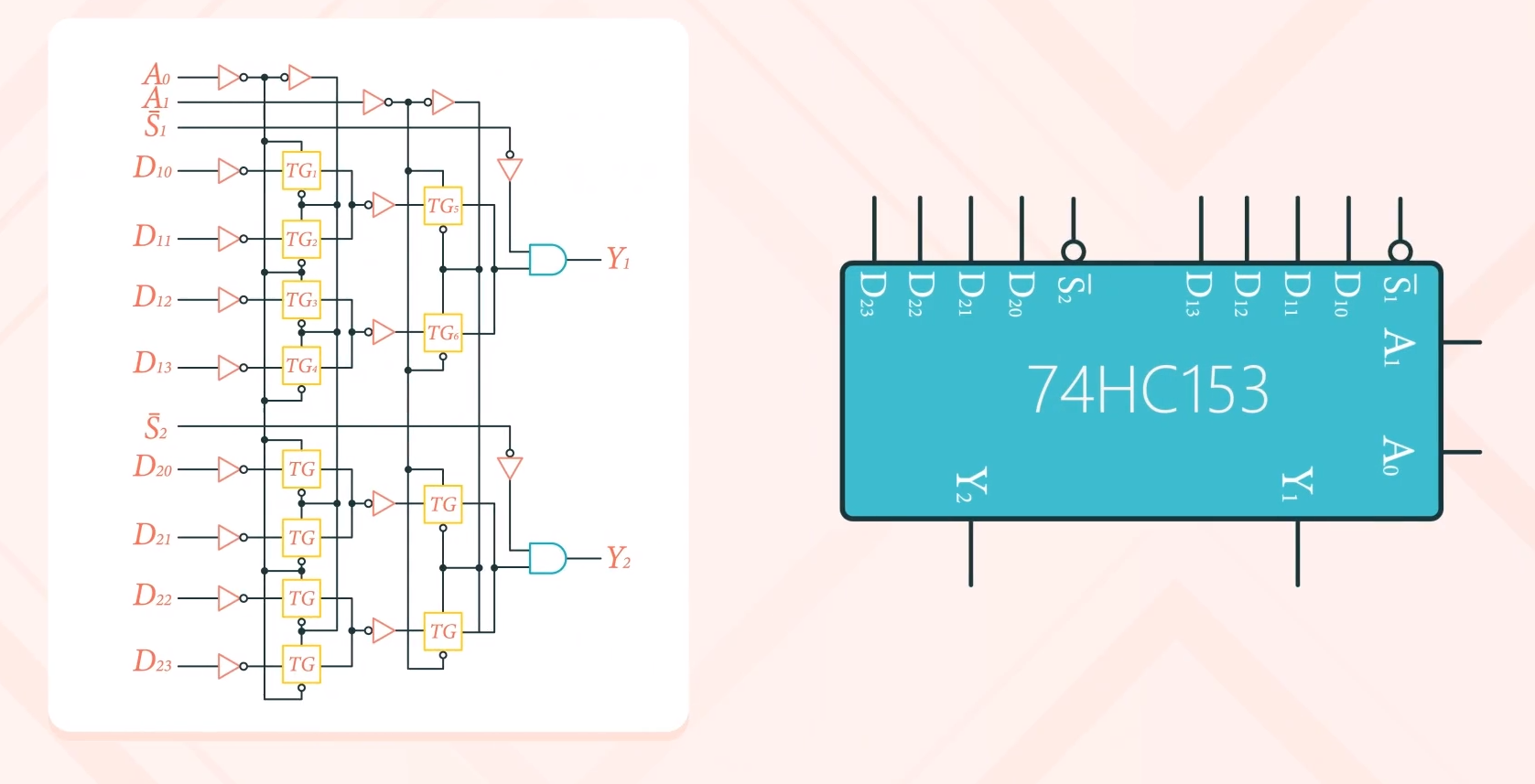

這是一個集成雙4選1數據選擇器74HC153及其符號表示。

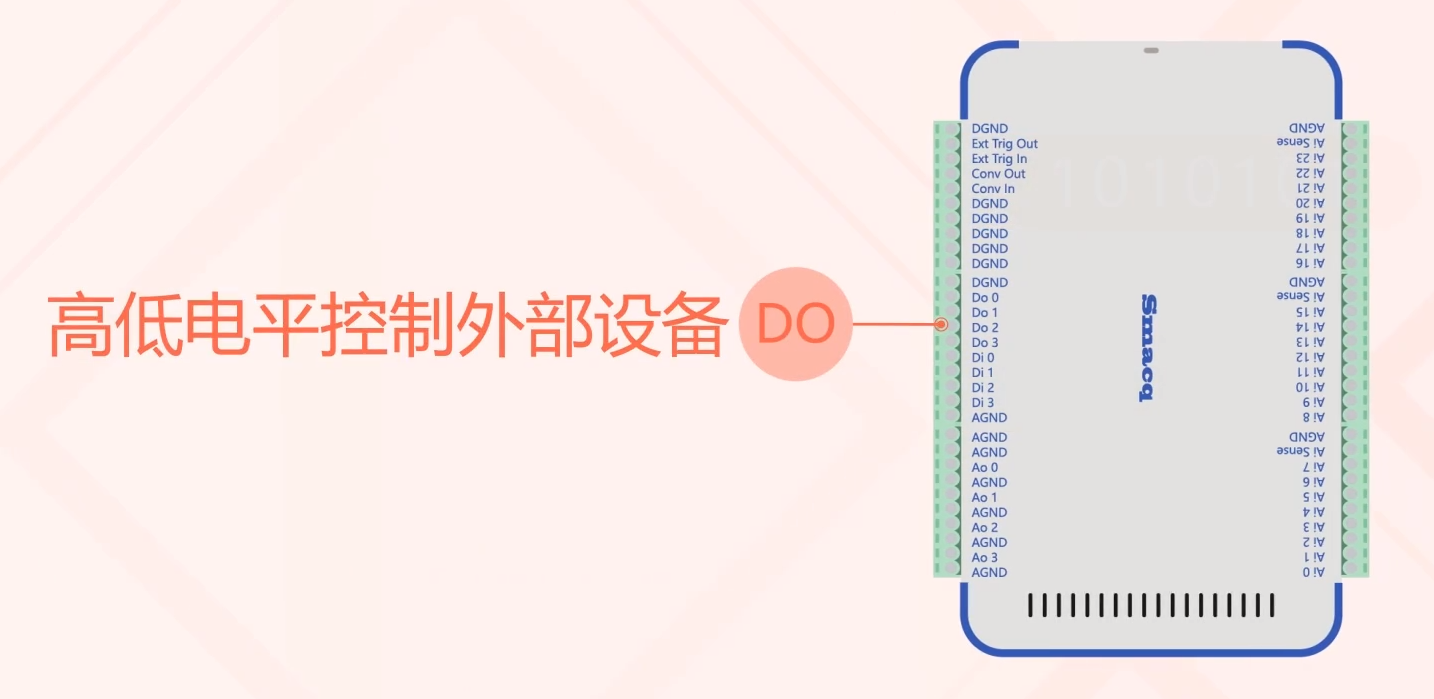

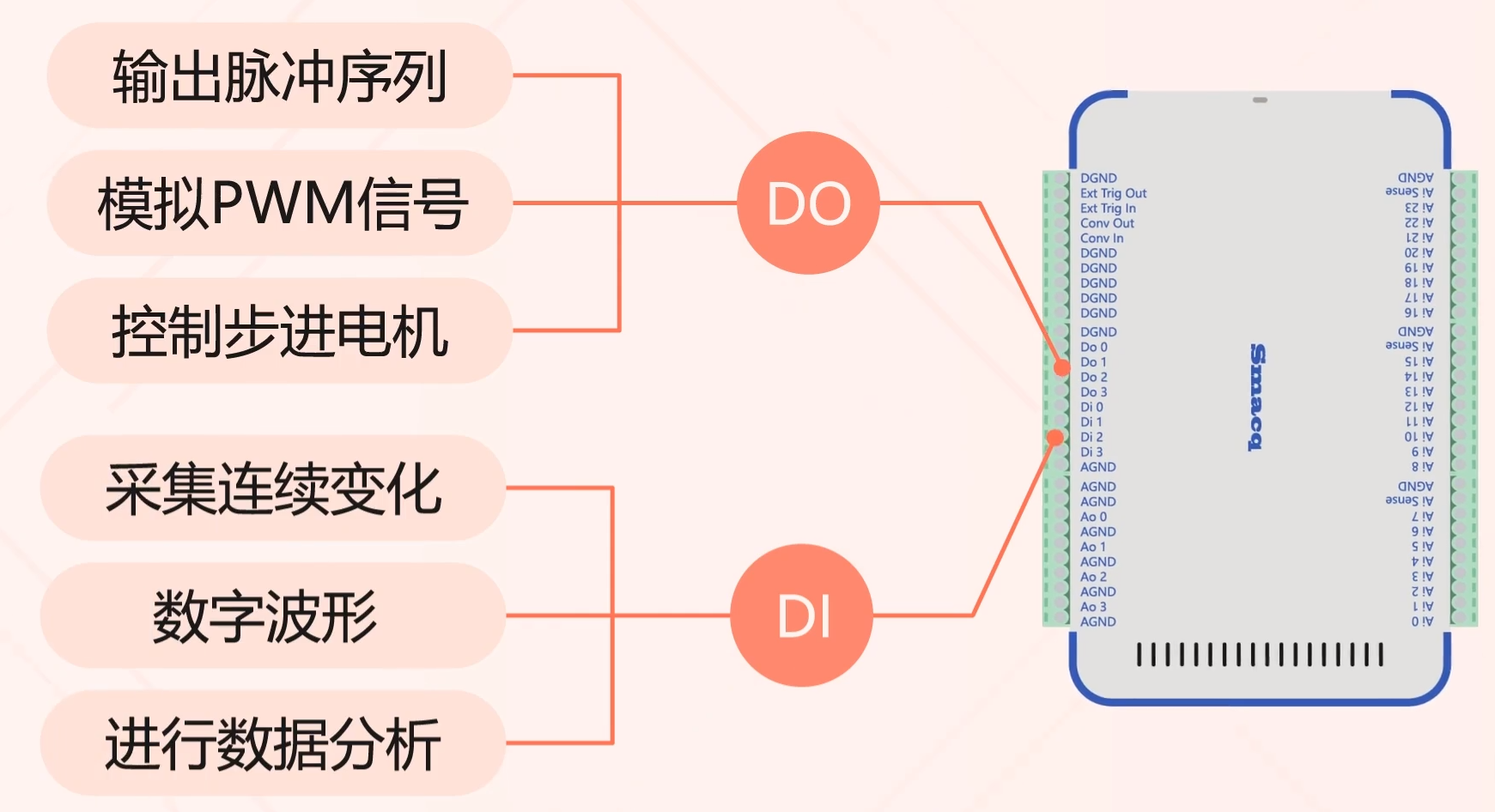

雖然這些電路執行的邏輯運算很復雜,但是最終也是以高低電平的形式輸出,那么使用采集卡的DI端口就可以檢測它們的狀態。依托計算機強大的計算能力,可以進行復雜的數字運算。

運算結果由DO輸出相應的高低電平,從而控制外部設備。

當然,這些I/O端口也可以發出一串脈沖信號,這就與時序邏輯電路有關了。

2、時序邏輯電路

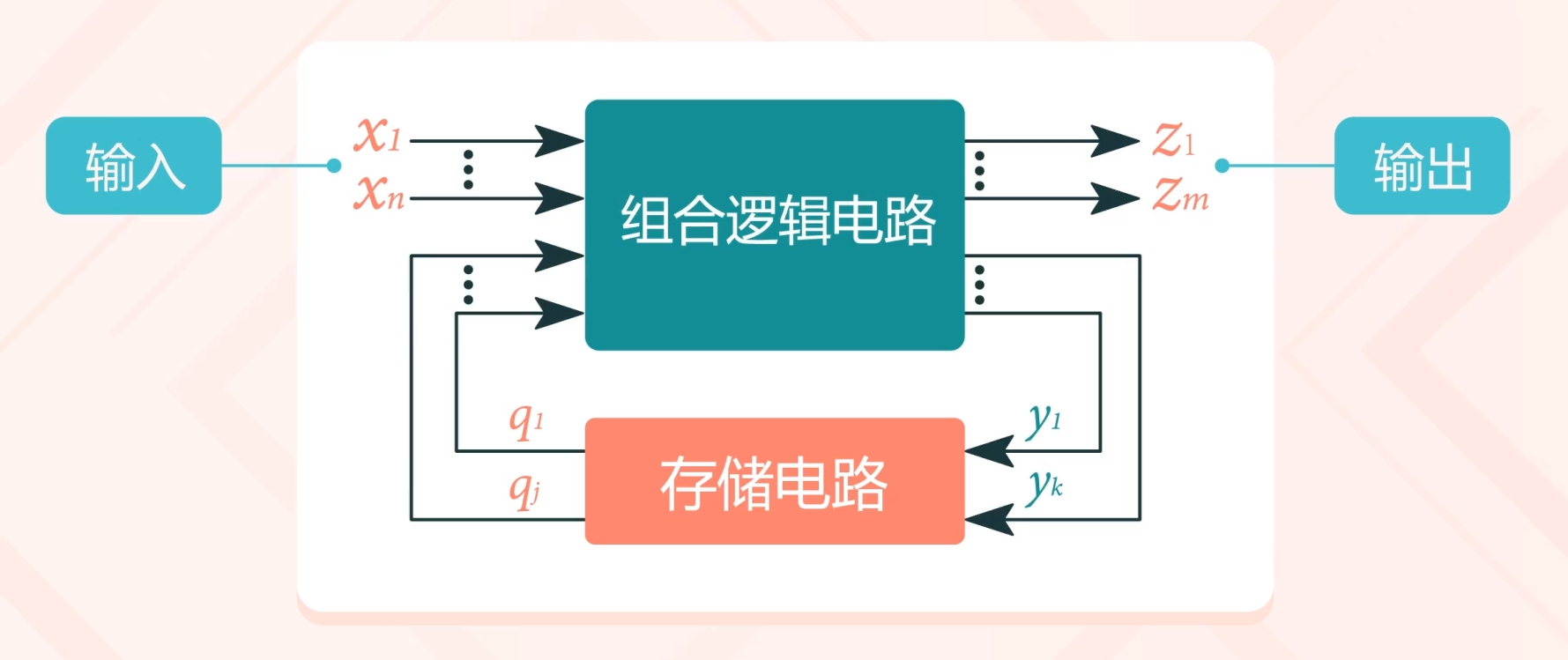

時序邏輯電路的特點是任一時刻的輸出信號不僅取決于該時刻的輸入信號,而且還取決于電路原來的狀態。它由組合邏輯電路和存儲電路組成。

組合邏輯電路與我們之前介紹的一致。而存儲電路實質上是由觸發器構成。所以我們先來看看觸發器是怎樣工作的。

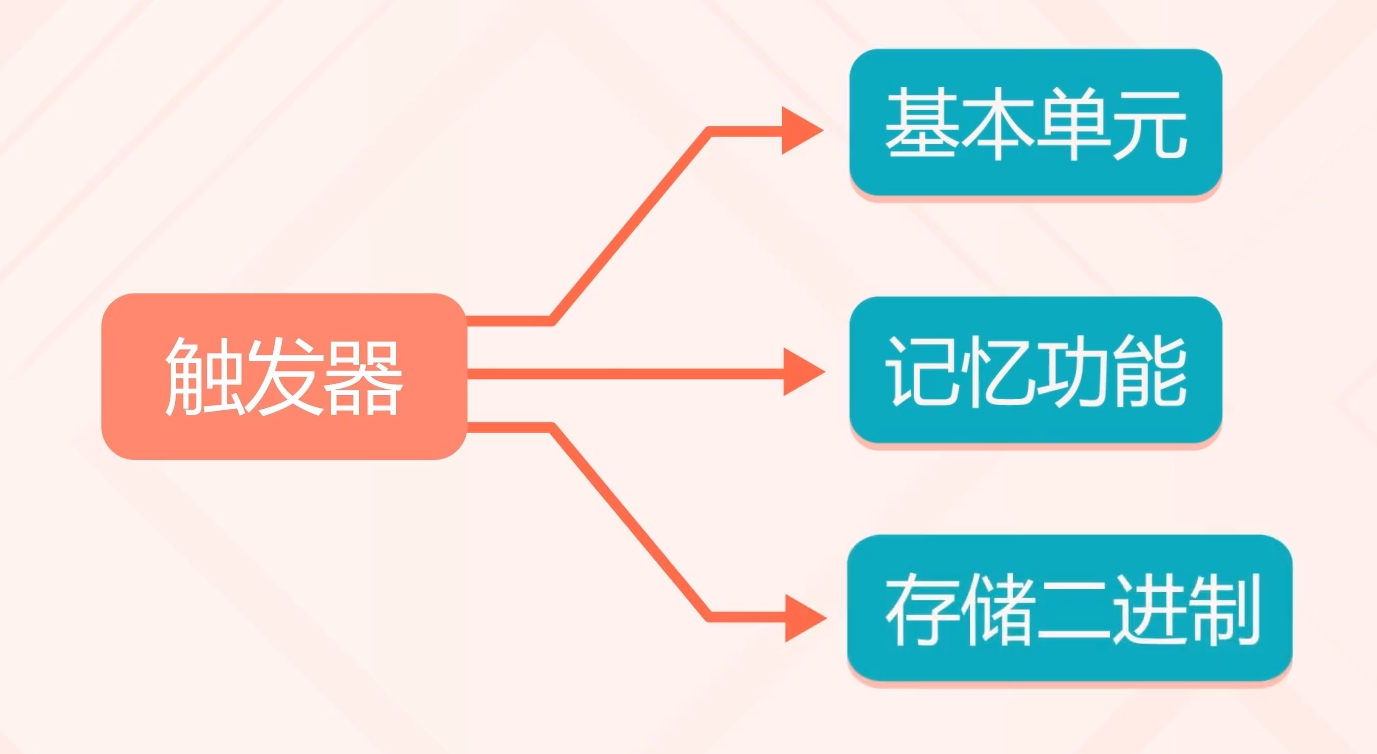

觸發器是構成時序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進制信息的邏輯電路。

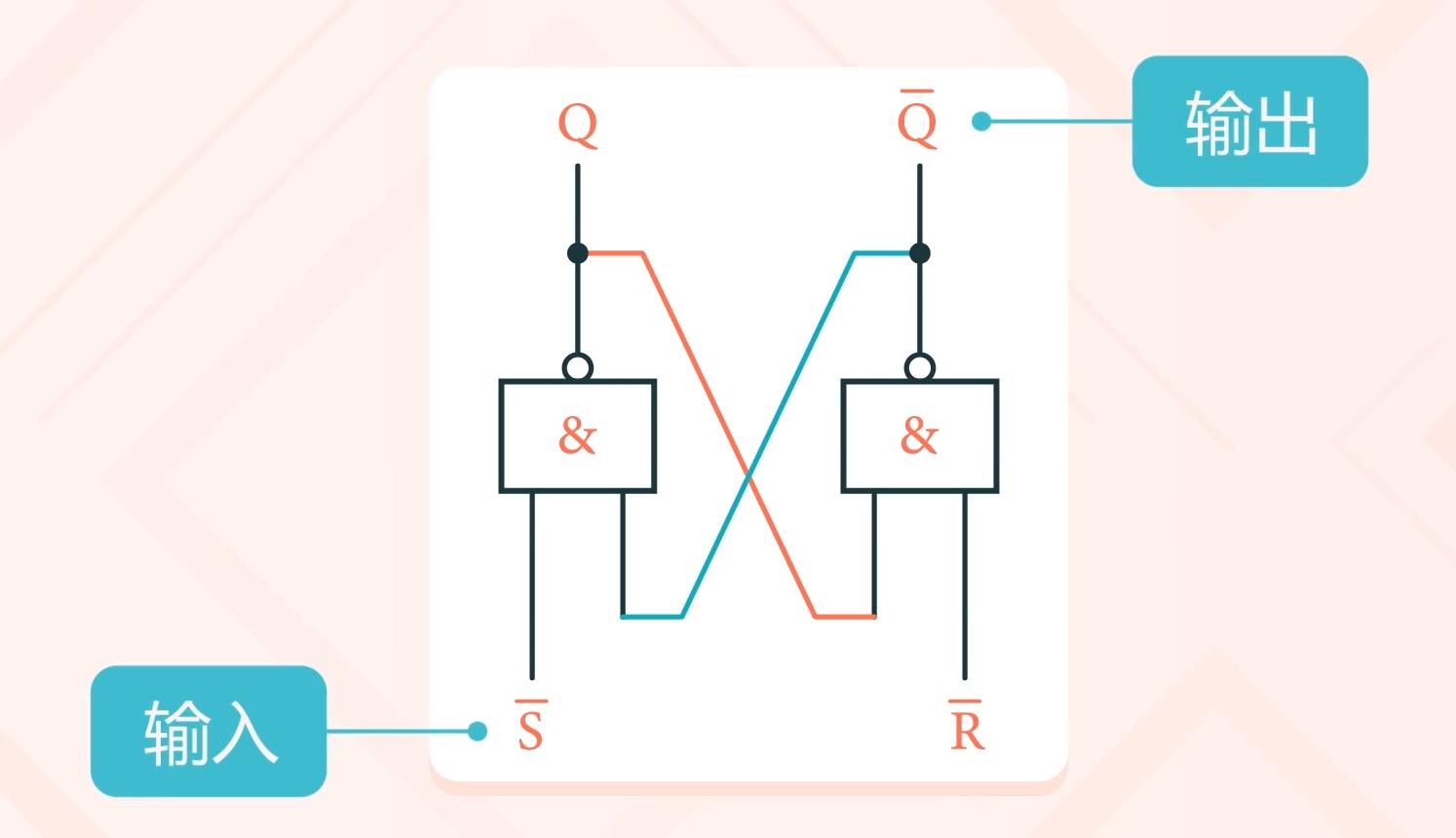

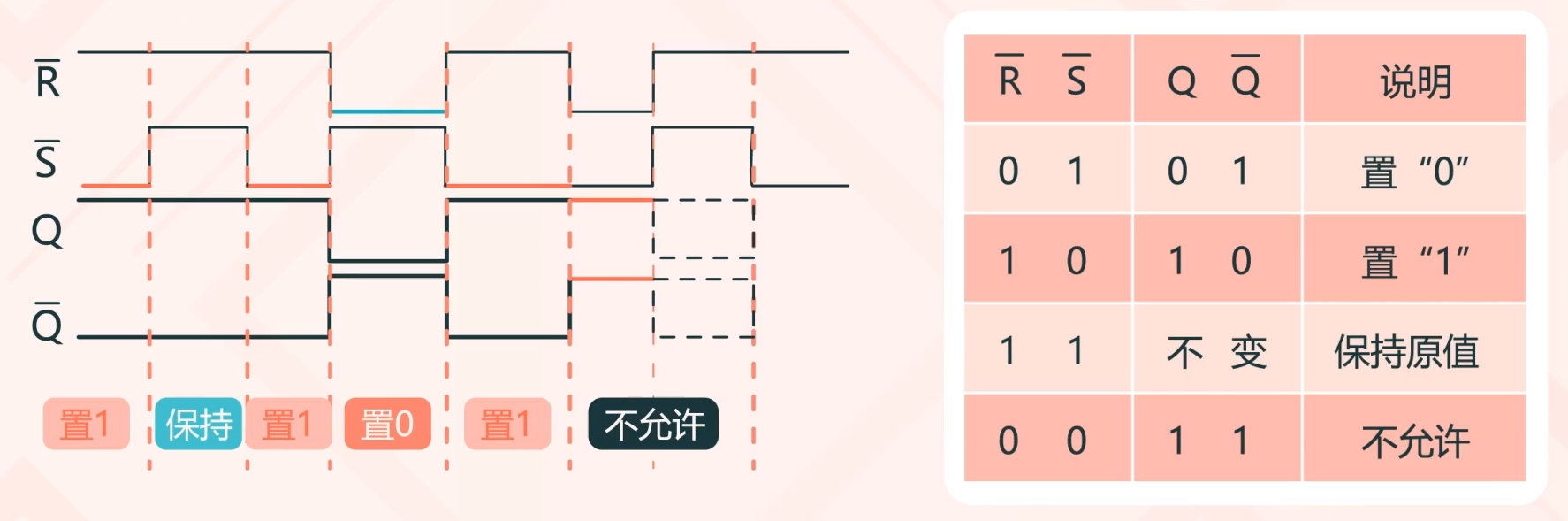

這里介紹一種基本RS觸發器。它的電路結構如下圖:

可以看出,與非門的輸出(“&”表示與)被傳送到了另一個與非門的輸入中,這就是電路中所說的反饋。它的工作流程依照我們分析組合邏輯電路時的分析方法就可以。當R(非)=1,S(非)=0,Q置1;當R(非)=0,S(非)=1,Q與Q(非)保持之前狀態不變;當R(非)=0,S(非)=1,Q置0。

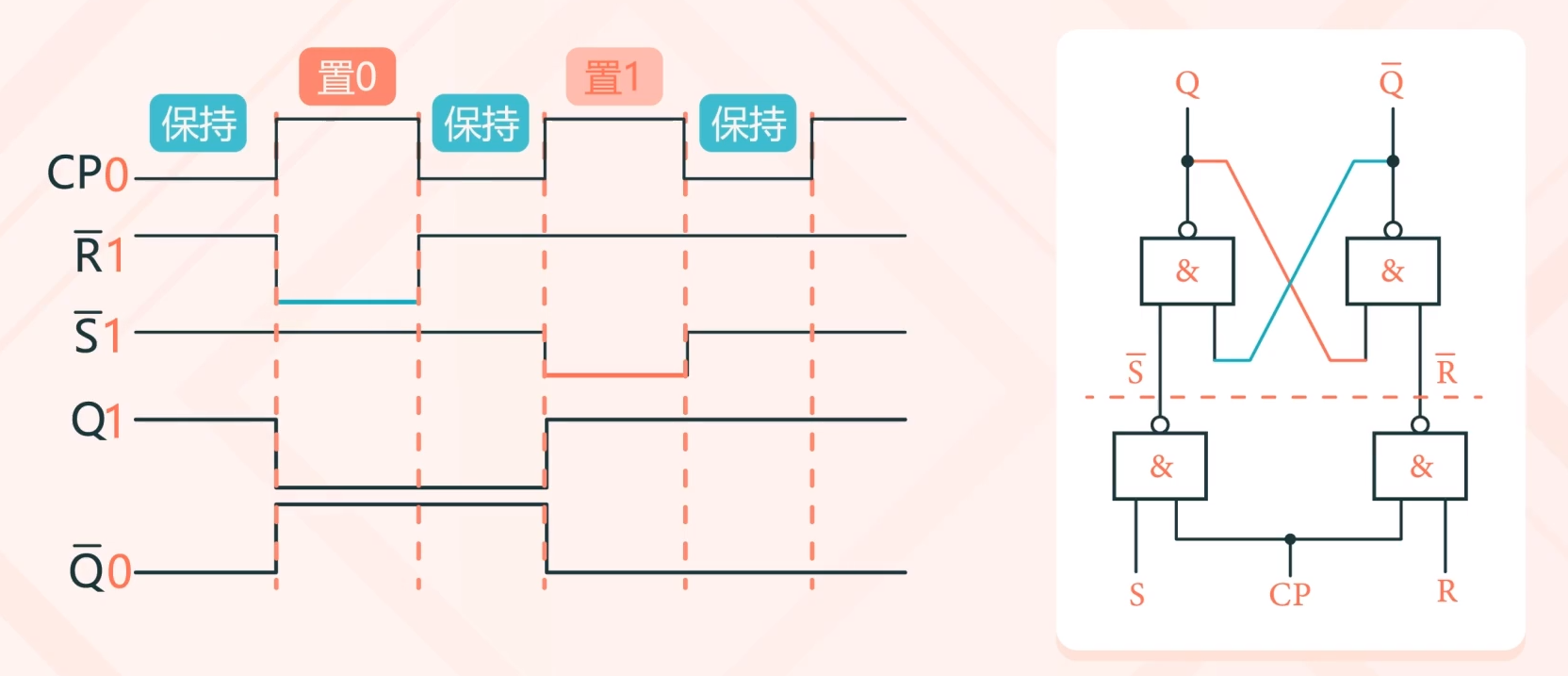

如果我們在電路中增加了一個同步信號也叫做時鐘信號(CP)時,就可以得到這樣的電路及時序圖:

當CP=0時,S(非)=R(非)=1,觸發器保持原來狀態不變。當CP=1時,工作情況與基本RS觸發器相同。

同組合邏輯電路一樣,由基本的RS觸發器可以構成很多復雜的觸發器以及由它們產生的各種時序邏輯電路。這些內容就不再為大家列舉了。那么時序邏輯電路又能完成什么樣的工作呢?

四、總線

我們都知道,計算機自身是不會產生信息的,需要通過鼠標、鍵盤等設備向計算機傳遞消息。這些設備所使用的總線協議就和時序邏輯電路息息相關了。

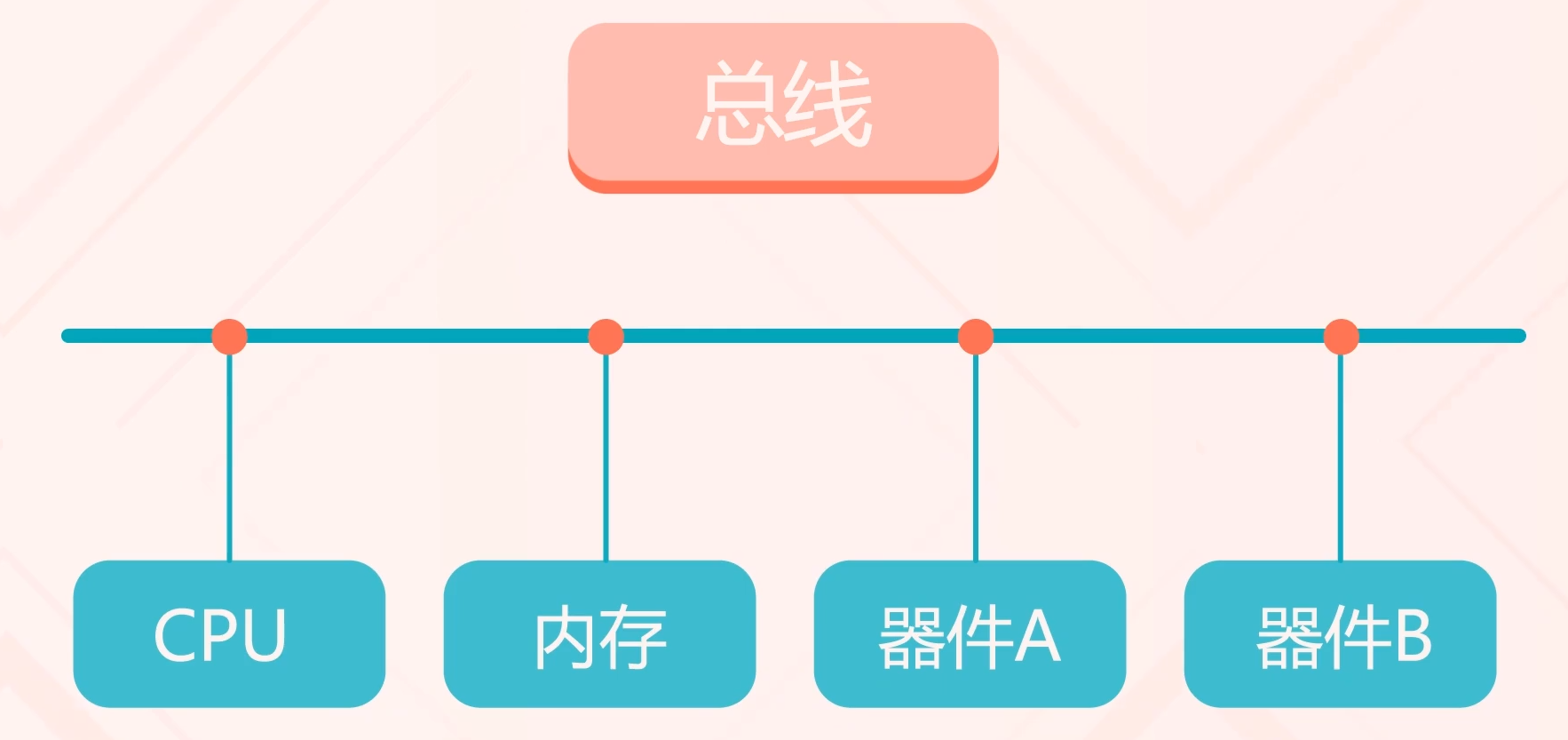

不過總線又是什么呢?

簡單來說,總線就是連接計算機各個功能模塊的一條通信主干線。只要器件間想要建立連接,就要通過這條線路。

當器件A與器件B通訊后,其他器件想要通訊就只能等待A與B通訊完成或是打斷它們之間的通信。下面我們就為大家介紹幾種常見的總線。

1、USB總線

USB總線是英文Universal Serial Bus(通用串行總線)的縮寫,用于規范電腦與外部設備的連接和通訊。它已經成為大量計算機和智能設備的標準擴展接口和必備接口之一。

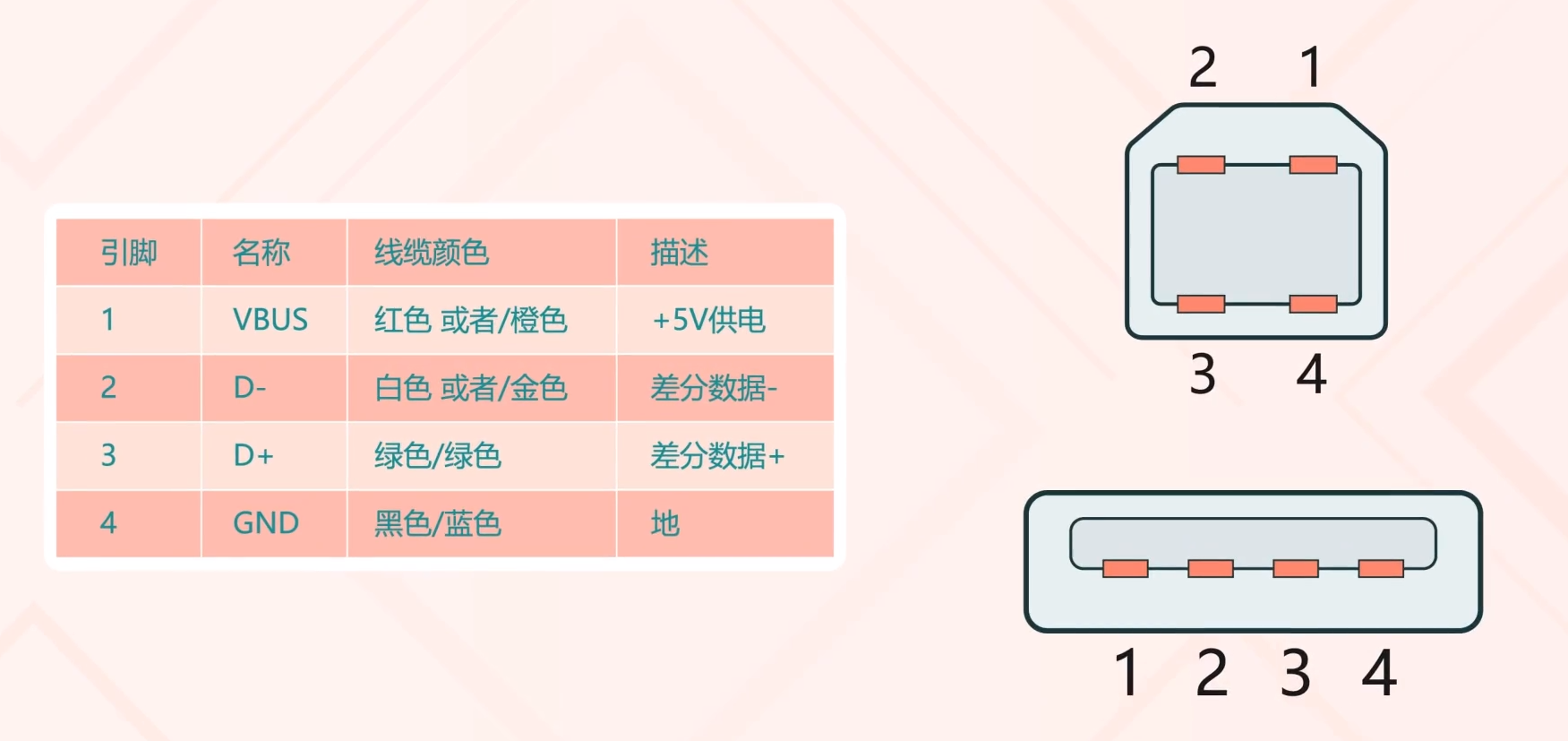

其引腳定義如圖:

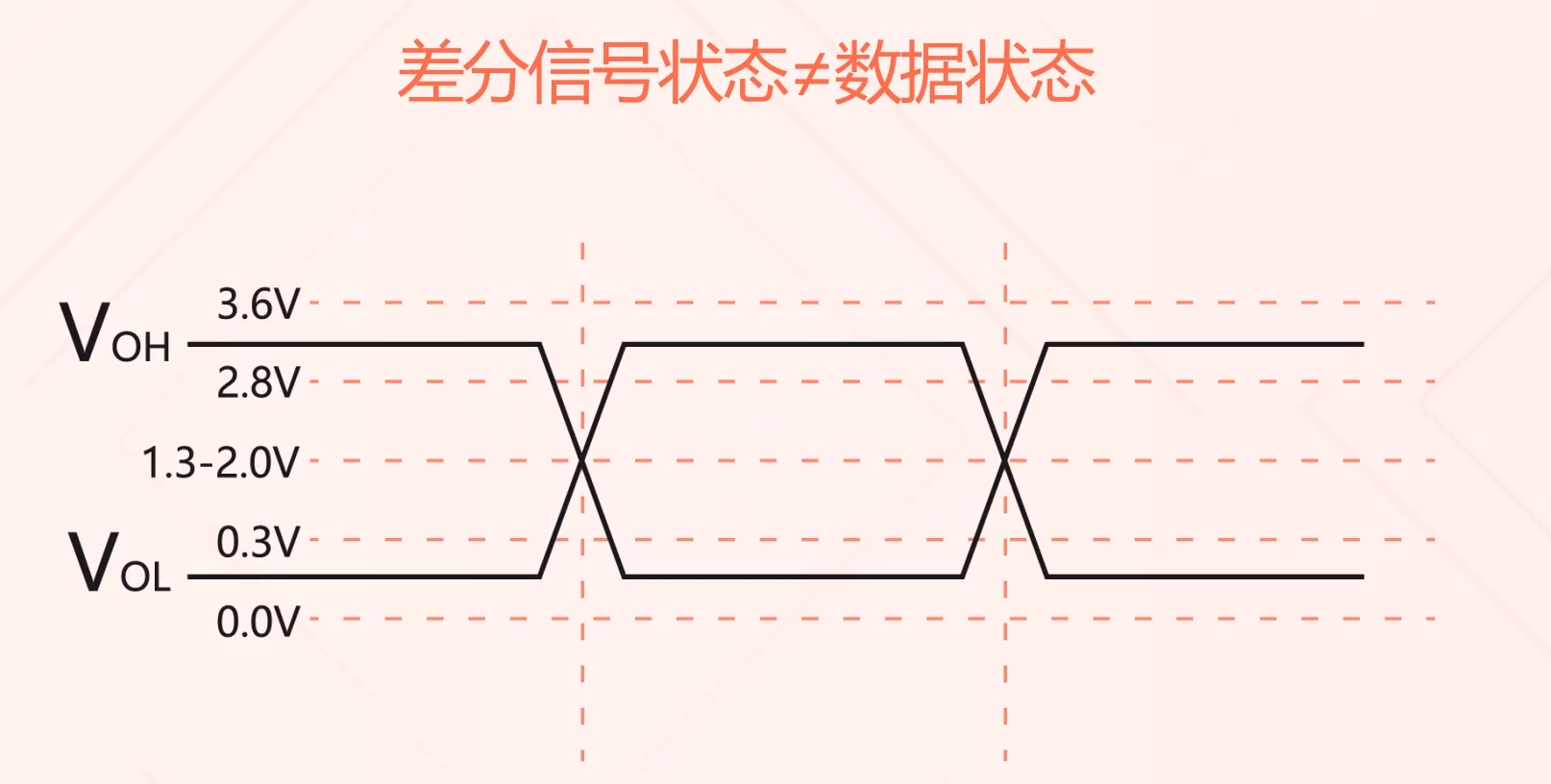

USB是一種異步串行總線。它傳輸數據主要依靠兩根差分模式傳輸的信號線D+和D-。

主機發送或接受的信息均由這兩根數據線傳輸,而且差分信號狀態并不直接代表數據狀態。因為USB使用的是NRZI編碼方式,這種編碼方式較為復雜,我們之后有機會在為大家介紹。總之,USB總線通過一些列的協議標準,使總線上的設備能夠完成通信。

2、232總線

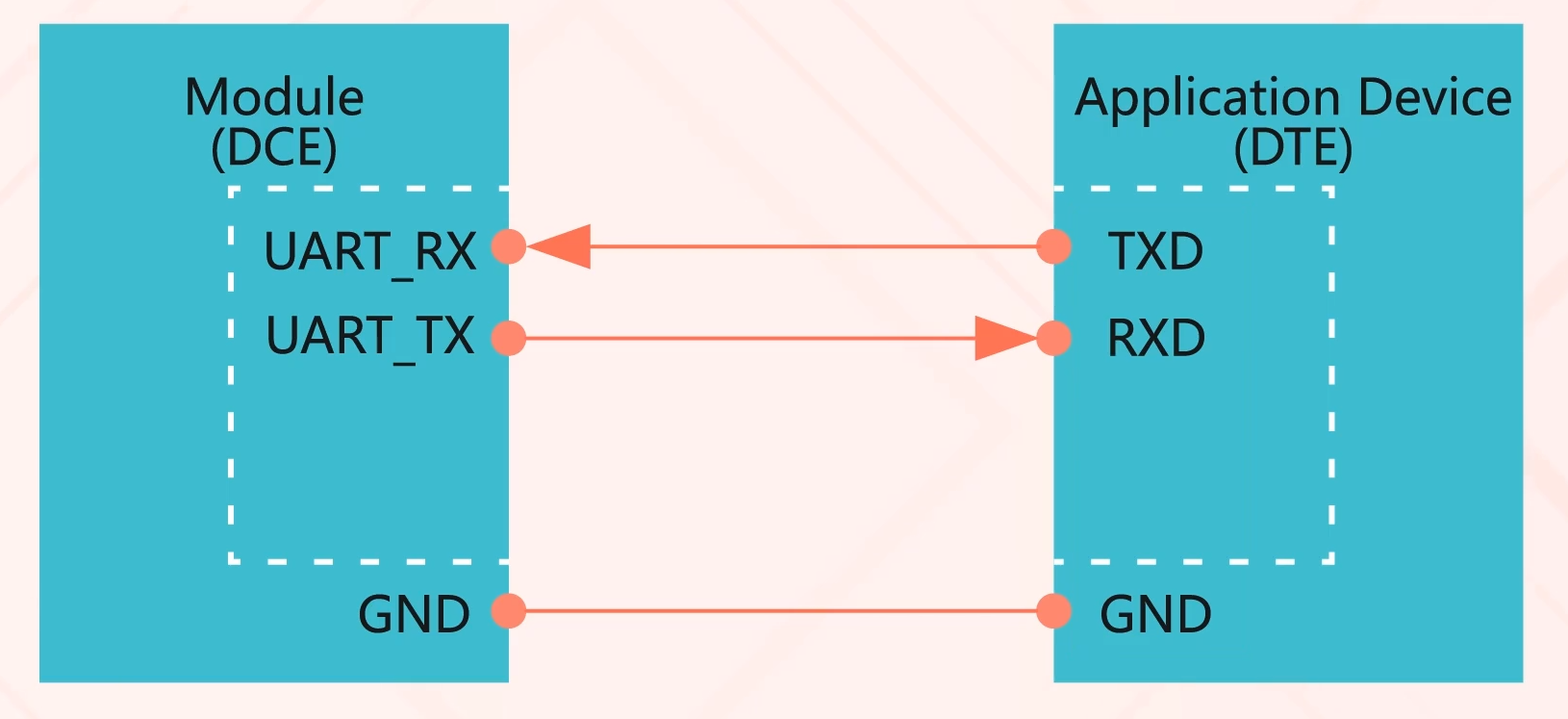

工業設備則大量使用232總線,它是常用的串行通信接口標準之一,其全名是“數據終端設備(DTE)和數據通信設備(DCE)之間串行二進制數據交換接口技術標準”。

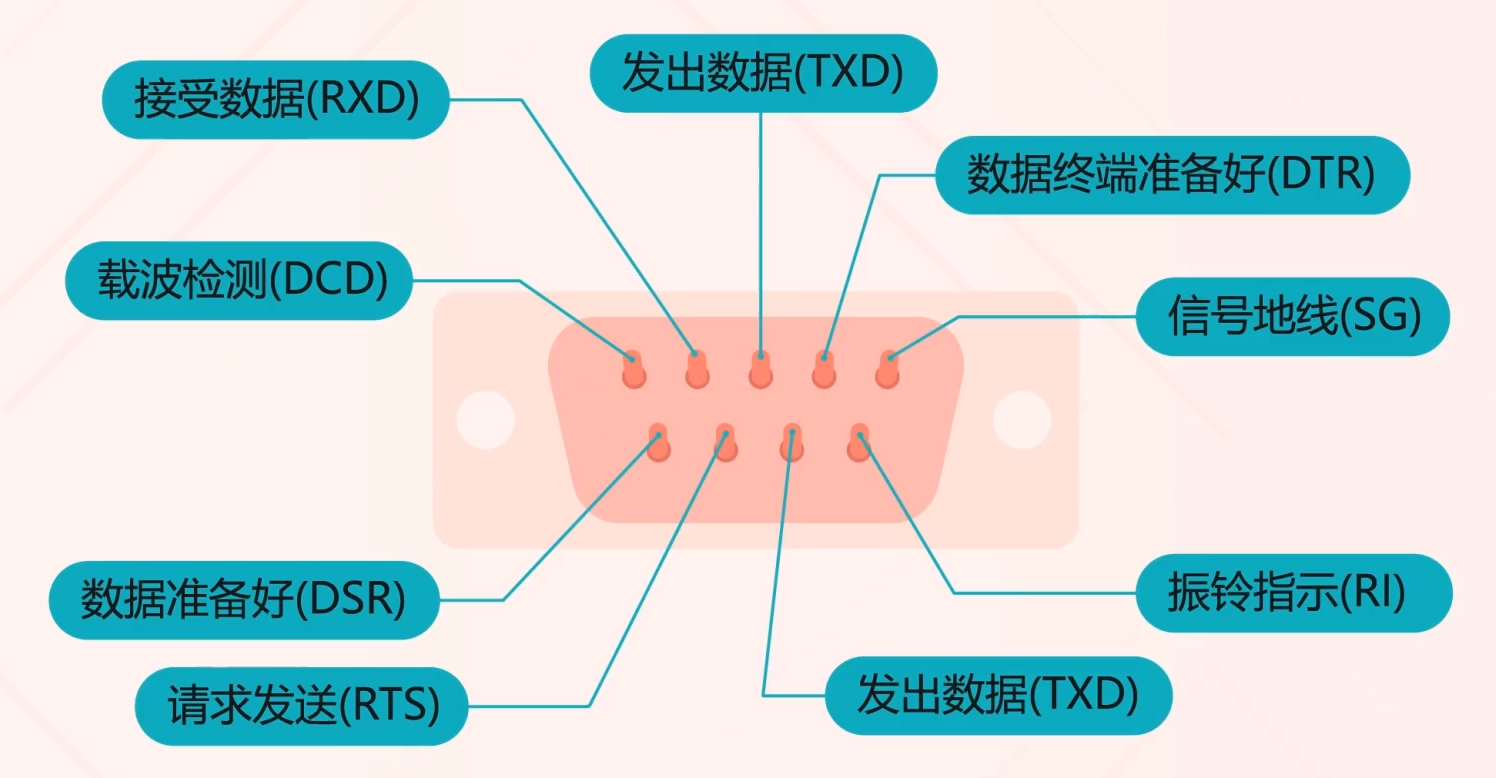

先來看看它的接口形態,公頭是帶有針腳的一端,母頭是帶有孔座的一端。

各引腳的定義如下圖所示:

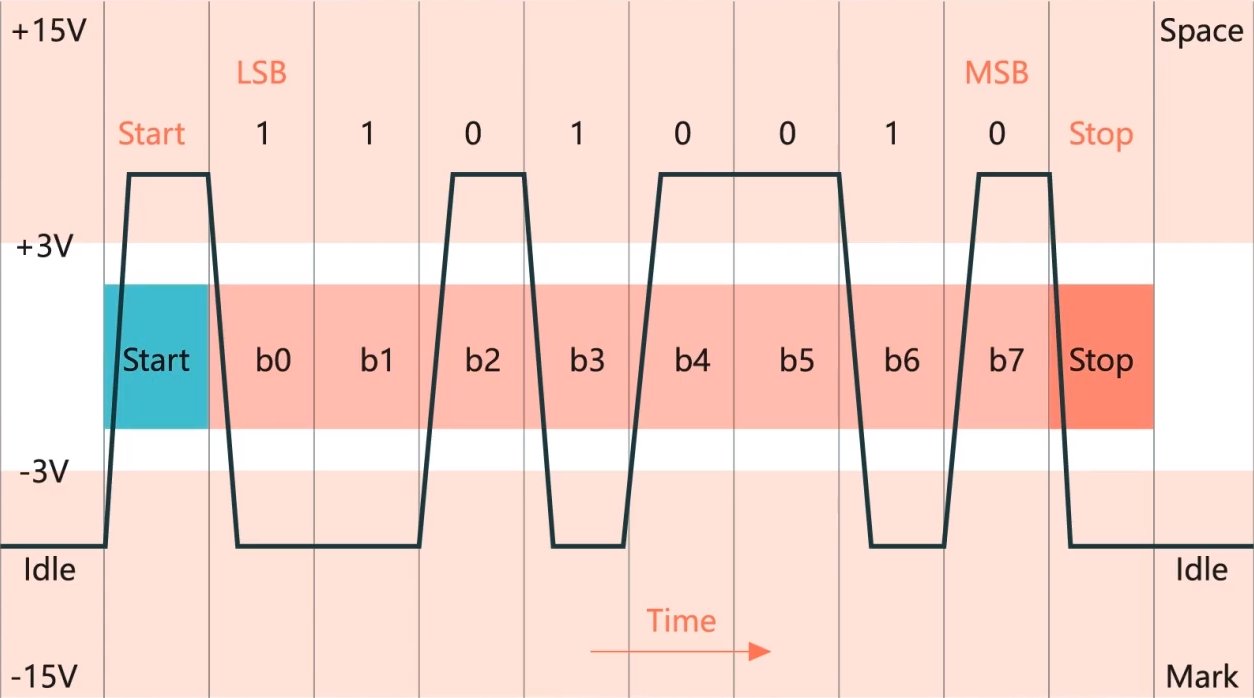

我們按照UART串口協議傳輸0100 1011。便可得到如下時序圖:

起始與停止位各占一位,數據以負邏輯,由高位到低位發送。在時序圖中大家可以看到,高電平的電壓比較高,可達15V。與TTL電平不兼容,不能直接連接到TTL電路上,而且232總線只能進行點對點的通信,很不方便。所以在RS-232的基礎上又發展出了許多種通信接口,RS-485就是其中之一,它被廣泛用于數據采集和控制應用中。

3、RS-485總線

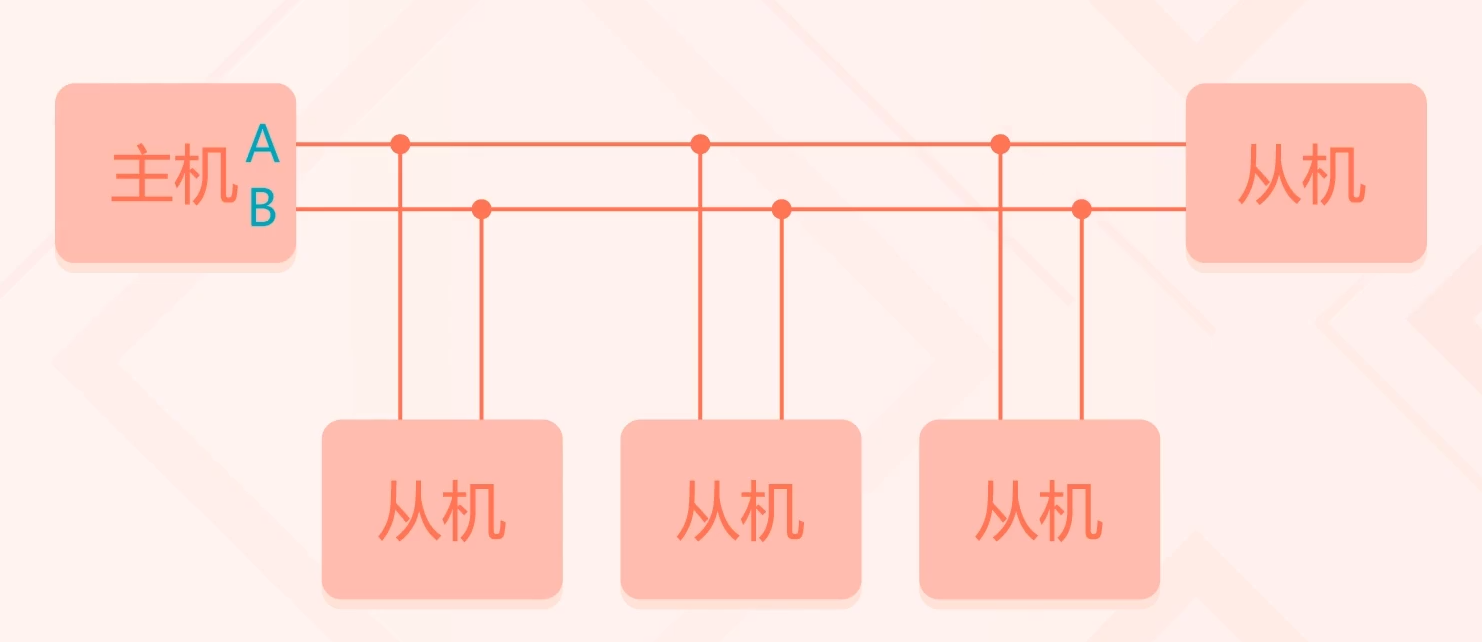

RS-485總線使用差分模式傳輸數據(A、B總線),有較強的抗干擾能力。同時傳輸距離長,可達1200米。并且在A、B總線上可以掛載多個設備。

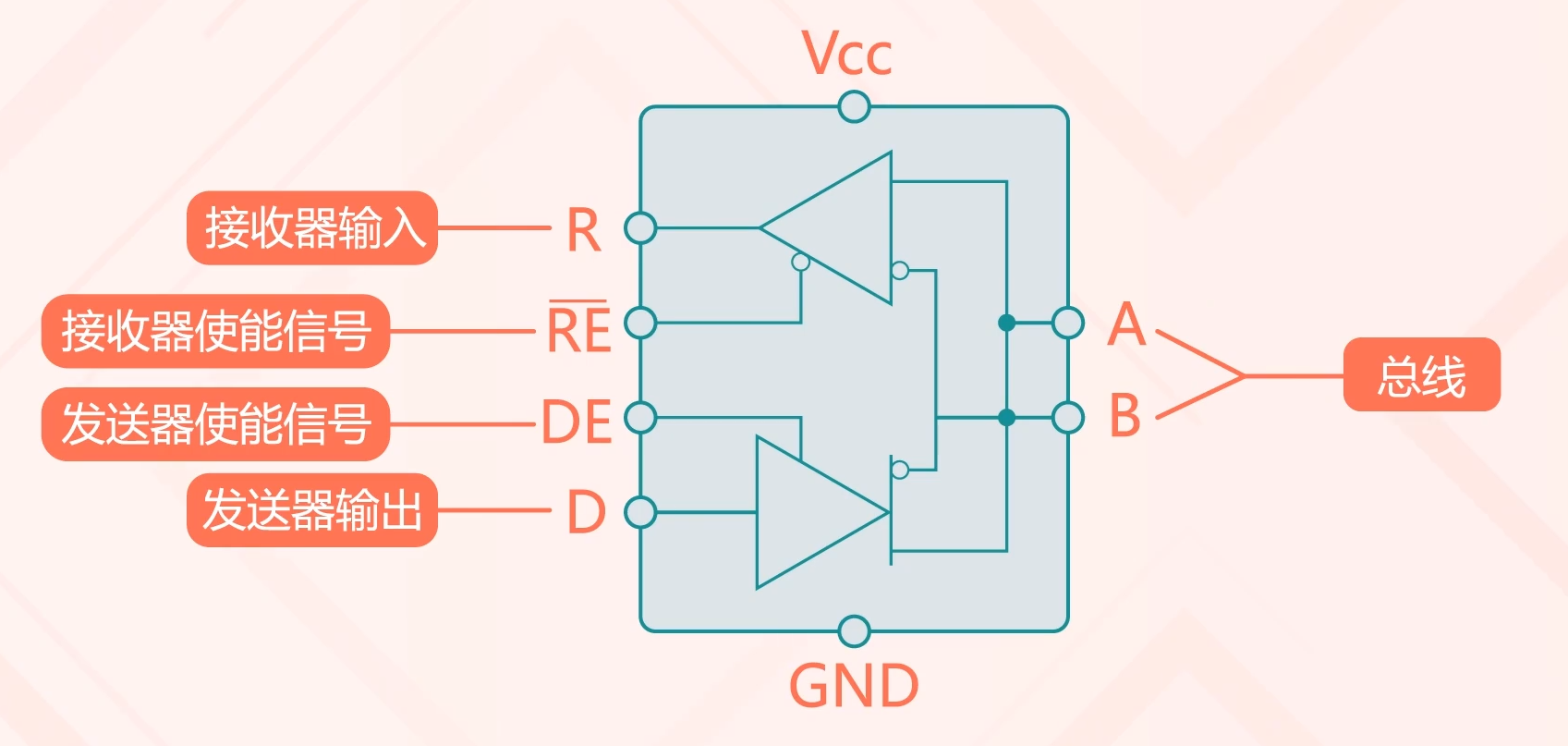

其內部結構如圖:

A、B為總線,R為接收器輸入,RE為接受器使能信號;DE為發送器使能信號,D為發送器輸出。

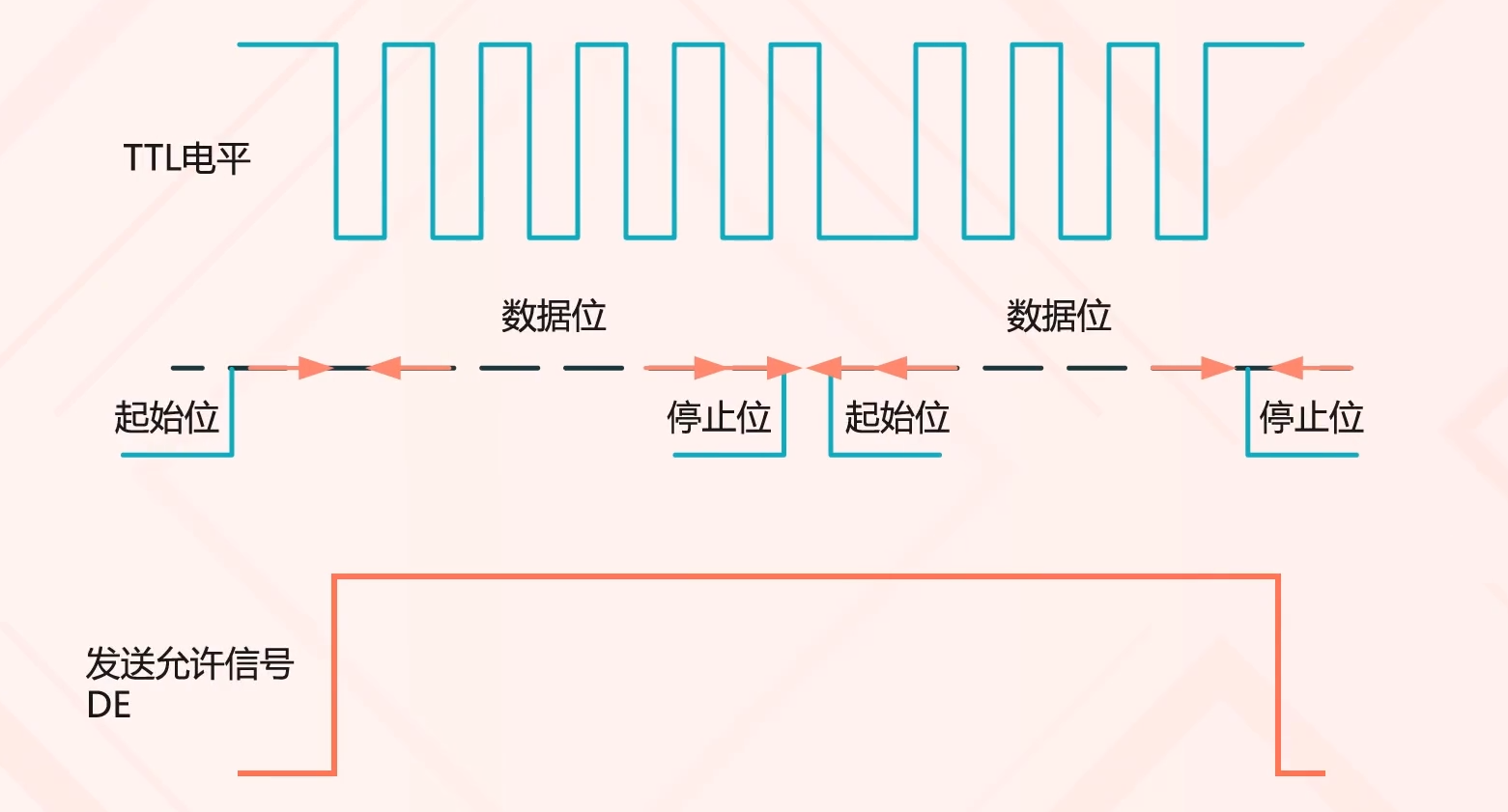

當它要發送數據時,DE要變成高電平,這樣A、B總線發送的數據才是正確的。

4、I2C總線

下面我們介紹另一類總線協議。I2C總線是由Philips公司開發的一種簡單、雙向二進制同步串行總線。因為它只需要兩根線,而且傳輸速度比較慢,所以方便實現。但是這些特點也使得I2C總線不適用于長距離傳輸,而多用于芯片間的信息傳遞。

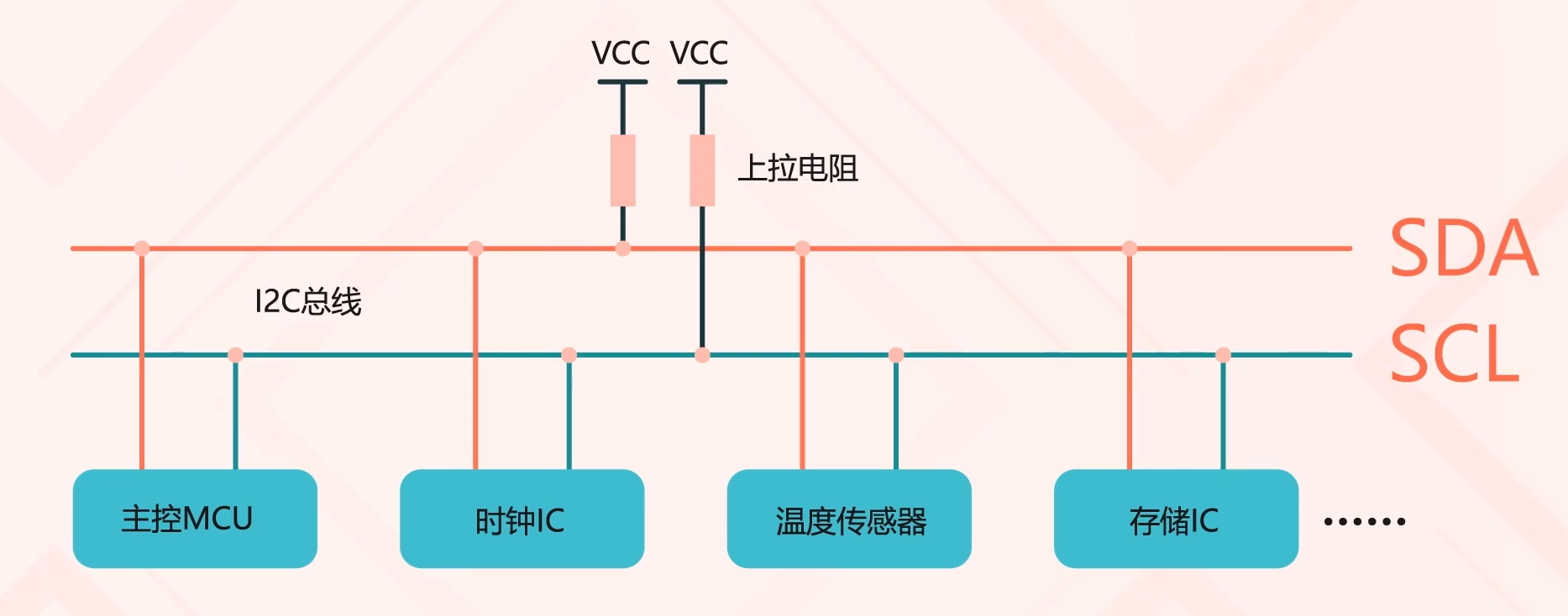

其物理層的連接如圖:

其中SCL總線負責傳遞時鐘信號,SDA總線傳遞數據信息。I2C總線傳輸數據時的時序圖是這樣的:

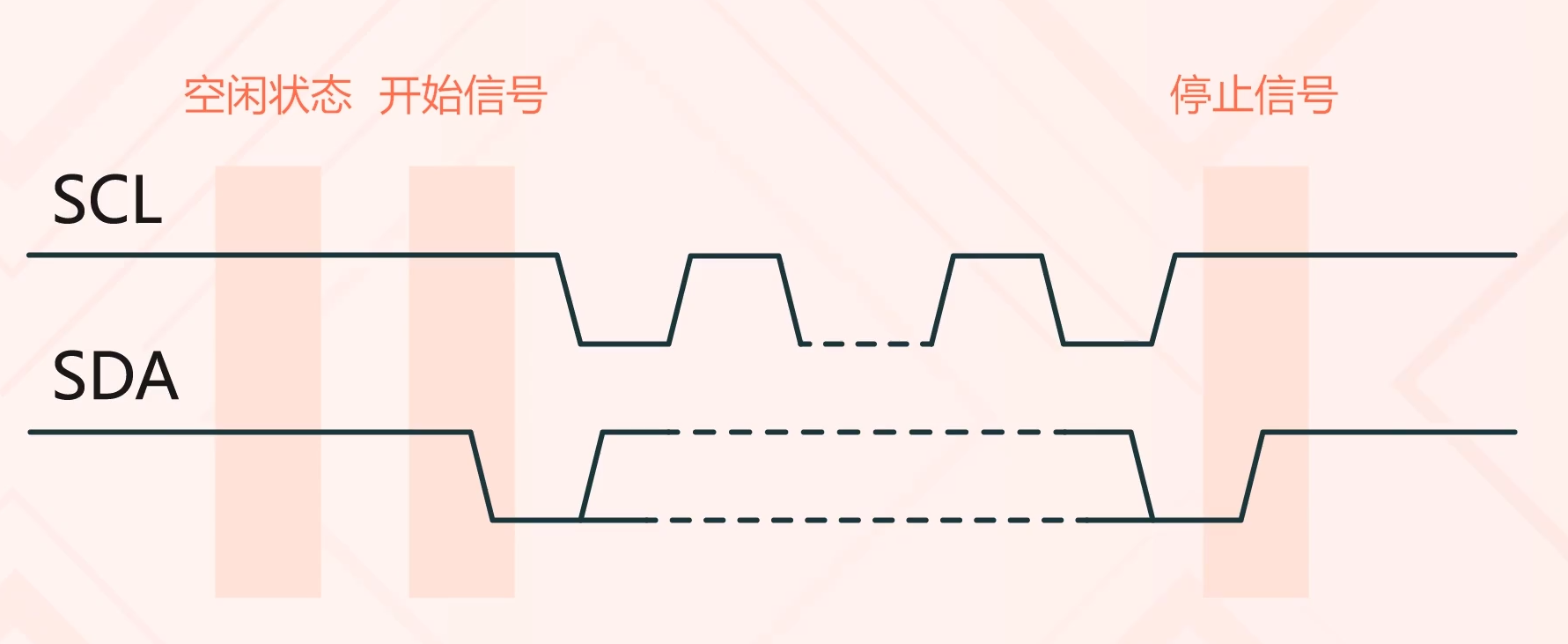

處于空閑狀態時,SCL和SDA均保持高電平;發送信號時,SDA由高電平轉換為低電平,SCL保持高電平;發送停止信號時,SDA由低電平轉換為高電平,SCL保持高電平。可以看到只有SCL為低電平時,SDA才能變換。當SCL保持高電平時,SDA上的電平是不能任意變化。

5、SPI總線

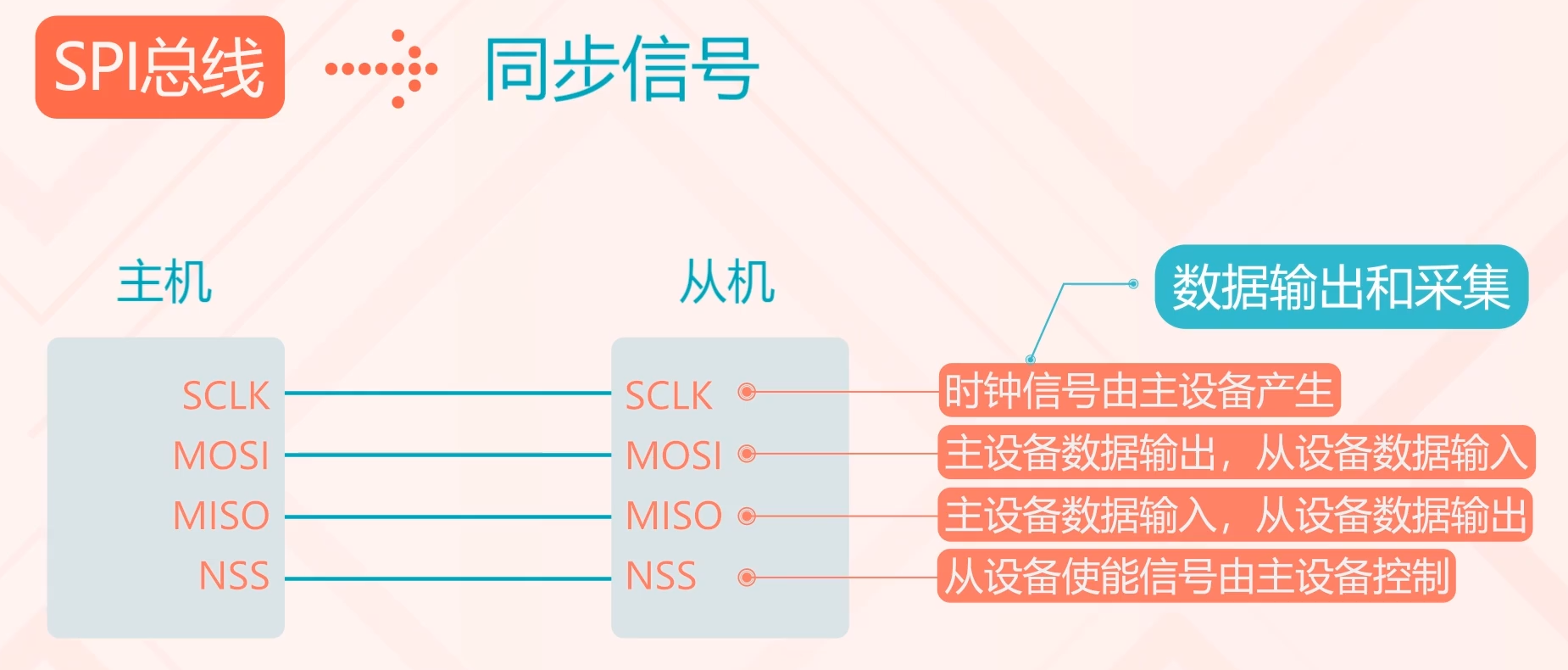

SPI總線是串行外設接口(Serial Peripheral Interface)的縮寫。它是一種4線總線,只占用芯片的4個管腳,節約了芯片管腳,而且硬件功能很強。所以在越來越多的芯片上都集成了這種通信協議。

它的四根總線分別是MISO:主設備數據輸入,從設備數據輸出;MOSI:主設備數據輸出,從設備數據輸入;SCLK,時鐘信號,由主設備產生;NSS:從設備使能信號,由主設備控制。

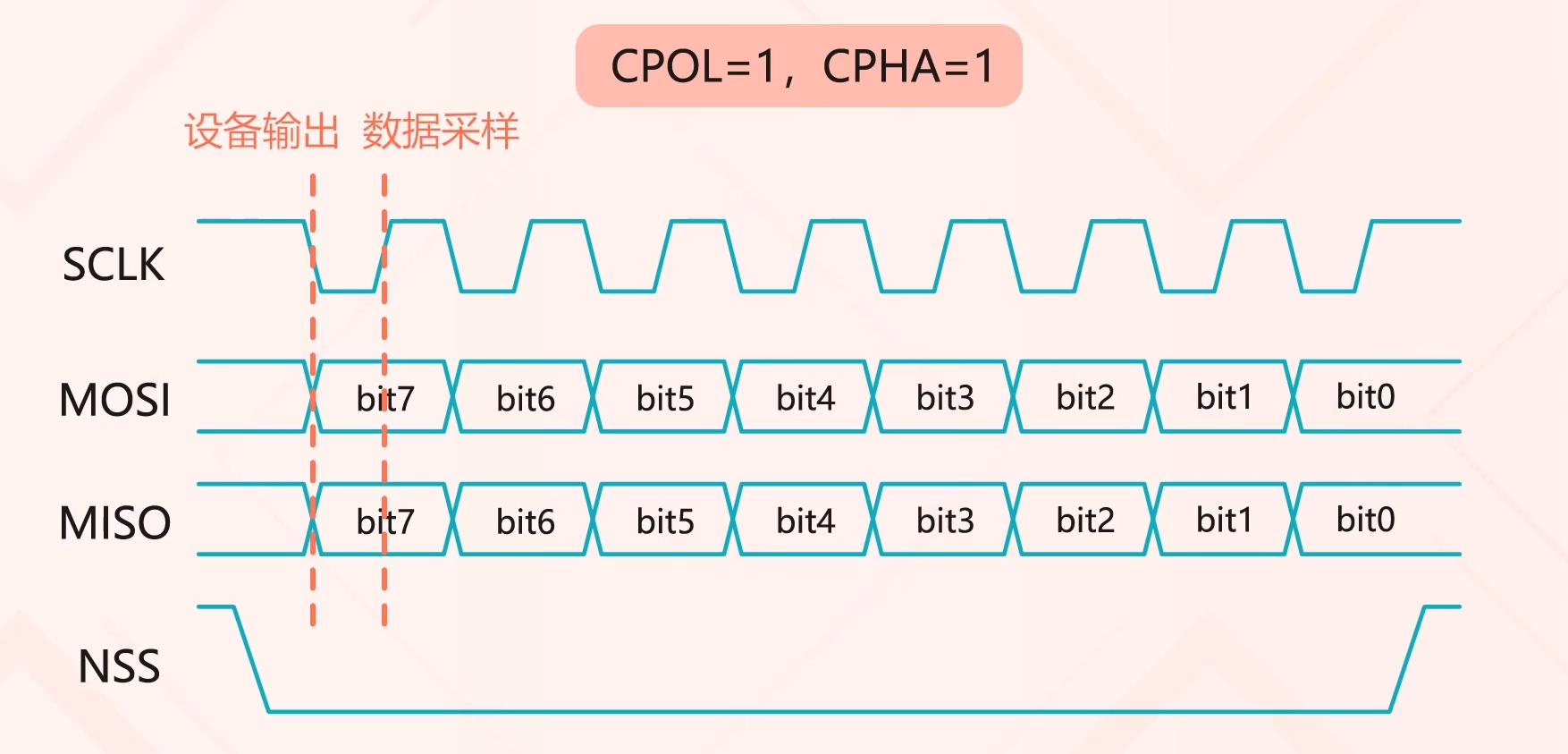

由于SPI是一種同步信號,數據的輸出和采集總是跟隨時鐘信號的變化而進行的。以CPOL=1,CPHA=1為例,可以畫出這樣時序圖:

CPOL=1表示時鐘是高電平時處于空閑;CPHL=1表示數據的輸出在一個時鐘周期的第一個沿上,也就是圖中時鐘信號的下降沿是設備輸出。推想而知,CPOL和CPHL都有0、1兩種取值,所以SPI總線有四種工作狀態,這里只列舉了其中的一種。

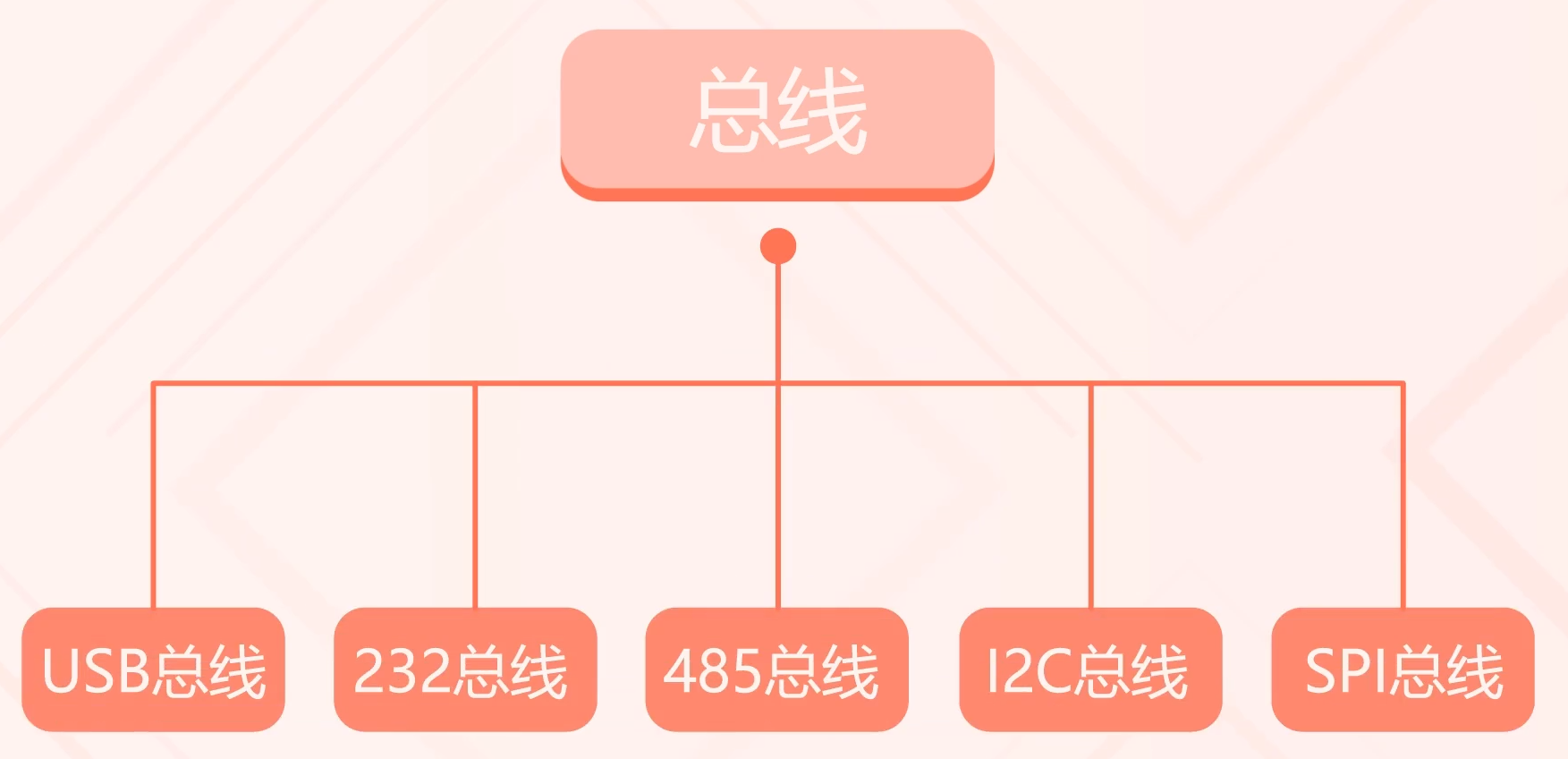

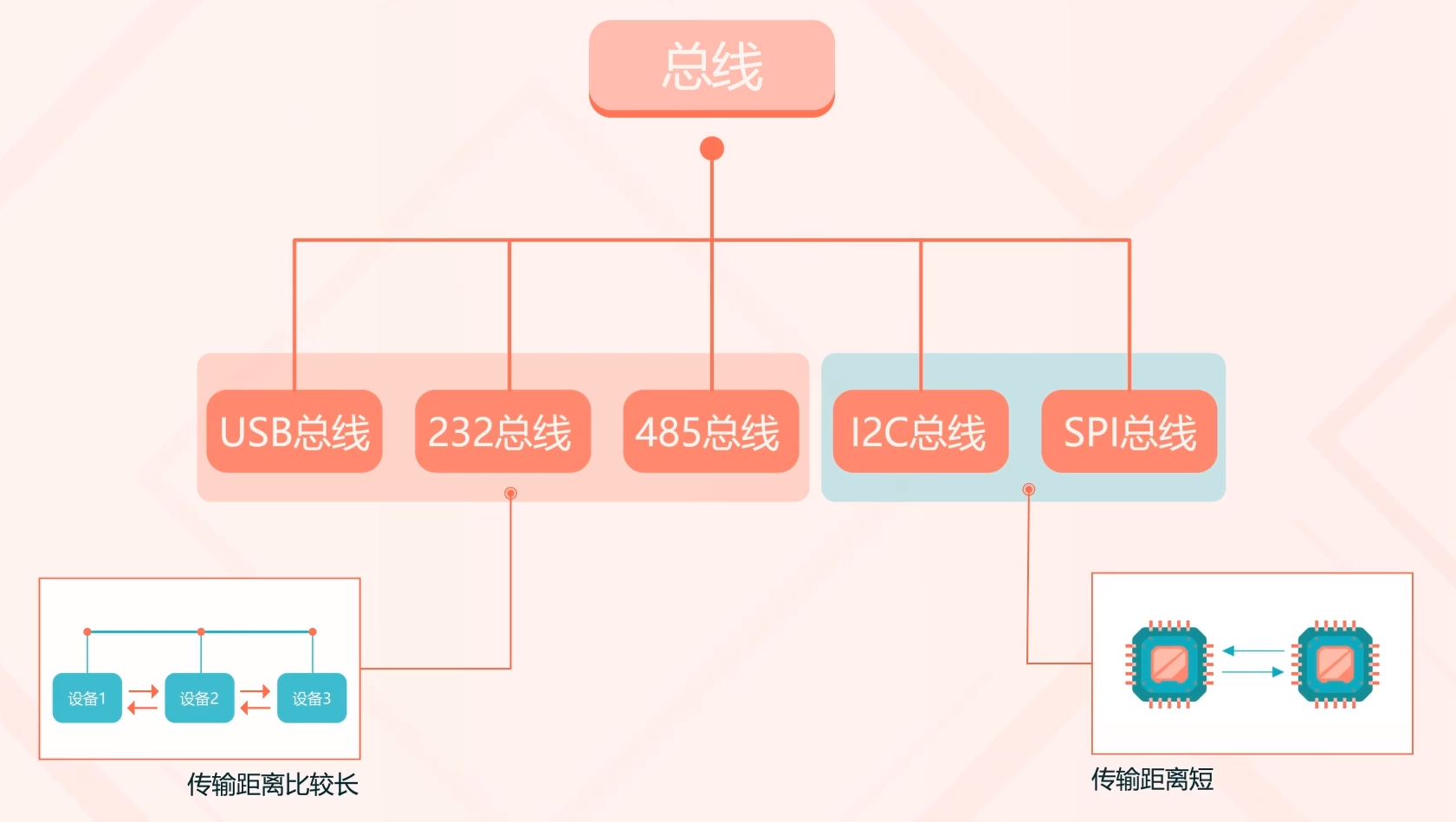

總線的類型有很多,我們可以將它們大致分為兩類:USB總線、232總線、485總線的傳輸距離相對而言比較長,所以用來建立各設備之間的信息傳遞。而I2C總線和SPI總線的傳輸距離相對較短,主要是完成電路板上的各種芯片以及處理器間的通訊。

同時需要注意:雖然總線上的數據以電壓的形式表現出來,但傳輸過程中有很多因素需要考量,比如傳輸的速率、高低電平的范圍、譯碼規則等等。因此用采集卡采集總線上的數字信號,需要復雜的編程邏輯,甚至需要一些電路調整,所以這并不是一個好的方案。不過,正如前面提到的,我們可以使用采集卡的DO端口輸出脈沖序列、模擬PWM信號、控制步進電機等等。用DI端口采集連續變化的數字波形進行數據分析。

感謝您的閱讀,以上就是本期文章的全部內容,如果對于文章內容有任何問題,都可以在評論區留言或搜索微信公眾號“Smacq思邁科華”直接聯系我們。請大家多多點贊、收藏、轉發。

我們下期再見!

Ps:文章的視頻內容可以點擊如下鏈接跳轉:什么是數字信號?

審核編輯 黃宇

-

數字信號

+關注

關注

2文章

1059瀏覽量

49525

發布評論請先 登錄

ADSP-2191M DSP:高性能數字信號處理解決方案

ADSP - 2188M:高性能數字信號處理利器

深入剖析ADSP - 2189M:高性能數字信號處理的理想選擇

TMS320VC5503 定點數字信號處理器深度剖析

SMx320VC33數字信號處理器:特性、參數與應用全解析

TMS320LC548定點數字信號處理器詳解

TMS320VC5416 定點數字信號處理器全面解析

TMS320VC5402 定點數字信號處理器深度解析

探索 NXP MC56F80xxx 數字信號控制器:特性、應用與設計要點

FUTEK QIA128數字信號調理模塊概述

什么是數字信號?

什么是數字信號?

評論