過去十年,AI算法和芯片架構的不斷創新,以及AI市場應用規模范圍的不斷擴大,兩者互相促進,給算法、架構、軟硬件集成、芯片設計都帶來了令人激動的新機遇。據麥肯錫研究報告預測,到2025年全球AI芯片市場預計將達到100億美元的規模。同時,算法和架構創新也給EDA流程中的芯片設計和驗證帶來了新的挑戰,需要新一代的EDA流程和工具的支持。

AI芯片設計與驗證挑戰

燧原科技資深架構師鮑敏祺表示:

“AI芯片往往具備超大的設計規模,同時,AI算法和應用的迭代周期短,因此在計算子系統、調度控制子系統、存儲子系統、高速通信子系統等多個領域,都提出了更高的設計要求。面對復雜的設計需求,AI芯片在驗證策略選擇上,也往往需要引入多種驗證手段,提前通過仿真、形式化驗證、FPGA原型驗證等一系列驗證手段發現問題,確保芯片在功能、功耗、調度性能等方面達到設計期望。”

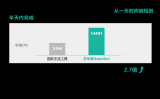

AI芯片設計結構復雜,不同子系統往往具備差異化的驗證重點,也就需要不同的驗證工具組合,實現驗證效果的最大化。然而業內人士普遍認為,當前驗證環節點工具各自為政帶來的高門檻和低效率,特別是“工具缺乏兼容性、數據碎片化、工具缺乏創新”等痛點,已成為目前芯片設計追求更快、更強、更簡單的三大阻礙。有數據顯示,每種工具在驗證中的激勵移植、重復編譯、碎片化調試所浪費的時間通常占到總體驗證時間的30%以上。

AI芯片高效驗證之道

芯華章科技驗證工程副總裁朱洪辰表示:

“面對這些挑戰,去年芯華章正式推出了從底層框架全新構建的智V驗證平臺,具備‘協同、易用、高效’三大優勢,能讓工具帶來1+1》2的驗證效益,有效地解決產業正面臨的兼容性挑戰,以及數據碎片化導致的驗證效率挑戰。”

基于智V驗證平臺,芯華章目前已經推出了多款數字驗證工具,涵蓋FPGA原型驗證、邏輯仿真、形式驗證、智能場景驗證、系統調試等領域。

芯華章科技驗證工程總監高世超介紹:

“為了提高AI芯片驗證效率,芯華章提供了融合高效的AI芯片驗證調試解決方案。我們的形式化驗證工具GalaxFV可與仿真技術結合,加速AI驗證覆蓋率收斂;智能場景驗證工具GalaxPSS,能夠利用場景建模自動生成跨平臺、可復用、智能化自回歸的測試激勵;數字驗證調試系統Fusion Debug則貫穿所有工具,提供了跨平臺的高效調試解決方案。”

芯華章科技驗證工程總監劉勤一表示:

“FPGA原型驗證對于提升超大規模的AI芯片設計效率,具備得天獨厚的技術解決優勢。基于FPGA硬件和擁有自主知識產權的全流程軟件,芯華章自主研發的高性能FPGA原型驗證系統樺捷(HuaPro-P1),可以幫助SoC/ASIC芯片客戶實現設計原型的自動綜合、分割、優化、布線和調試,從而有效減少用戶人工投入,提升系統驗證與軟件開發效率,縮短芯片設計周期。”

原文標題:對話燧原科技 | 芯華章帶來AI芯片高效驗證之道

文章出處:【微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636330 -

AI

+關注

關注

91文章

39793瀏覽量

301408 -

驗證系統

+關注

關注

0文章

27瀏覽量

10468 -

芯華章

+關注

關注

0文章

195瀏覽量

11981

原文標題:對話燧原科技 | 芯華章帶來AI芯片高效驗證之道

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

是德科技與聯發科技聯合完成一項工作原型驗證

思爾芯榮登“國產EDA工具口碑榜”,以“芯神瞳”原型驗證解決方案賦能芯片創新

開芯院采用芯華章高性能數字仿真器GalaxSim,RISC-V 驗證獲近3倍效率提升

FPGA原型驗證實戰:如何應對外設連接問題

【喜報】芯神瞳原型驗證解決方案榮膺工博會“集成電路創新成果獎”

西門子桌面級原型驗證系統Veloce proFPGA介紹

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

芯華章高性能FPGA原型驗證系統實現設計原型自動綜合、布線和調試

芯華章高性能FPGA原型驗證系統實現設計原型自動綜合、布線和調試

評論