在高速數字信號中,PCB布線的目的,就是保證接收端能夠正確接收到發射端的信號。正確體現在兩個方面:

(1)如果設計到時鐘的話,需要保證時序的正確性;

(2)波形幅度需要符合要求,因為數字信號一般對大于VIH的電平判別為高,低于VIL的電平判別為地。所以,當幅度處于VIL~VIH之間的話,則無法判斷。

總之,我們希望PCB布線不會影響到信號的波形。

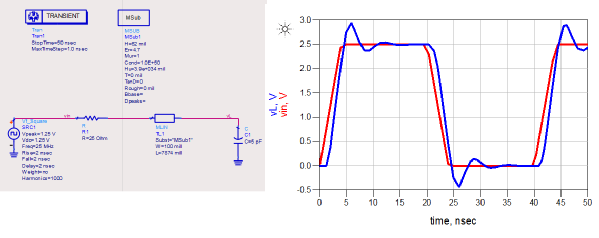

微帶線失配,會產生反射,導致波形失真,如下圖所示。藍線為負載端輸出信號,紅線為源輸出信號。接收端信號產生振鈴。

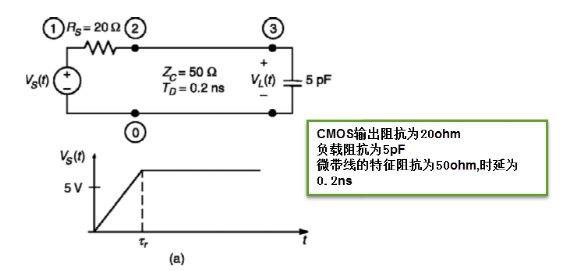

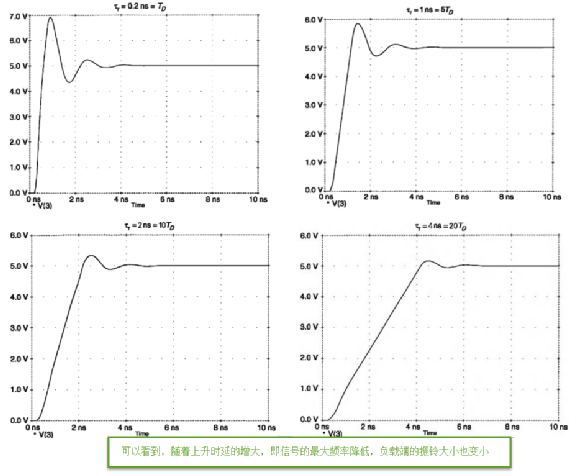

以下例子是比較合理的假設,因為一般CMOS的輸出阻抗為10~30ohm,而CMOS的輸入一般呈容性,容值為5~15pF。

微帶線終端負載對信號波形的影響

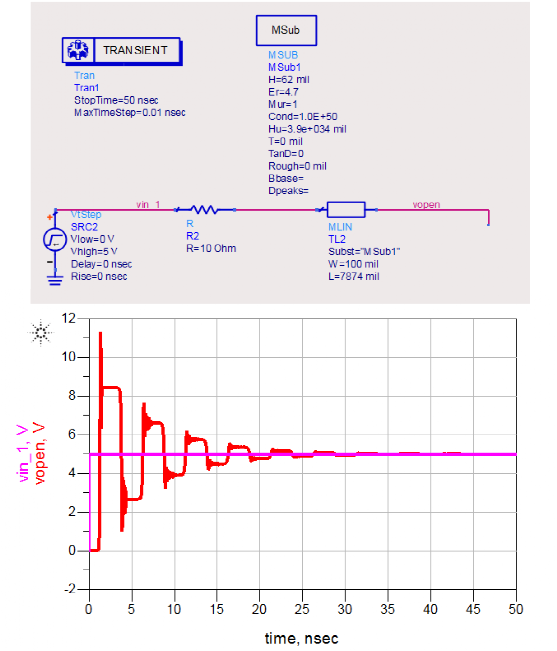

終端負載為開路

如下圖所示,可以看到,當負載為開路時,其接收端的信號,會先產生振鈴,然后再穩定在5V。而在振鈴處,最高電壓能到11V,最低值在1V左右,高壓可能導致芯片的損壞,低壓可能導致芯片的誤判。

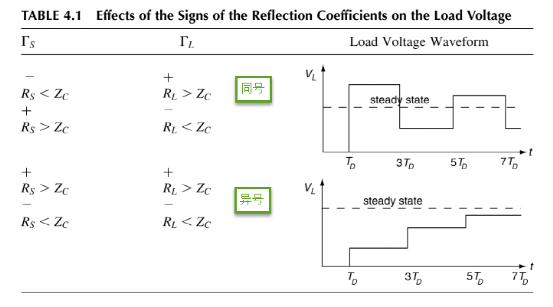

這些振鈴的產生,是因為信號在負載端和源端不斷地來回反射,疊加產生的。所以,Γs和ΓL的符號的不同,還會影響疊加信號的波形。

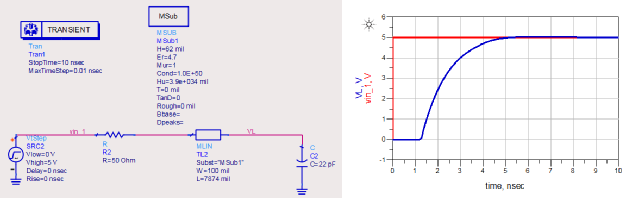

終端負載為容性負載

假設源端做了串聯匹配。源端信號為0上升時間的理想階躍信號,電容在剛開始時,看上去為短路,然后緩慢地變成開路。電容會引入額外的時延。

匹配策略

反射會引起信號失真,而源端和終端的失配會引起反射。那想緩解信號的失真,有效的手段,就是進行匹配。

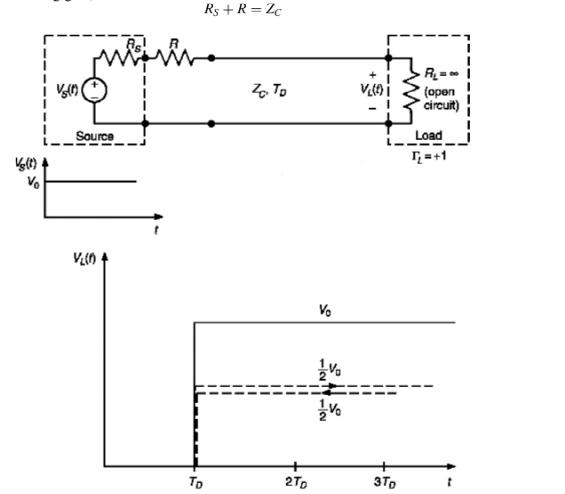

串聯匹配

一般來說,典型的CMOS的輸出阻抗都小于PCB的特征阻抗,所以可以在PCB線上加一個電阻,使得Rs+R=Zc,這樣,在源端沒有反射。

這種匹配方式,即為串聯匹配。

在串聯匹配的情況下,源端輸出到微帶線的電壓為V0/2,而終端負載一般為開路或者類似開路,所以負載反射系數為1,因此在負載處的電壓為V0/2+V0/2=V0,信號完整性很好。

而且,對于開路負載,沒有電流流入該電阻,所以不額外耗散功率。

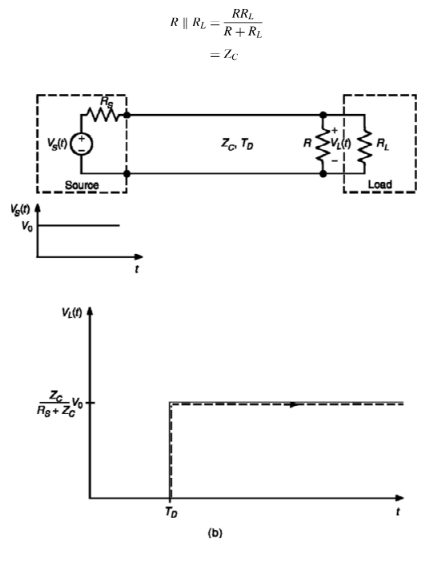

并聯匹配

并聯匹配,即在負載端并聯一電阻R,使得負載阻抗為Zc。

并聯匹配下,接收到的電壓會比發射端的電壓小,因為并聯匹配時,沒有負載反射來提高輸入波形的電壓。而且,即使對于開路負載,并聯電阻上也會有電流,因此匹配負載會消耗功率。

那什么時候,可以不care微帶線的長度,而且不需要做匹配呢?

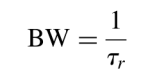

假設脈沖信號的上升時間為τr,則該脈沖對應的主要頻譜帶寬為

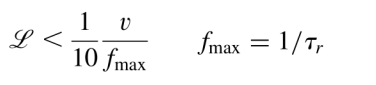

想要微帶線的尺寸可以忽略,則需要其長度小于傳輸信號最大頻率時對應波長的十分之一。

即

所以,當微帶線的長度和傳輸信號的上升沿時間有如下關系時,微帶線上的任意失配基本不會造成信號的失真。

參考文獻:

CLAYTON R. PAUL Introduction to electromagnetic compatibility

審核編輯 :李倩

-

數字信號

+關注

關注

2文章

1056瀏覽量

49324 -

PCB布線

+關注

關注

22文章

473瀏覽量

43539

原文標題:高速數字信號的匹配問題

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

函數信號發生器和任意波形信號發生器區別詳解

深入探討PCB布局布線的專業設計要點與常見挑戰

PCB設計 | AI如何顛覆PCB設計?從手動布線到智能自動化的30年演進

PCB布局布線的相關基本原理和設計技巧

超強超全布線經驗教程大全

高速PCB布局/布線的原則

PCB布線怎么才不會影響到信號的波形

PCB布線怎么才不會影響到信號的波形

評論