基于UVM搭建驗證環境和構造驗證激勵,調試的工作總是繞不開的。實際上,對驗證環境和激勵的調試,往往伴隨著驗證階段的前半程,并且會花掉驗證工程師很多時間和精力。然而,大部分細節被隱藏在復雜的環境內部。這里的復雜,指的是UVM本身構造的不同機制(比如factory、config_db、objection等),以及在不同機制內部使用的數據結構。

作為UVM的用戶,我們需要相信在絕大部分情況下這些機制本身是沒有問題的。因此,從頂層獲得有效的調試信息就非常關鍵,比起潛入到內部要高效得多。

這也是本文的目的,盤點UVM針對不同機制提供給用戶的調試功能。建議收藏和關注,總有一天你會用到。本文的示例代碼都是在UVM類庫提供的例程上進行少量修改得到的。

01 PLUGARG(命令行參數)

01 PLUGARG(命令行參數)

UVM將不同機制的調試功能封裝成了命令行參數。在運行仿真的時候帶上這些參數,就可以在仿真日志中打印出來對應的詳細調試信息。本節將這些命令行參數都梳理出來,并附有仿真日志截圖。

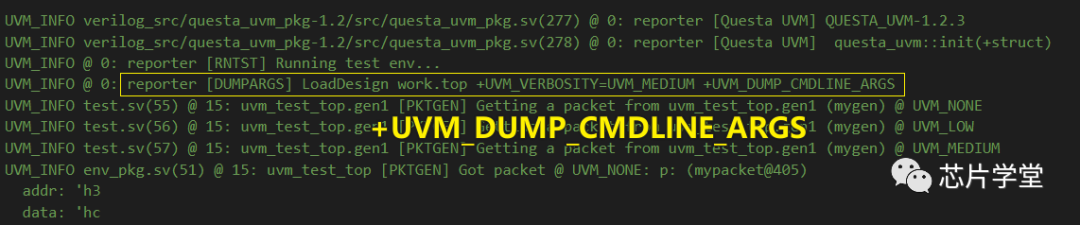

+UVM_DUMP_CMDLINE_ARGS:導出所有的命令行參數,確認當前的命令行參數符合你的預期。

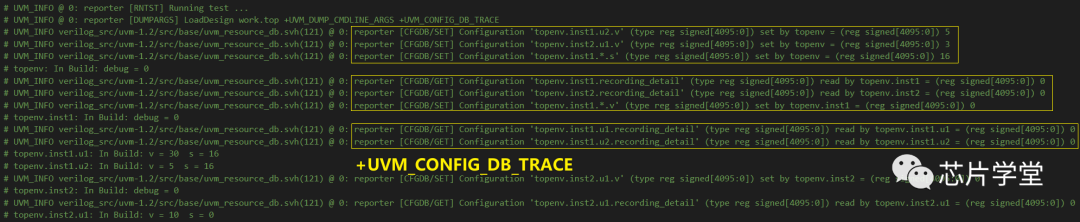

+UVM_CONFIG_DB_TRACE: 打開訪問Config_db的追蹤(tracing)功能,可以看到config_db的set和get操作在什么時間由什么組件發起。

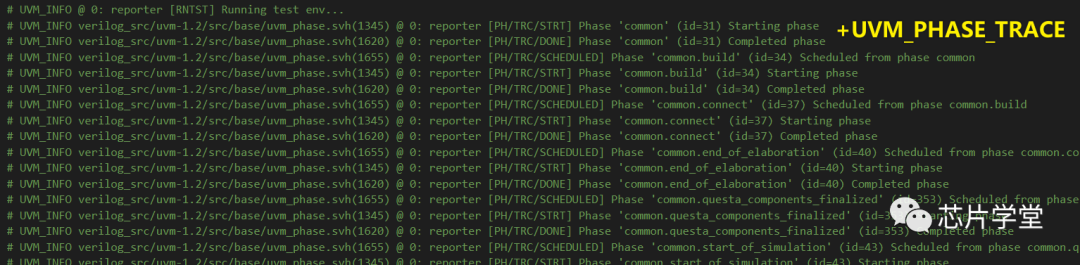

+UVM_PHASE_TRACE:打開Phase執行的追蹤功能,可以看到不同phase的執行順序。

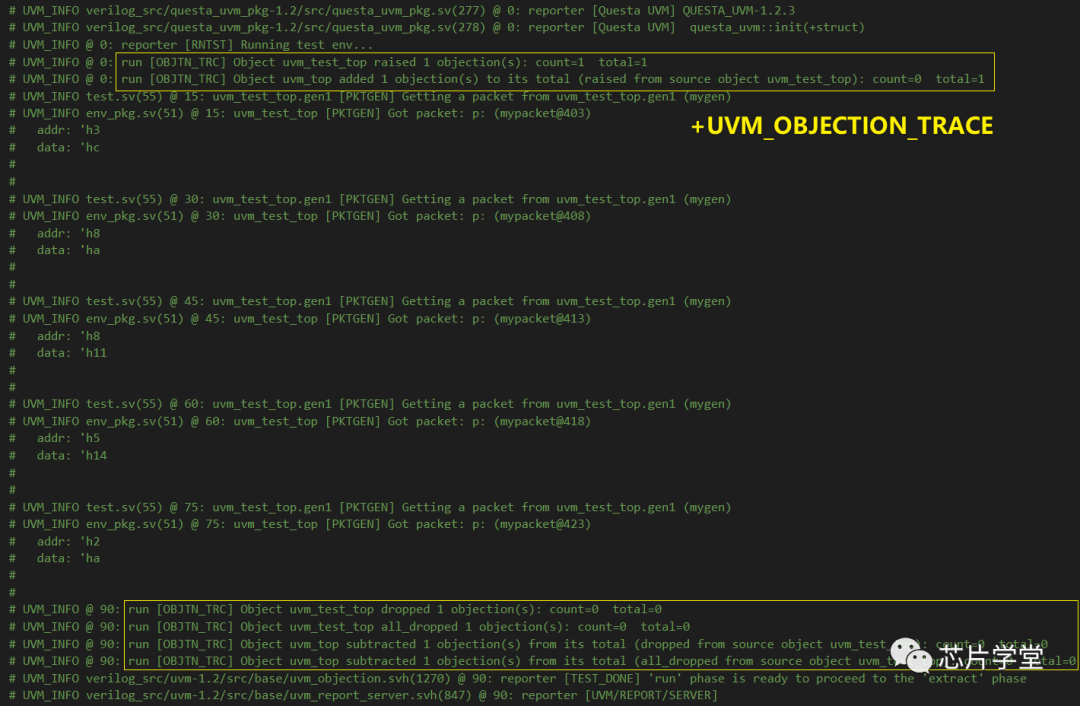

+UVM_OBJECTION_TRACE:打開Objection相關活動的追蹤功能,可以清晰地呈現出objection在運行中的狀態。

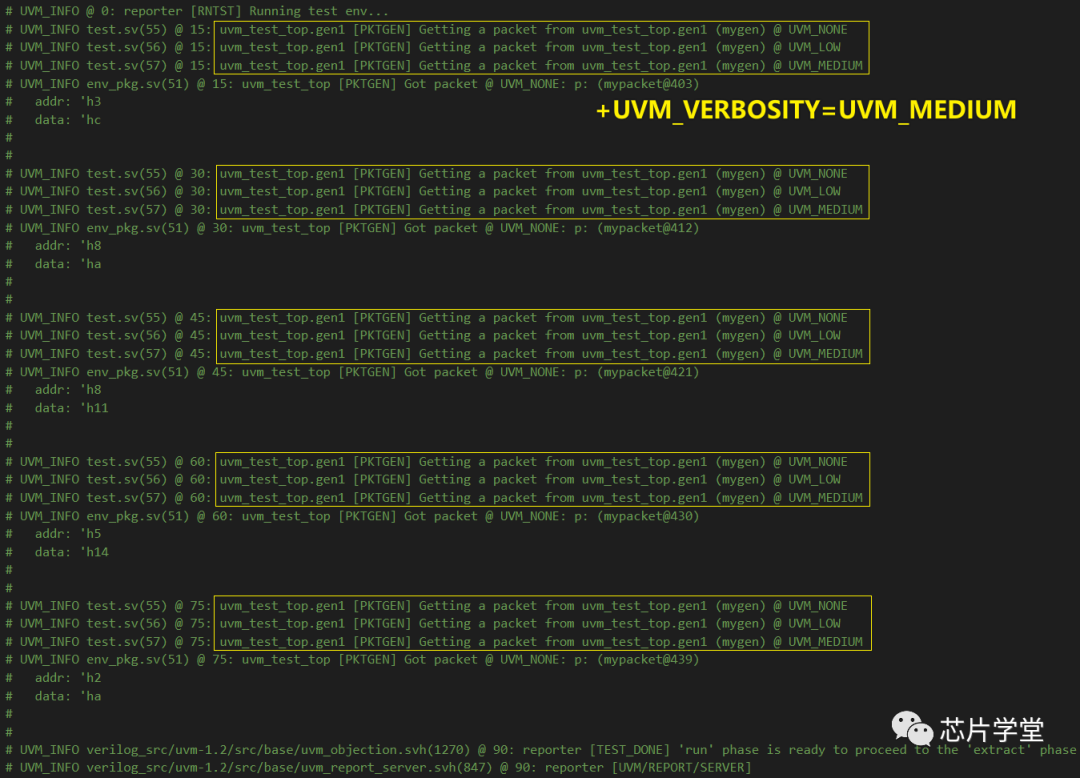

+UVM_VERBOSITY:設置打印信息的冗余程度,有效地控制不同重要性信息的打印和屏蔽。

02 PRINT(打印)

02PRINT(打印)

除了命令行參數,UVM還提供了很多內置打印函數。這些函數可以在驗證環境中被調用,調用后會將對應的數據結構按照強可讀性的格式打印到仿真日志中,為環境調試工作提供極大的便利。

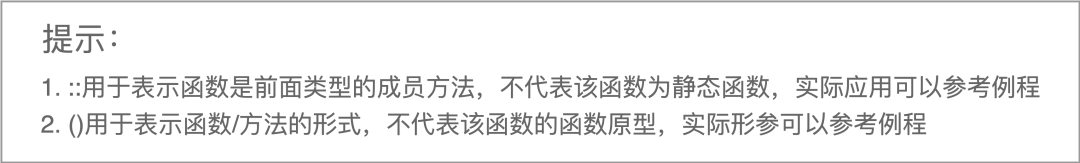

uvm_root::print_topology():打印整個驗證環境的組件拓撲結構

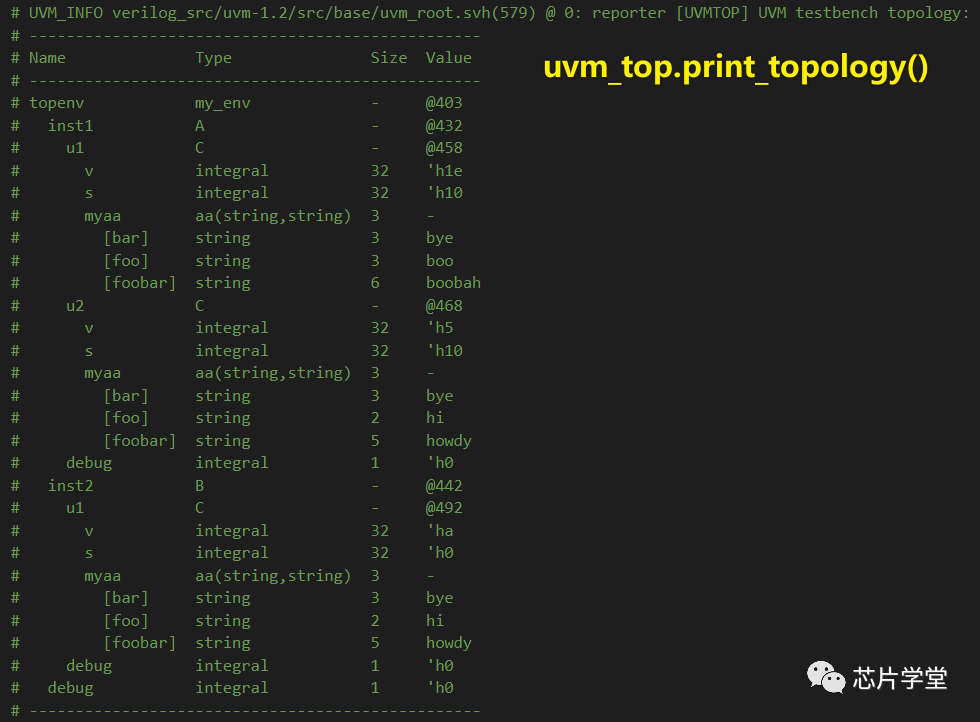

uvm_component::print_config():打印當前組件可見視角下的所有配置資源信息

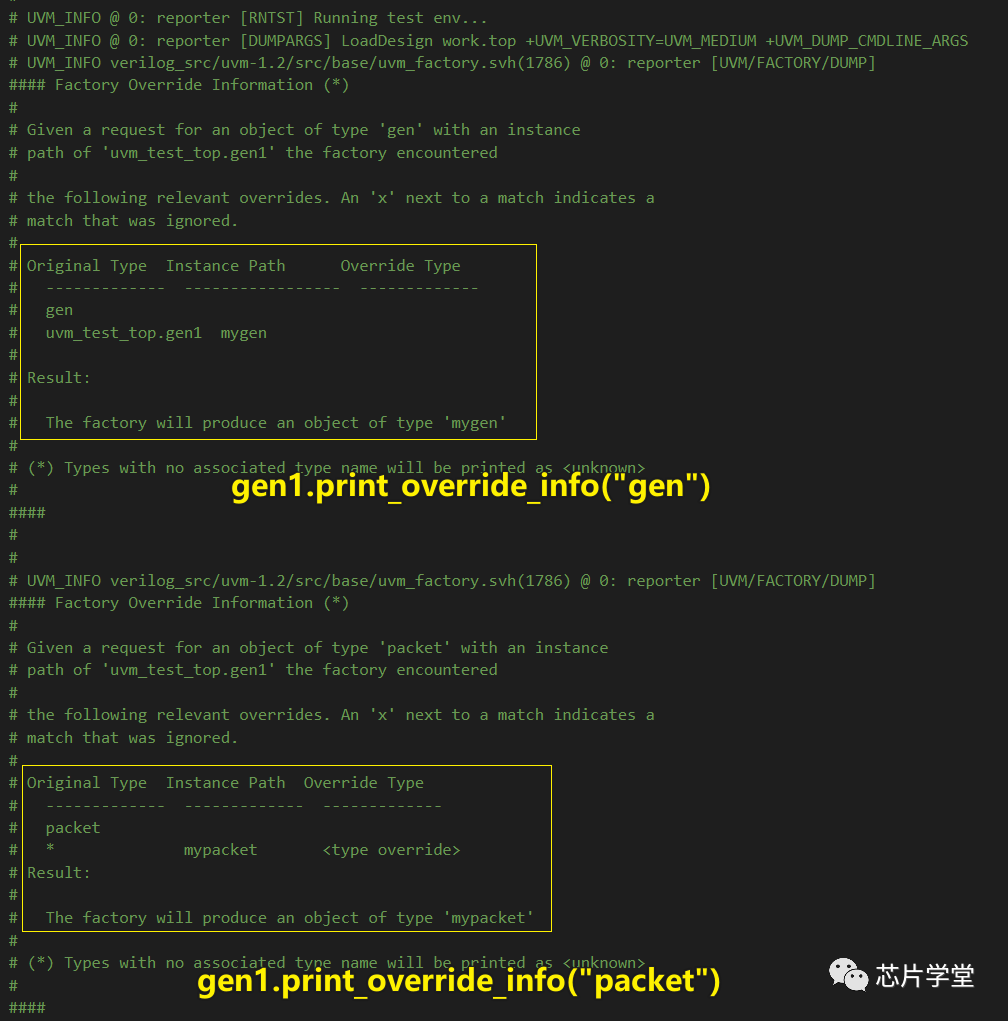

uvm_component::print_override_info():打印當前組件的工廠重載信息

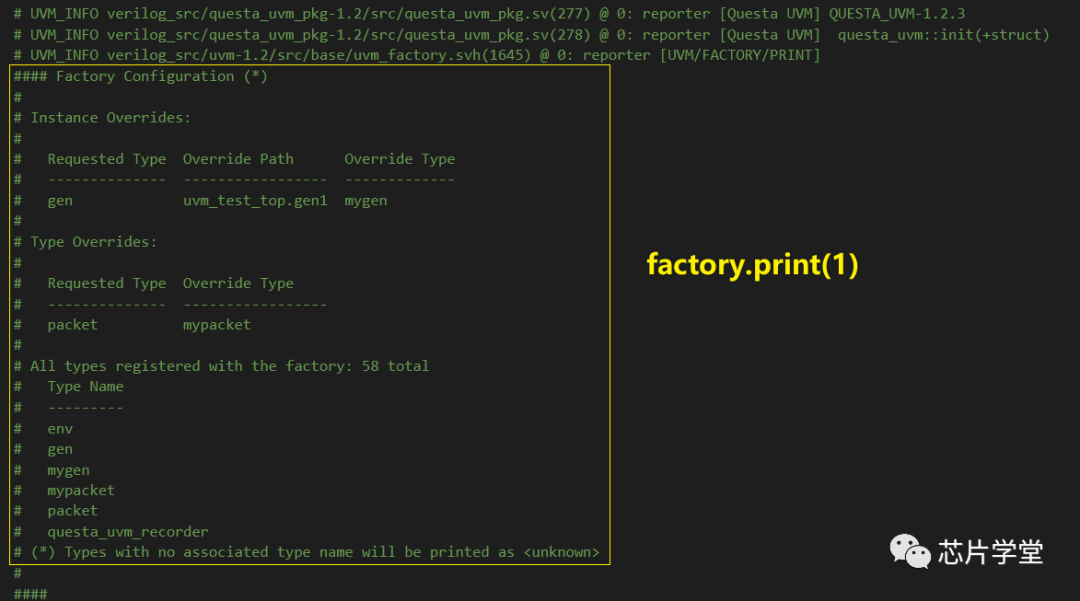

uvm_factory::print():打印全局工廠中注冊的類型以及instance和type重載信息

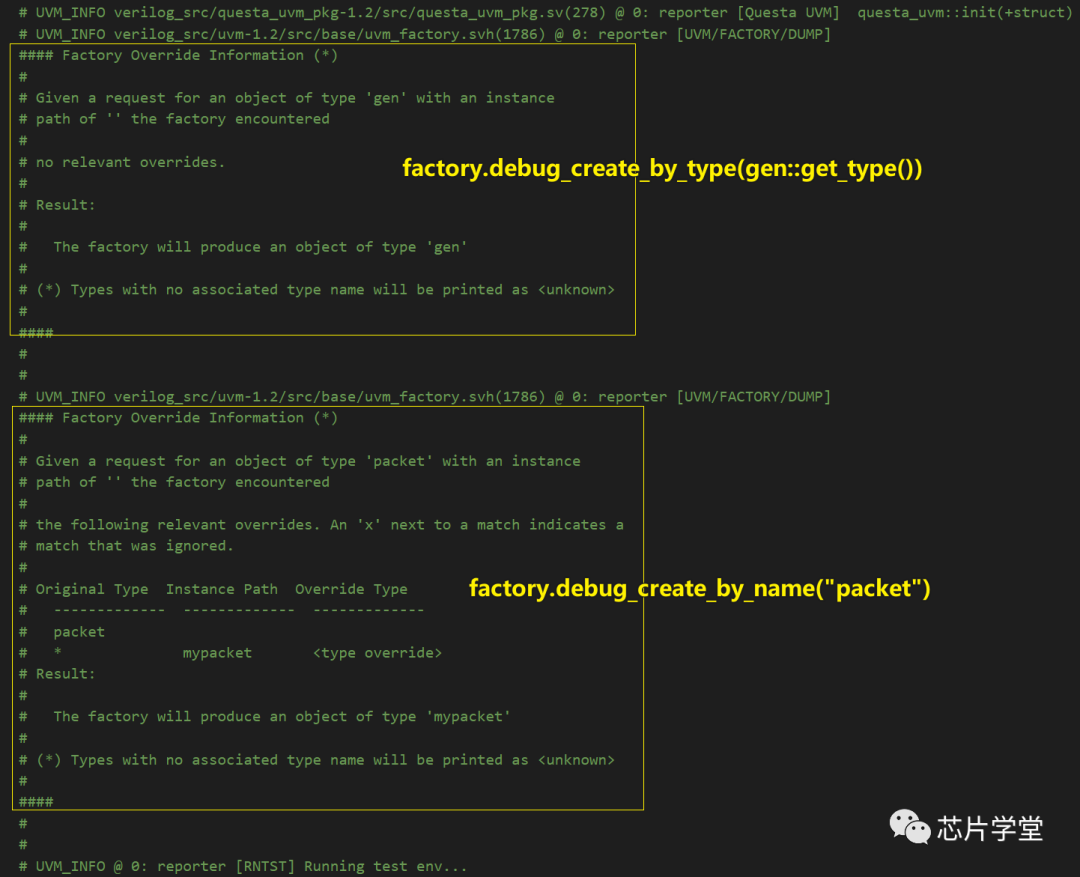

uvm_factory::debug_create_by_type():打印工廠根據參數實際會創建的類型

uvm_factory::debug_create_by_name():打印工廠根據參數實際會創建的類型

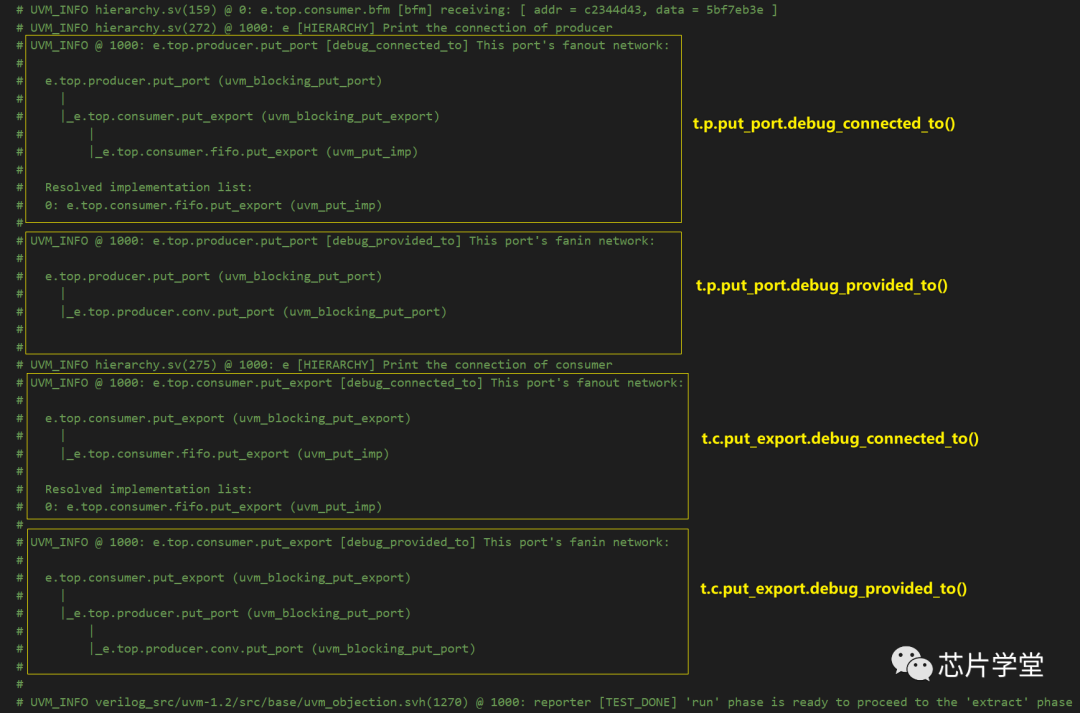

uvm_port_base::debug_connected_to():打印當前端口連接的下游端口網絡,包括port/export/imp

uvm_port_base::debug_provided_to():打印當前端口連接的上游端口網絡,包括port/export

審核編輯 :李倩

-

仿真

+關注

關注

54文章

4466瀏覽量

138034 -

UVM

+關注

關注

0文章

183瀏覽量

19985 -

機制

+關注

關注

0文章

24瀏覽量

10019

原文標題:SystemVerilog | UVM | 超實用!盤點UVM不同機制的調試功能

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

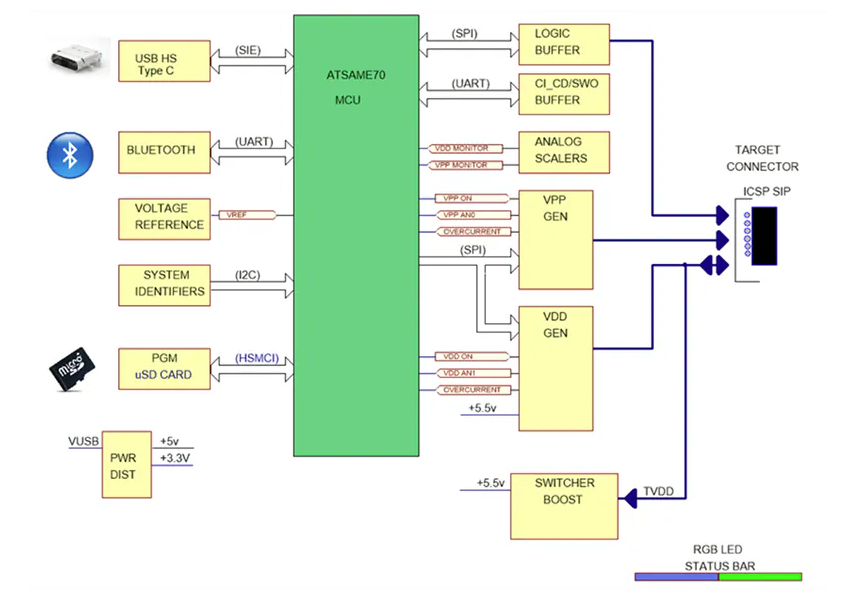

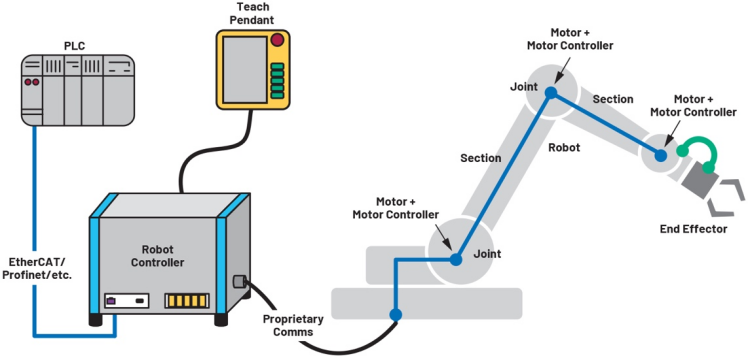

用于SWD/JTAG調試器的多功能轉接板設計

MPLAB? PICkit?5 內電路調試器技術解析與應用指南

AppTest邀請測試---邀請用戶參與測試

AppTest邀請測試 -邀請用戶

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

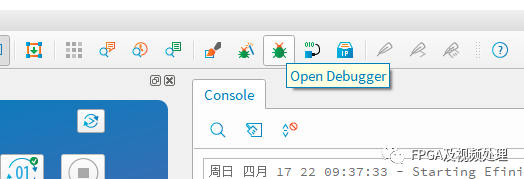

Efinity debuger常見問題總結-v4

盤點UVM針對不同機制提供給用戶的調試功能

盤點UVM針對不同機制提供給用戶的調試功能

評論