近日,據外媒報道,半導體聯(lián)盟ISMC表示將在印度修建半導體芯片工廠。

半導體聯(lián)盟ISMC是由Next Orbit Ventures和高塔半導體投資成立的,據悉本次新建的工廠將用于生產65nm制程工藝芯片,計劃投資30億美元,若該項目順利完成,這個工廠將成為印度首座半導體芯片工廠。

不過65nm制程在臺積電等芯片大廠來看是相當落后的,貢獻的營收也少得可憐,我國早在10年前就已經開始生產65nm了。

不過對于半導體芯片行業(yè)發(fā)展較晚的國家來說,65nm在收益與技術難度方面也是恰到好處的,例如目前中芯國際65nm所帶來的收益依然能名列前茅,考慮到這是印度的第一座半導體芯片工廠,該廠的建立將會極大地推動印度半導體產業(yè)的發(fā)展,并且會提供1500多個崗位供人就業(yè)。

綜合整理自 半導體行業(yè)觀察 芯查查 國際電子商情

審核編輯 黃昊宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

65nm

+關注

關注

0文章

5瀏覽量

9501 -

半導體芯片

+關注

關注

61文章

943瀏覽量

72635

發(fā)布評論請先 登錄

相關推薦

熱點推薦

芯源的MOSFET采用什么工藝

采用的是超級結工藝。超級結技術是專為配備600V以上擊穿電壓的高壓功率半導體器件開發(fā)的,用于改善導通電阻與擊穿電壓之間的矛盾。采用超級結技術有助于降低導通電阻,并提高MOS管開關速度,

發(fā)表于 01-05 06:12

0.2nm工藝節(jié)點的背后需要“背面供電”支撐

實現(xiàn)0.2nm工藝節(jié)點。 ? 而隨著芯片工藝節(jié)點的推進,芯片供電面臨越來越多問題,所以近年英特爾、臺積電、三星等廠商相繼推出背面供電技術,旨

半導體特定型圖像傳感器“65nm BSI-CIS”的詳解;

【博主簡介】本人“ 愛在七夕時 ”,系一名半導體行業(yè)質量管理從業(yè)者,旨在業(yè)余時間不定期的分享半導體行業(yè)中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容

目前最先進的半導體工藝水平介紹

1.8nm)制程 技術亮點:這是英特爾首個2納米級別制程節(jié)點,采用了全環(huán)繞柵極晶體管(Gate-All-Around, GAA)和背面供電網絡(Backside Power Delivery Network)。與Intel 3制程相比,每瓦性能提升達15%,

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

封裝測試**

1.**封裝前測試**

在將芯片進行封裝之前,需要對芯片進行再次測試,以確保芯片在運輸、存儲等過程中沒有受到損壞。半導體測

發(fā)表于 10-10 10:35

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業(yè)的前沿技術

%。至少將GAA納米片提升幾個工藝節(jié)點。

2、晶背供電技術

3、EUV光刻機與其他競爭技術

光刻技術是制造3nm、5nm等工藝節(jié)點的高端半導體

發(fā)表于 09-15 14:50

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

。那該如何延續(xù)摩爾神話呢?

工藝創(chuàng)新將是其途徑之一,芯片中的晶體管結構正沿著摩爾定律指出的方向一代代演進,本段加速半導體的微型化和進一步集成,以滿足AI技術及高性能計算飛速發(fā)展的需求。

CMOS

發(fā)表于 09-06 10:37

高精度半導體冷盤chiller在半導體工藝中的應用

在半導體產業(yè)的工藝制造環(huán)節(jié)中,溫度控制的穩(wěn)定性直接影響芯片的性能與良率。其中,半導體冷盤chiller作為溫控設備之一,通過準確的流體溫度調節(jié),為半

半導體芯片制造Fab工廠布局和結構簡介-江蘇泊蘇系統(tǒng)集成有限公司

在半導體產業(yè)的核心地帶,芯片制造工廠以其高度自動化、超凈環(huán)境和復雜的工藝流程聞名。這些工廠不僅是技術密集型的象征,更是精密工程與空間設計的典

蘇州芯矽科技:半導體清洗機的堅實力量

控化學試劑使用,護芯片周全。

工藝控制上,先進的自動化系統(tǒng)盡顯精準。溫度、壓力、流量、時間等參數(shù)皆能精確調節(jié),讓清洗過程穩(wěn)定如一,保障清洗效果的一致性和可靠性,極大降低芯片損傷風險,為半導體

發(fā)表于 06-05 15:31

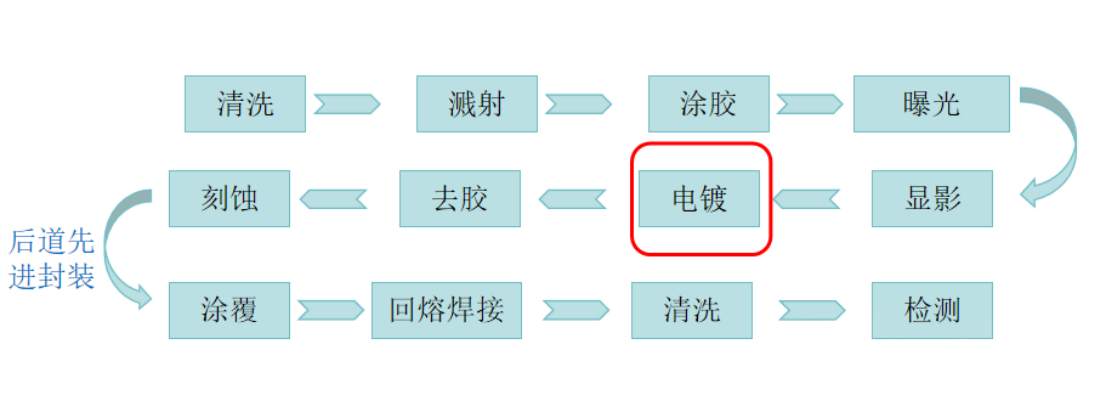

揭秘半導體電鍍工藝

一、什么是電鍍:揭秘電鍍機理 電鍍(Electroplating,又稱電沉積 Electrodeposition)是半導體制造中的核心工藝之一。該技術基于電化學原理,通過電解過程將電鍍液中的金屬離子

三星在4nm邏輯芯片上實現(xiàn)40%以上的測試良率

%左右開始,隨著進入量產階段,良率會逐漸提高”。

星電子將在 12Hi HBM4 中采用 1c nm DRAM 內存芯片和 4nm 邏輯芯片

發(fā)表于 04-18 10:52

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

資料介紹

此文檔是最詳盡最完整介紹半導體前端工藝和后端制程的書籍,作者是美國人Michael Quirk。看完相信你對整個芯片制造流程會非常清晰地了解。從硅片制造,到晶圓廠芯片

發(fā)表于 04-15 13:52

印度將修建首座半導體芯片工廠,采用65nm工藝

印度將修建首座半導體芯片工廠,采用65nm工藝

評論