目錄

近期打算寫一些Cadence的使用總結,一來是可以加深自己對Cadence的熟悉程度,二來也可以替廣大讀者節約摸索時間。如有出入和需補充的地方,歡迎大家在評論區或私聊中指出。本期,作者擬介紹Cadence中Calculator的使用。我會在開頭介Calculator的啟動與界面,接著分別介紹Calculator的各個模塊與使用方法。考慮到PDK版權問題,所有數值的結果均進行遮擋或者打碼處理,請見諒。

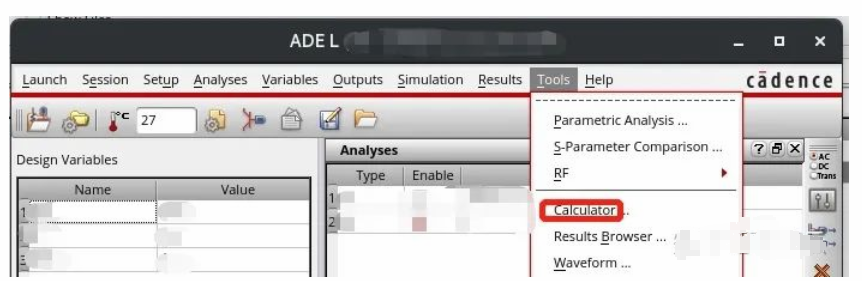

1. Calculator的啟動與界面

ADE L --> Tools --> Caculator

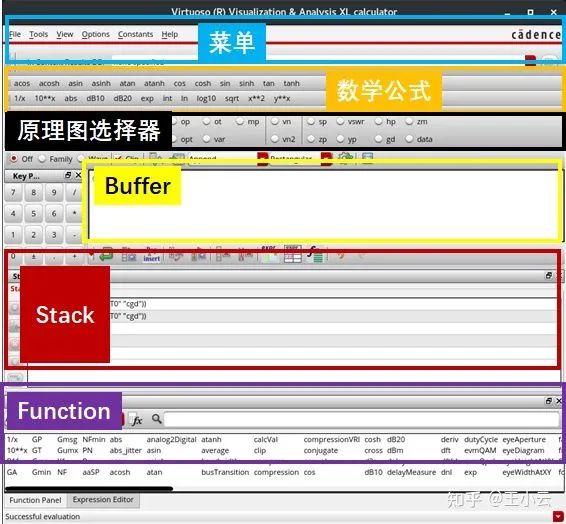

Calculator的界面由上至下分為以下幾個板塊,如圖2所示。圖2的界面可能與大家的界面不完全相同,這是因為我在View里面修改了設置。

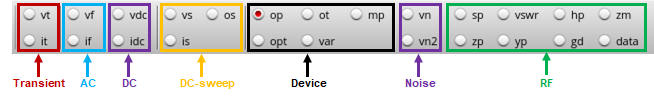

“數學公式”比較簡單,在此我就不做過多介紹了。下面,我會對其他版塊進行逐一的介紹。

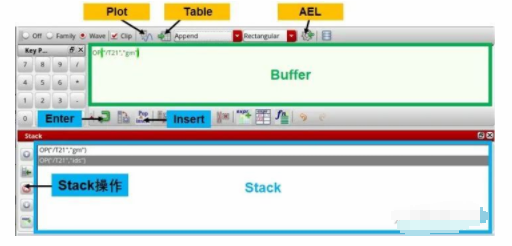

2. Buffer與Stack

Buffer和Stack是最為常用的板塊之一,它們存儲了你“輸入數據”和“表達式”。下面以“晶體管T21的直流工作點ids”為例講解功能,如圖3所示。

2.1 繪制曲線

點擊圖3所示“Plot”按鈕,即可繪制“ids”曲線。

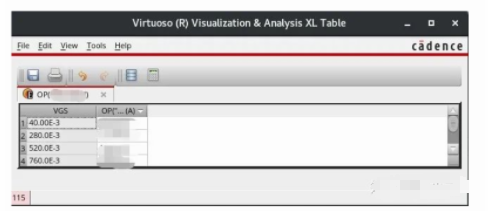

2.2 生成Table

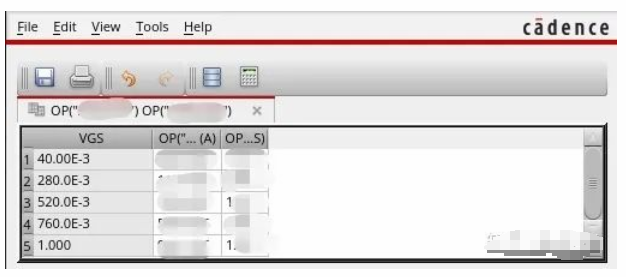

點擊圖3所示的“Table”按鈕,可生成如圖4所示的Table。第一列是參數掃描的變量“VGS”,第二列是晶體管T21的“ids”。

2.3 導出Table

在圖4界面,File --> export (可以選擇.csv)

之后可通過Matlab,Origin等軟件進行處理或者繪圖

2.4 生成多欄Table

保持圖4中的Table打開

回到圖3,在Buffer中輸入晶體管T21的跨導表達式。

OP("/T21","gm")

接著點擊圖3中的“Table”按鈕,即可生成如圖5所示的多欄Table。新增加的第三列就是晶體管“T21”的跨導。

備注:“Table”按鈕右側選擇“Append”才會添加新列,如果是“Replace”則是進行替換。

2.5 表達式送入AEL

點擊圖3所示的“AEL”按鈕,可將“Buffer”中的表達式送入AEL。

2.6 Buffer與Stack交互

點擊圖3中的“Enter”按鈕,可將“Buffer”中的表達式送入“Stack”。

點擊圖3中的“Insert”按鈕,可將“Stack”中的表達式送入“Buffer”。

2.7 Stack內部操作

點擊圖3中“Stack操作”,我們可以對“Stack”內部存儲的表達式進行“添加”,“刪除”,和“順序”調整。

3. 原理圖選擇器

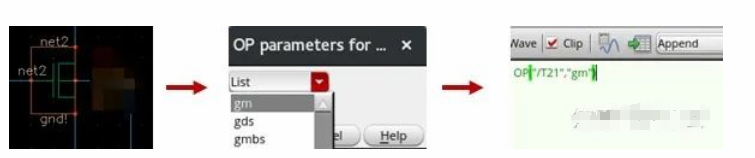

我們可以通過如圖6所示的“原理圖選擇器”在原理圖中選擇我們感興趣的“元件”,“電壓”和“電流”并將表達式送入“Buffer”。

我們以晶體管直流工作點“op”為例。點擊op --> 自動跳轉原理圖 -->選擇T21晶體管 --> 自動彈出List --> 選擇gm --> 表達式進入“Buffer”,如圖7所示。

4. 菜單

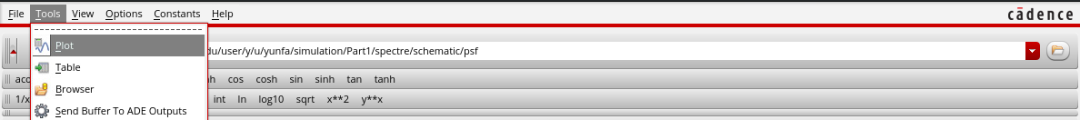

4.1 Tools

如圖8所示為“Tools”的功能。我已在第二節中進行了詳細介紹。

圖8. Tools

圖8. Tools

4.2 Views

可以選擇是否顯“數學公式”,“Stack”,“原理圖選擇器”等板塊。

5 Function

Function的功能十分強大,可以對幾乎所有的電路參數進行計算,可以顯著提升設計效率。

5.1 常用函數

bandwidth(帶寬):放大器設計常用

groupdelay(群時延):系統設計常用

NF(噪聲系數):低噪放設計常用

Phasenoise(相位噪聲):振蕩器設計常用

還有擺率,功率譜密度,jitter等等常用函數都可以找到,使用非常簡單。下面我以其中比較復雜的“上升延遲”舉例。

5.2 舉例“上升延遲”

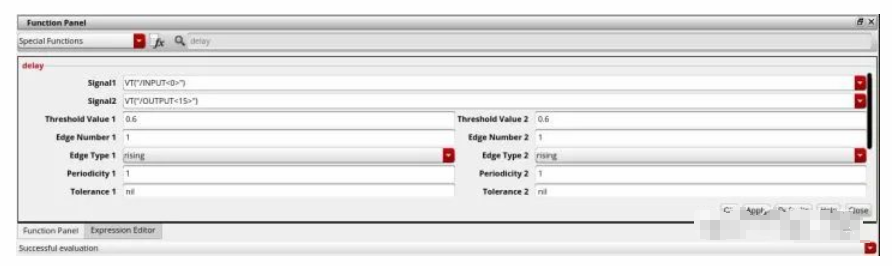

(1)如圖9所示,在“Function”中搜索“delay”并選中

(2)在Signal1和2中分別填入我們所關注的信號

(3)VDD=1.2V,因此我們這里的臨界電壓設置為 0.6 0.6

(4)我們關注的是輸入上升沿到輸出上升沿的延遲,所以選擇“rising”,“rising”。

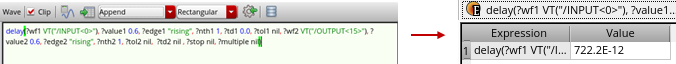

(5)點擊“Apply”,在Buffer中出現如圖表達式,并用Table導出為722.2 ps。

為了論證該結果的正確性,作者用Marker手動獲得了上升延遲。將圖10的結果與公式對比,容易證明是一致的。

-

Cadence

+關注

關注

68文章

1011瀏覽量

146907 -

Calculator

+關注

關注

0文章

6瀏覽量

7008

原文標題:仿真軟件:Cadence中的Calculator使用總結

文章出處:【微信號:yaliDV,微信公眾號:模擬混合信號設計驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Cadence Conformal AI Studio三大核心引擎重塑IC驗證

Cadence Conformal AI Studio榮獲2025亞洲金選獎年度最佳EDA獎

Cadence榮膺2025全球電子成就獎之年度EDA/IP/軟件產品獎

今日看點:Cadence宣布收購ChipStack;德州儀器啟用馬六甲第二組裝測試工廠

2025 Cadence 中國技術巡回研討會即將開啟 ——系統設計與分析專場研討會(上海站)

Cadence中Calculator的使用

Cadence中Calculator的使用

評論