系統設計人員正在尋找所有他們能找到的增加內存帶寬和容量的想法,專注于從內存改進到新型內存的所有內容。更高級別的體系結構更改可以幫助滿足這兩種需求,即使內存類型是從 CPU 中抽象出來的。

兩種新的協議正在幫助實現這一目標,即CXL和OMI。但有一個迫在眉睫的問題是,它們是否會共存,或者一個是否會戰勝另一個。

“隨著處理器中CPU內核數量的增長,人們普遍認為希望為CPU內核獲得更多的內存帶寬和內存容量,”Rambus數據中心產品營銷副總裁Mark Orthodoxou說。“人們已經沒有能力添加DRAM頻道了。

雖然這兩個新協議在概念上有一些高級的相似之處,但它們并不相同。但是,對于它們是否真的相互競爭,似乎存在很多困惑。甚至還存在廣泛的誤解,特別是關于OMI的誤解。

如今,每個人都專注于數據,無論是不斷增長的數據量還是如何最好地管理數據。

”金融服務希望為欺詐檢測添加更多數據源,以提供即時結果,“MemVerge的聯合創始人兼首席執行官Charles Fan說。”社交媒體需要更多的數據源來分析用戶,但提供即時結果。電子商務零售商想要更多的數據源,但需要即時建議。芯片正在設計1萬億個晶體管,但它們需要與前幾代產品在同一時間周期內進入市場。基因組研究人員想要更多的細胞數據,但他們希望縮短疫苗發現的時間。

所有這些都需要更多的內存來為更多的計算提供服務。“在未來兩年內,需要增加一千倍的計算量和一百倍的內存,”范說。

內存和存儲

現代計算系統具有兩層內存結構。有工作內存,它是處理器的本地內存,用于快速訪問,它通常是某種形式的DRAM。然后是存儲,一種內存形式,它在邏輯上并且通常在物理上遠離處理器。這通常是非易失性存儲器,如閃存甚至硬盤驅動器。

這種安排反映了功能、成本和訪問的混合。“內存”往往是更快的技術,盡管成本高于存儲技術。即使考慮到速度,它也不夠快,無法跟上現代處理器的步伐,這就是為什么處理器上的SRAM緩存對性能如此重要的原因。

“存儲”往往由非常高容量的存儲器組成,這些存儲器在每位基礎上非常便宜。但是它們的訪問時間可能比DRAM可以提供的時間慢幾個數量級。

在過去十年中,存儲類內存的討論很多,它具有存儲的一些特征,但具有內存的性能。MRAM,RMRAM和PCRAM是這種交叉類別的典型代表 - 在研究周期的早期還有其他想法。

將單一技術同時用于存儲器和存儲的承諾是誘人的,但它將為芯片設計人員創建需要與存儲器接口的IC帶來一些挑戰。大多數芯片都有用于DRAM的特定接口。如果您可以使用MRAM或RRAM,那么您將CPU連接到哪個接口?這些存儲器可能都具有不同的訪問協議。

存儲有不同的挑戰,但內存類型的激增造成了類似的困境。此外,存儲中的數據通常必須批量檢索才能實際使用。該復制操作需要時間并消耗能量。

這兩種情況都將受益于一種抽象出所使用的特定存儲器的細節的方法,這樣芯片設計人員以及在某種程度上的軟件開發人員都不必那么關心特定系統的存儲器細節。它還可能使軟件在不同系統之間更具可移植性,這在數據中心特別有價值。

如今,它需要更高級別的程序或系統來管理和構建不同內存和存儲資源的池。這種“大內存”程序提供了一種增加內存帶寬和容量的方法。

“圍繞大內存計算的論點是,與其不斷努力使存儲越來越快,不如利用其他新硬件,并輔以正確的軟件集,”范說。“我們可以構建一個軟件定義的內存池,該內存池可以成為應用程序需要處理的所有活動數據的平臺,從而減少或消除活動應用程序數據的內存和存儲之間的數據傳輸。

CXL 和 OMI 協議都提供抽象,盡管級別較低。但作為新興的解決方案,很容易將兩者混淆。OMI在網上幾乎沒有大張旗鼓的方式,對它的認識似乎低于對CXL的認識。根據你和誰交談,他們做或不做同樣的事情,因此做或不互相競爭。

CXL和/或OMI的出現并不一定影響大內存管理系統的使用。相反,它使物理內存連接更容易處理。”我們依靠CPU使用其接口/內存管理器訪問內存,因此我們的軟件與內存互連無關,包括CXL,OMI和DDR4 / 5,“Fan說。

CPU使用的近內存和OMI

工作內存需要快速。多年來,DRAM一直提供最佳的速度/成本組合,并且隨著技術的發展,DRAM似乎可能會繼續這樣做。即便如此,還是有辦法提高這種性能,但要付出代價。

DRAM的致命弱點是一組驅使記憶的長線。它們的高電容使得很難繼續推動更高的內存速度并添加更多內存。

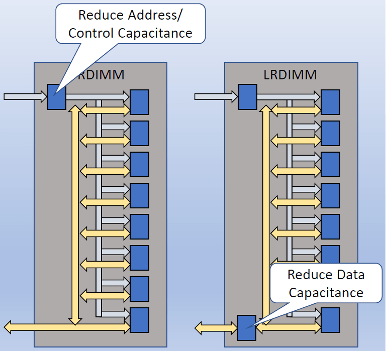

兩種變體有所幫助。一個是RDIMM,其中地址和控制信號在芯片上緩沖。這加快了這些信號的速度,同時保留了數據信號。LRDIMM還通過緩沖數據更進一步。這增加了延遲的時鐘周期,但加快了線路速度并允許更多內存。

圖1:RDIMM緩沖地址和控制信號;LRDIMM 還緩沖數據信號。其目的是擁有更短,更少的電容線路和更快的訪問,但代價是額外的時鐘周期延遲。

但是用于訪問的端口需要許多引腳 - LRDIMM的每個通道152個,Objective Analysis的Jim Handy在去年的Hot Interconnects會議上的一次演講中說。八個通道將花費1,216個引腳。

”由于引腳數量非常大,因此驅動這些引腳所需的面積很大,因為它是并行接口,“Orthodoxou說。

HBM 是另一種提供更高訪問速度的替代方案。雖然價格昂貴,但它提供了最高的帶寬。但它的總線是1000位寬。還有其他挑戰,在關于OMI的白皮書中有所描述。

”雖然HBM是一個幫助,但它比標準DRAM貴得多,并且僅限于不超過12個芯片的堆棧,將其使用限制在低容量內存陣列上,“該論文說。”HBM 也很復雜和不靈活。在現場無法升級基于 HBM 的內存。因此,HBM 內存只在沒有其他解決方案可用的情況下才被采用。

OMI從OpenCAPI世界中出現,為了延遲,OMI規范被分離出來。它旨在通過兩種方式解決這些近內存挑戰 - 遷移到SerDes,以及使用DIMM控制器。用于 OMI 通道的 DIMM 被稱為差分 DIMM 或 DDIMM。

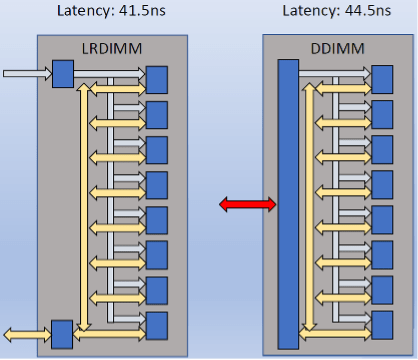

SerDes連接將取代當前的DDR式接口,以更少的信號提供更高的速度。控制器部分提供與LRDIMM上的寄存器相同的功能,在此過程中將總內存延遲增加約4ns。

“OMI延遲包括通過內存本身的延遲,這是從內部連接到主機中的傳輸端口回到主機中接收的內部連接的往返讀取延遲,”OpenCAPI聯盟的技術總監兼董事會顧問Allan Cantle說。

圖 2:LRDIMM 與 DDIMM 的比較。DDIMM左側的藍色框是控制器。延遲增加幾納秒。

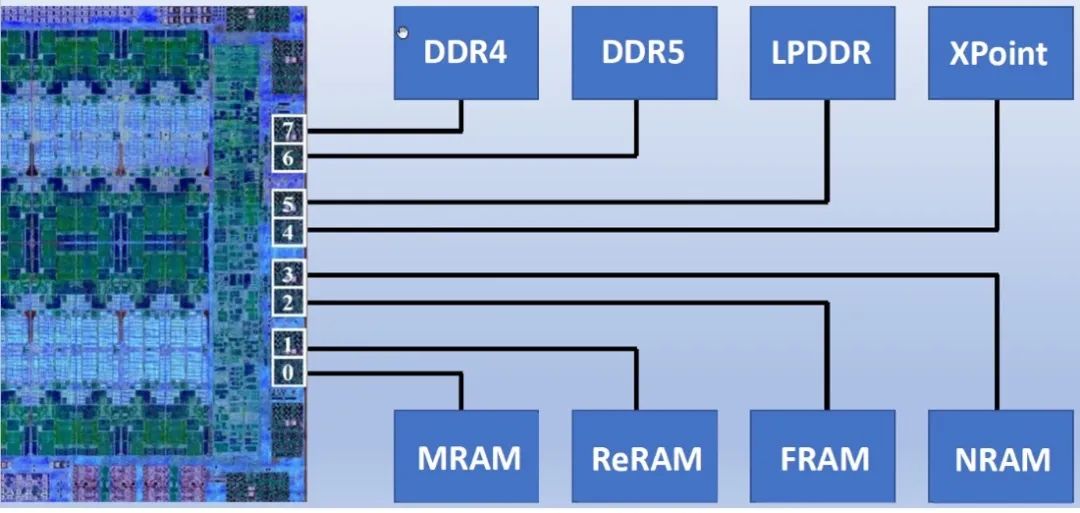

此外,控制器還可以連接到許多不同類型的內存。它充當該內存和處理器之間的橋梁。就處理器而言,所有內存看起來都像 OMI,除此之外的細節都在 DDIMM 上處理。

這允許系統構建商混合和匹配正在使用的內存類型。每個通道都可以是其自己的內存類型。事實上,只要控制器支持,單個 DDIMM 就可以混合使用內存。

圖 3:混合內存系統的概念示例,其中每個通道使用不同的內存技術。

然而,目前還不清楚系統是否真的會以這種方式組成。有些人認為,抽象的價值不在于創建異構內存池,而在于使具有一組接口的單個 CPU 可以訪問由任何這些類型的內存構建的同構池。

“近內存將始終是同構存儲器的更多選擇,而不需要抽象異構存儲器類型,”西門子EDA驗證IP產品經理Gordon Allan說。

帶寬將高于標準DRAM接口,盡管HBM仍然會更快。也就是說,擁有更少的引腳意味著SoC上用于存儲器通道所需的硅將小得多,這使得OMI在帶寬/面積上與HBM更具競爭力。由于接口占用空間較小,如果 OMI 可以使用的通道多于其他接口,則聚合帶寬可能會更高。

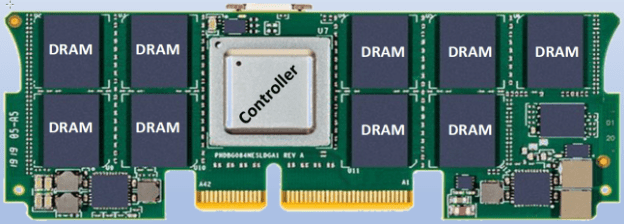

為了完全出現這種新范式,首先需要控制器芯片,然后需要DDIMM可用。這一進程已經開始,但還有很長的路要走。即便如此,到目前為止,OMI的吸收速度一直很慢。

圖 4:顯示控制器和多個 DRAM 芯片的 DDIMM。還提供2U版本。資料來源:OpenCAPI Consortium

“我們沒有與客戶要求我們提供這項技術,但對于OMI來說,現在還為時尚早,”艾倫說。“這是IBM和其他一些公司推廣的相對較新的進入者。它仍然沒有在業界被廣泛采用,但肯定有很多人對它感興趣,因為它聲稱要擴展DDR的容量優勢和HBM的性能帶寬優勢。但在這一點上,這仍然是一個大膽的,未經證實的說法。

遠內存和CXL

遠內存的情況更為復雜。除了與特定類型的內存相關的問題之外,頻繁需要復制大塊內存也是一個重大問題,特別是對于機器學習等內存或存儲密集型應用程序,尤其是在數據中心。

這些是CXL解決的問題。”CXL 優化和虛擬化數據傳輸、存儲和計算,“Synopsys 系統設計組工程總監 Levent Caglar 說。

這在數據中心應用程序中很有用。”HPC領域由大量的計算結構組成,“Cadence知識產權集團產品營銷集團總監Arif Khan說。”CPU、GPU、加速器、FPGA 等都連接到不斷增長的內存池。CXL 滿足了異構計算的需求,同時保持了緩存的一致性,并允許內存的可擴展性。

但它也很復雜。“我們需要考慮存儲的三個不同方面,”西門子EDA的Allan說。“首先是共置處理器和內存。在處理管道的另一端,我們有相干的內存和存儲鏈接,其中數據必須與其他處理和通信元素共享。此外,我們還對數據中心的存儲進行了更大規模的搜索和檢索。CXL位于這些領域的第二和第三位。

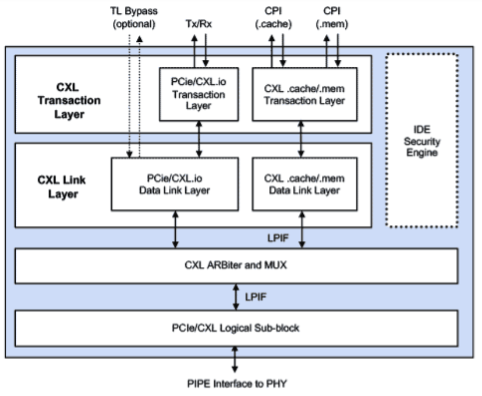

圖 5:CXL 控制器的框圖。CXL 功能依賴于 PCIe 進行物理互連。

CXL在概念上類似于OMI,充當允許處理器與內存類型無關的橋梁。”從系統其余部分的角度來看,該內存在邏輯上盡可能接近CPU,“Caglar說。

但CXL的職權范圍比OMI要廣泛得多,需要涵蓋的用例要多得多。”OMI和CXL在它們試圖解決的近內存問題方面非常相似,“Orthodoxou說。”他們的不同之處在于CXL試圖解決遠內存問題。

審核編輯 :李倩

-

芯片

+關注

關注

463文章

54007瀏覽量

465935 -

cpu

+關注

關注

68文章

11277瀏覽量

224949 -

存儲

+關注

關注

13文章

4787瀏覽量

90057

原文標題:CXL和OMI:競爭還是互補?

文章出處:【微信號:TenOne_TSMC,微信公眾號:芯片半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瀾起科技發布PCIe 6.x/CXL 3.x AEC解決方案

Penguin Solutions SMART Modular CXL NV-CMM E3.S 2T 內存模塊通過 CXL 兼容性認證

借助CXL和壓縮技術實現高效數據傳輸

SerDes vs. ETH,互補還是競爭?

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能線性轉接驅動器

探索CXL 70 - 5C天線:450 MHz頻段通信的理想選擇

關于CW32 互補PWM 程序調試的疑問求解

紫光國芯榮獲2025年度CXL產品技術創新獎

瀾起科技推出CXL? 3.1內存擴展控制器,助力下一代數據中心基礎設施性能升級

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

Arm Neoverse CMN S3 推動Compute Express Link (CXL) 存儲創新

CXL和OMI:競爭還是互補?

CXL和OMI:競爭還是互補?

評論