解析DS320PR822:PCIe 5.0和CXL 1.1的高性能線性轉接驅動器

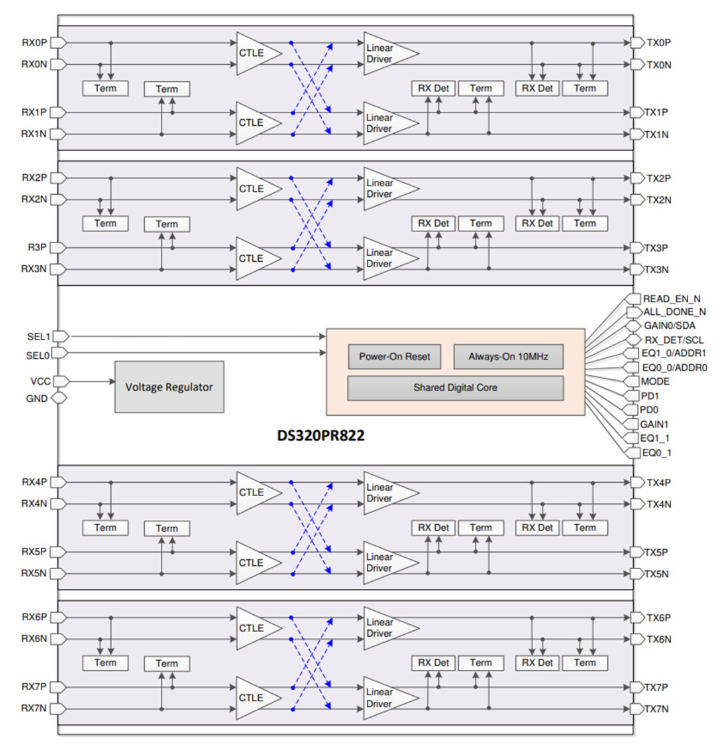

在高速數據傳輸領域,PCIe 5.0、CXL 1.1等接口技術的發展對信號傳輸的質量和穩定性提出了更高要求。DS320PR822作為一款專為支持這些高速接口而設計的線性轉接驅動器,具有諸多卓越特性。本文將深入剖析DS320PR822的特性、應用、電氣參數等方面,為電子工程師在實際設計中提供有價值的參考。

文件下載:ds320pr822.pdf

特性亮點

高速接口支持

DS320PR822支持PCIe 5.0、CXL 2.0、UPI 2.0等速率高達32 Gbps的接口,同時還支持大多數交流耦合接口,如DP、SAS、SATA、XFI等,展現出了強大的兼容性和通用性。

均衡與低延遲設計

接收器部署了連續時間線性均衡器(CTLE),可提供可編程高頻增強功能,打開因互連介質引起的碼間串擾而關閉的輸入眼圖。CTLE在16GHz下可升至22dB,且具有100 ps的超低延遲和PRBS數據的75 fs低附加隨機抖動,以及16GHz時 -10dB的極低回波損耗,能有效改善信號質量。

低功耗與抗干擾能力

該器件采用3.3V單電源,內部穩壓器具有抗電源噪聲能力,每通道有功功率僅160mW,無需散熱器。數據路徑使用內部穩壓電源軌,高度抵抗板上的各種電源噪聲,保證了在復雜電磁環境下的穩定工作。

靈活配置方式

提供引腳搭接、SMBus或EEPROM編程三種配置方式,還具備針對PCIe用例的自動接收器檢測功能,與協議無關的線性轉接驅動器可無縫支持PCIe鏈接訓練,通過一個或多個DS320PR822支持x2、x4、x8、x16、x24總線寬度,滿足不同應用場景的需求。

引腳功能解析

DS320PR822共有64個引腳,各引腳功能明確且多樣。例如,ALL_DONE_N引腳在SMBus/I2C Primary模式下指示EEPROM寄存器加載操作的完成情況;MODE引腳可設置設備控制配置模式,有5種不同的電平設置可供選擇;EQ和ADDR系列引腳在不同模式下分別用于設置接收器線性均衡器(CTLE)的增益和SMBus / I2C的二次地址。這些引腳的合理配置是實現器件各項功能的關鍵。

電氣參數詳解

絕對最大額定值

規定了器件在不同參數下的最大承受范圍,如電源電壓(VCC)在 -0.5V至4.0V之間,超出這些范圍可能導致器件永久損壞。

ESD額定值

人體模型(HBM)為±2000V,帶電設備模型(CDM)為±500V,表明了器件在靜電防護方面的能力。

推薦工作條件

明確了電源電壓、電源噪聲容限、工作溫度等參數的推薦范圍,確保器件在正常工作時能夠達到最佳性能。

直流和高速電氣特性

涵蓋了功率消耗、控制IO的電壓和電流特性、接收器和發射器的電氣參數等多個方面。例如,在不同的EQ和GAIN設置下,器件的平坦增益和EQ增益會有所不同,工程師需要根據實際應用需求進行合理調整。

功能模塊與工作模式

線性均衡功能

DS320PR822的接收器采用連續時間線性均衡器(CTLE),通過高頻提升和低頻衰減來均衡無源通道的頻率相關插入損耗。在Pin模式下,EQ引腳可設置不同通道的均衡增益;在SMBus/I2C模式下,各通道可獨立編程,實現更精細的控制。

扁平增益控制

GAIN引腳可設置器件的扁平增益,在Pin模式下,不同的電平設置對應不同的增益值;在I2C模式下,每個通道也可獨立設置。同時,需要注意輸出信號的擺幅應在器件的線性范圍內,以保證信號的質量。

接收器檢測狀態機

該器件部署了Rx檢測狀態機,可根據不同的引腳設置確定是否存在有效的PCI Express終端。在PCIe應用中,PD0/1引腳可與PCIe側帶信號連接,實現所需的RX檢測功能。

交叉點功能

提供四個2x2交叉點多路復用器功能,通過SEL引腳可選擇信號路徑為直連或交叉連接,在所有設備控制模式下均有效。

工作模式

- Active PCIe Mode:PCIe狀態機啟用,PD0和PD1引腳驅動為低,用于重驅動和均衡PCIe信號,提高信號完整性。

- Active Buffer Mode:PCIe狀態機禁用,適用于非PCIe應用,作為緩沖器提供線性均衡。

- Standby Mode:PD1和PD0引腳為高,器件進入待機模式,節省功耗。

編程與配置

引腳模式

通過2級和5級引腳對器件進行控制和信號完整性優化設置。其中,8個5級輸入引腳使用電阻分壓器設置有效電平,外部電阻需具有10%或更好的公差。

SMBUS/I2C寄存器控制接口

當MODE = L2時,通過標準I2C或SMBus接口進行配置,接口速率可達400 kHz。DS320PR822有共享寄存器和通道寄存器兩種類型,分別用于設備級配置和各通道的獨立配置。

SMBus/I2C Primary模式配置

將MODE引腳設置為L1,器件可從EEPROM讀取配置信息。EEPROM加載操作在設備首次上電后僅進行一次,完成后ALL_DONE_N引腳將變為低電平。

應用與設計要點

典型應用場景

DS320PR822可用于機架式服務器、微服務器、塔式服務器、高性能計算、硬件加速器、網絡連接存儲、存儲區域網絡(SAN)和主機總線適配器(HBA)卡、網絡接口卡(NIC)、臺式計算機或主板等多種領域,還可用于實現PCI Express x2、x4、x8、x16等不同總線寬度的2x2交叉點配置。

UPI x24通道交叉點配置

設計要求

在與PCIe CEM連接器接口時,使用85Ω阻抗的走線,對差分對的P和N走線進行長度匹配;采用均勻的走線寬度和間距;在每個通道段的接收器端附近放置交流耦合電容,推薦使用220nF的電容;對連接器過孔和信號過孔進行背鉆,以減少殘樁長度;使用參考平面過孔確保低電感的回流路徑。

詳細設計步驟

將DS320PR822放置在CPU Tx和CPU Rx之間,保證器件輸出引腳的信號擺幅在其線性范圍內。根據通道損耗調整EQ設置,以優化接收端的眼圖。在SMBus/I2C模式下,需使用上拉電阻將SCL和SDA引腳連接到3.3V電源。

應用曲線分析

通過對比有無DS320PR822的PCIe 5.0鏈路,發現該器件能夠將鏈路的總通道損耗從36dB擴展到58dB,實現約22dB的延伸能力,但實際延伸效果受多種信號完整性因素影響,建議進行信號完整性仿真。

電源與布局建議

電源設計

電源應滿足推薦工作條件中的直流電壓、交流噪聲和啟動斜坡時間要求。無需特殊的電源濾波,僅需標準的電源去耦,包括每個VCC引腳的0.1μF電容、每個器件的1.0μF大容量電容和每個電源總線的10μF大容量電容。同時,電壓調節器輸出引腳需在附近使用0.1μF的去耦電容。

布局設計

- 去耦電容應盡量靠近VCC引腳,若電路板設計允許,可放置在器件正下方。

- 高速差分信號應緊密耦合、偏斜匹配并進行阻抗控制,盡量避免使用過孔,若必須使用,需采取措施減少過孔殘樁。

- 可在高速差分信號焊盤下方使用GND relief來改善信號完整性,同時在器件正下方放置GND過孔,以提高熱導率。

DS320PR822以其高性能、低功耗、靈活配置等特點,為高速數據傳輸應用提供了優秀的解決方案。電子工程師在設計過程中,需充分理解其特性、電氣參數、功能模塊和應用要點,結合實際需求進行合理的配置和布局,以確保系統的穩定性和可靠性。在實際應用中,你是否遇到過類似高速接口設計的挑戰?又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

高速接口

+關注

關注

1文章

76瀏覽量

15321

發布評論請先 登錄

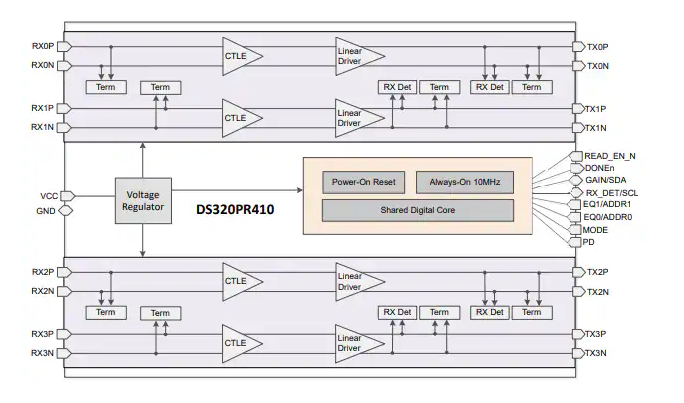

DS320PR410支持PCIe5.0、CXL 2.0的四通道線性轉接驅動器數據表

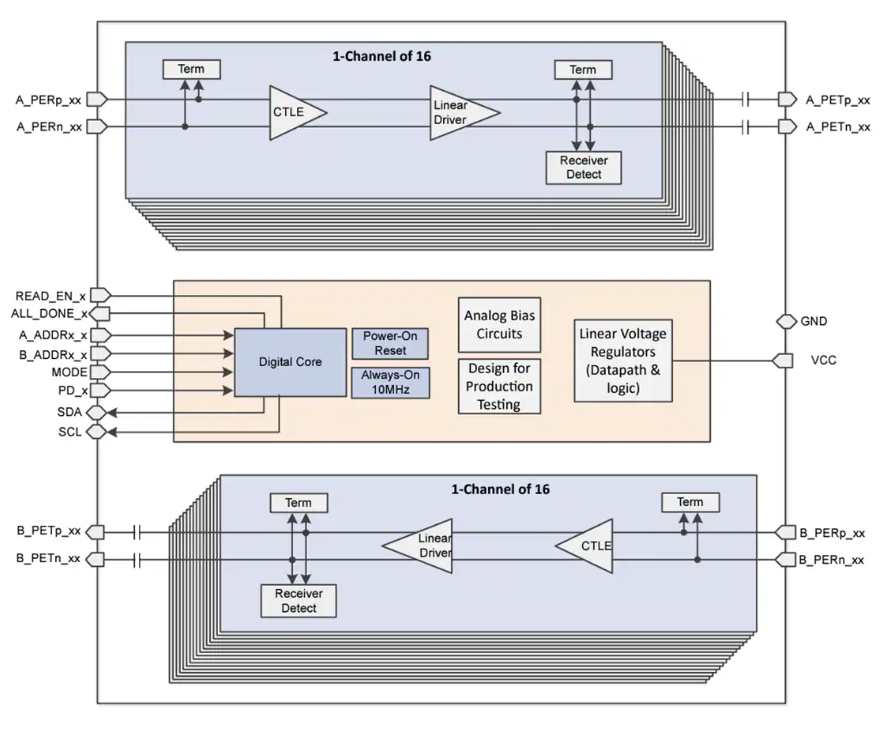

DS320PR1601 32Gbps 16通道PCIe 5.0、CXL 2.0線性轉接驅動器數據表

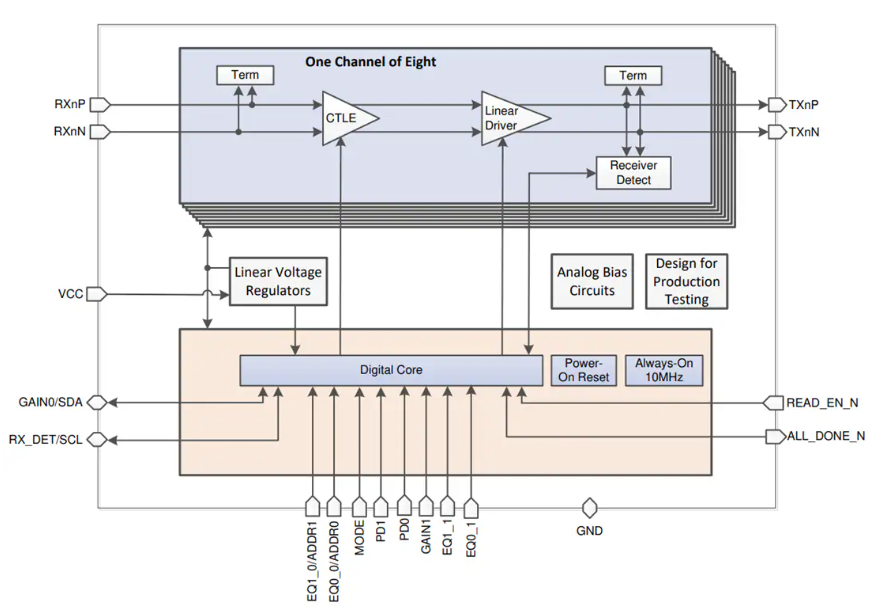

DS160PR822 PCIe 4.0 16Gbps 8通道線性轉接驅動器數據表

DS320PR822用于PCle 5.0、CXL 1.1的線性驅動器數據表

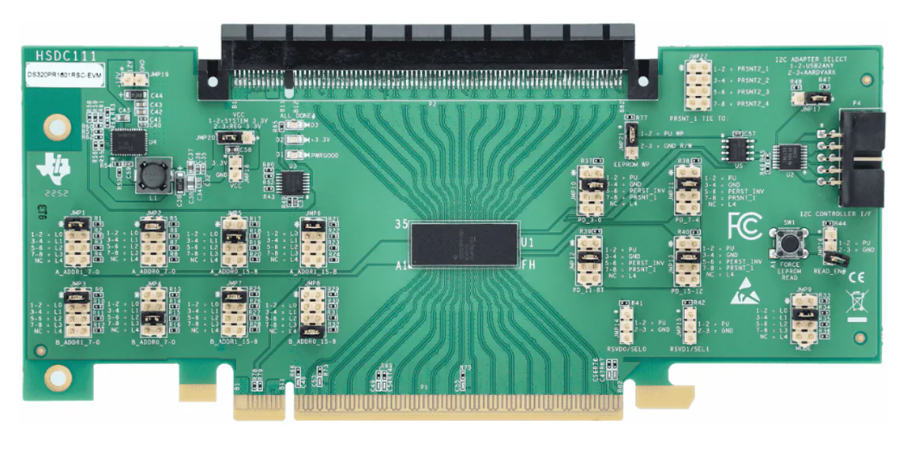

DS320PR1601RSC-EVM線性轉接驅動器評估模塊技術解析

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能線性轉接驅動器

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能線性轉接驅動器

評論