1、綜合-優化資源

當選擇為none,綜合器優化的最少,當選擇為full時,綜合器優化的最多,選擇rebuilt時,工具自動選擇一個折中的方案,對當前工程做優化。如果在rebuilt的選項不希望一些信號被優化,則可以調用原語進行約束。

對于模塊,想保留該模塊的層次結構

(* keep_hierarchy=“yes” )

對于信號,在實際使用中,最好作用于寄存器,有的wire即使約束,也會被優化。

( keep=“true” )

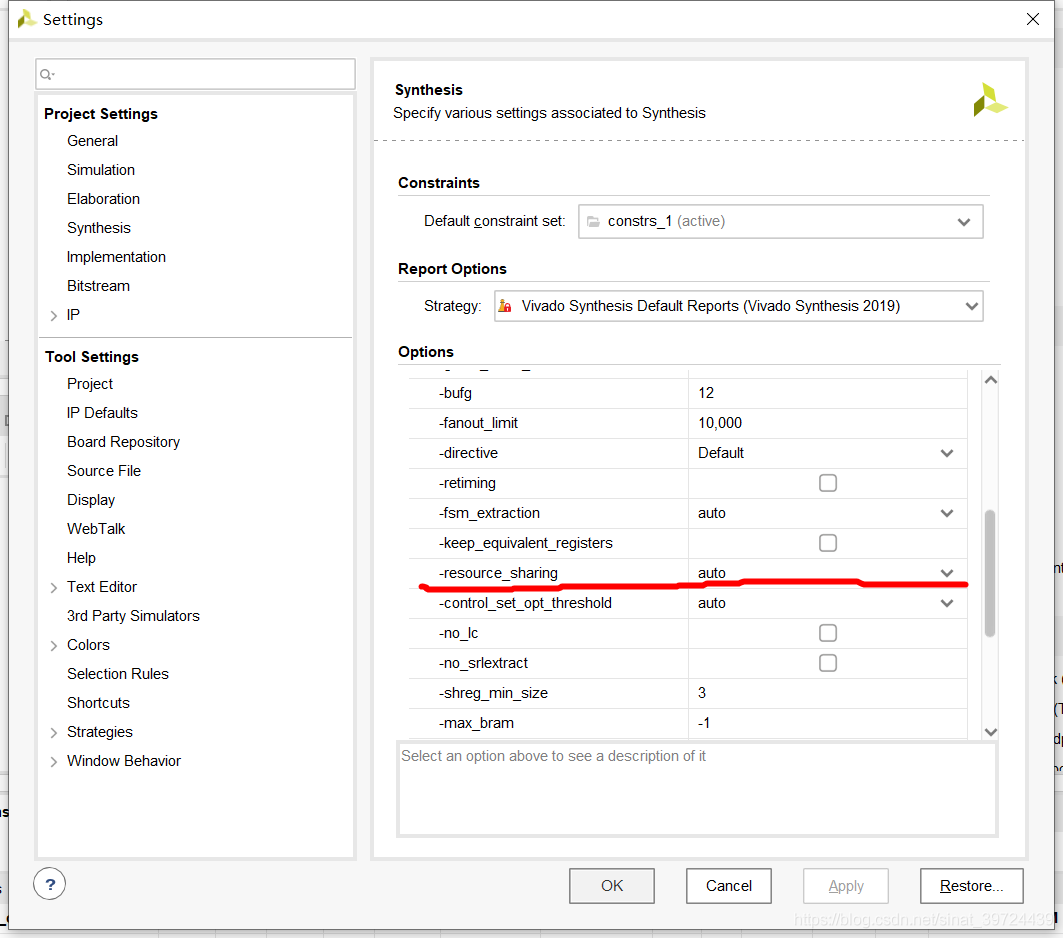

2、綜合-資源共享

當選擇為on時,使能資源共享,當選擇為off時,關閉資源共享,當選擇為auto時,綜合器會根據時序的余量自動選擇是否啟動資源共享。

注意,此此選項只對當前代碼中加減乘有影響。

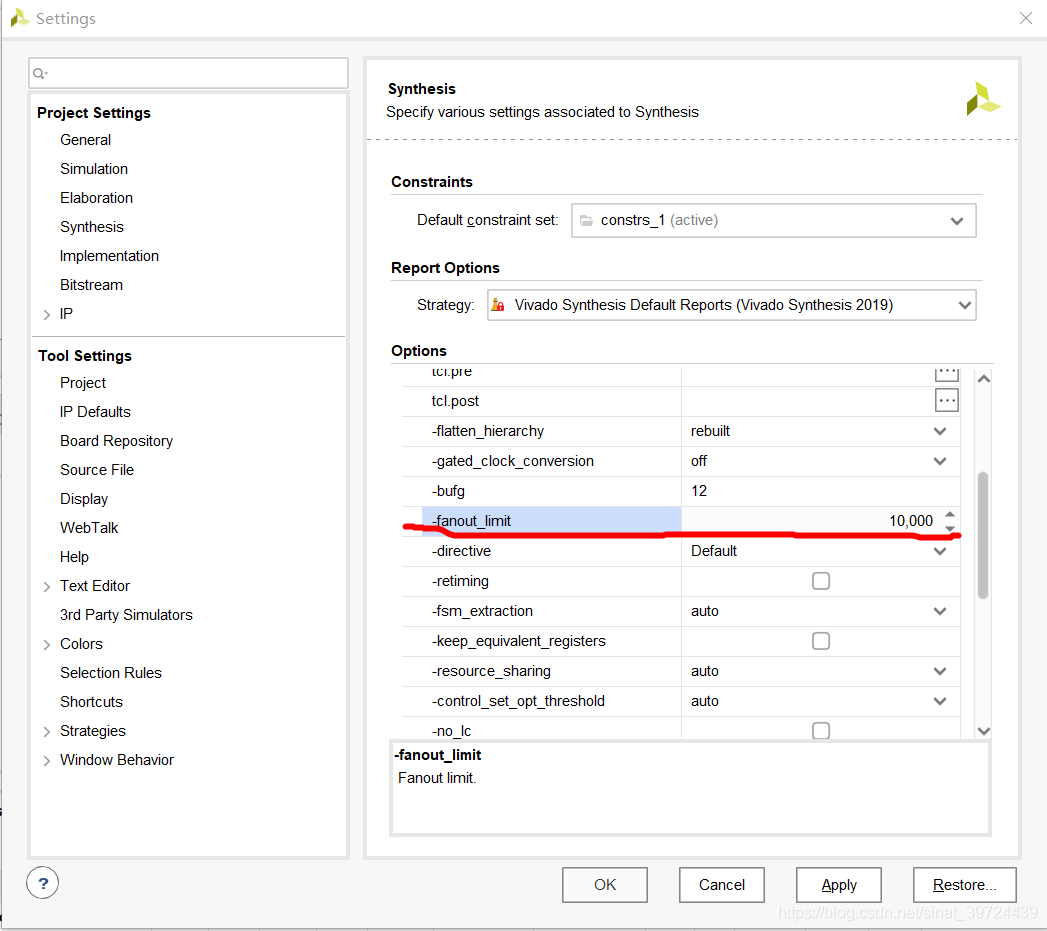

3、綜合-扇出限制

默認是10000,這只是一個籠統的全局設置,對復位無效。

對于單一信號的扇出約束,使用約束

( max_fanout= *)

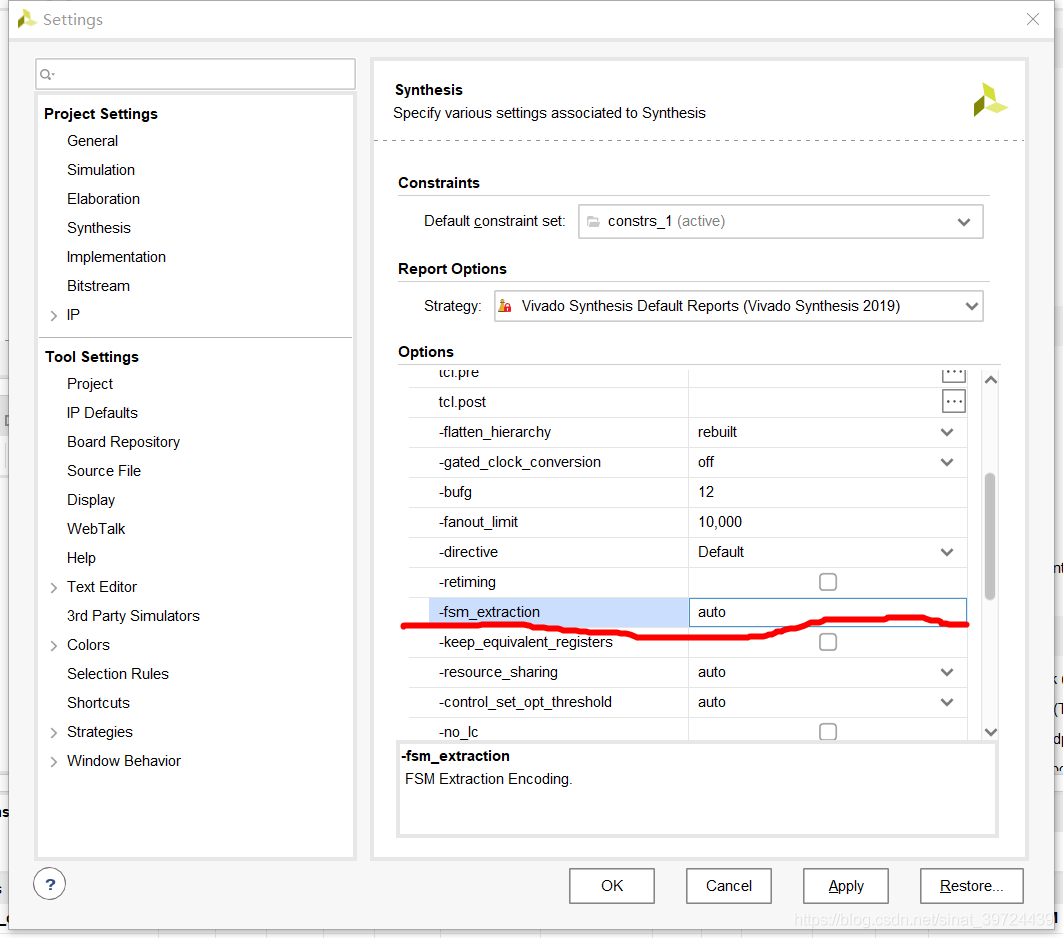

4、狀態機的編碼方式

當選擇為auto時,綜合器會根據當前的代碼,自動選擇最有的編碼方式。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Vivado

+關注

關注

19文章

857瀏覽量

71111

發布評論請先 登錄

相關推薦

熱點推薦

蜂鳥E203 ARTY綜合時出現的unconnected問題怎么解決?

大家好,我嘗試用make bit生成bit文件,在vivado綜合日志中出現很多模塊has unconnected port,只是warning可以成功生成bit文件。在相關模塊的例化文件中發現這些模塊的對應port沒有給出連接,想問下這些port是不必要并不影響模塊的使

發表于 11-10 07:28

開源RISC-V處理器(蜂鳥E203)學習(二)修改FPGA綜合環境(移植到自己的Xilinx FPGA板卡)

。

vivado加載所有的約束文件,這里需要將舊的文件remove掉,也就是藍框的兩個文件。

進行綜合時,如果提示jtag tck的iobuf錯誤,建議在約束文件中添加如下約束:

set_property

發表于 10-31 08:46

vivado時序分析相關經驗

vivado綜合后時序為例主要是有兩種原因導致:

1,太多的邏輯級

2,太高的扇出

分析時序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

發表于 10-30 06:58

vcs和vivado聯合仿真

我們在做參賽課題的過程中發現,上FPGA開發板跑系統時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado ip核的soc系統進行仿真。在這種情況下

發表于 10-24 07:28

FPGA開發板vivado綜合、下載程序問題匯總

在做vivado綜合時和FPGA下載程序時,我們碰到以下問題,并找出了對應的解決方案。

1.could not open include file”e203_defines.v”問題

在做

發表于 10-24 07:12

Vivado浮點數IP核的一些設置注意點

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一個IP核實

發表于 10-24 06:25

Vivado無法選中開發板的常見原因及解決方法

在使用 AMD Vivado Design Suite 對開發板(Evaluation Board)進行 FPGA 開發時,我們通常希望在創建工程時直接選擇開發板,這樣 Vivado 能夠自動配置

關于交流負載模式中的CF值設置(下)

01CF值設置在不同發布平臺的關注點(一)學術發布平臺在學術平臺上,關于交流負載模式中CF值設置的研究成果主要關注理論分析和實驗驗證。研究人員會深入探討CF值與負載特性、電路參數之間的數學關系,通過

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結果(以 Vivado 2024.2 為例)。

一文詳解Vivado時序約束

Vivado的時序約束是保存在xdc文件中,添加或創建設計的工程源文件后,需要創建xdc文件設置時序約束。時序約束文件可以直接創建或添加已存在的約束文件,創建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在

e203在vivado硬件里自定義指令識別為非法指令怎么解決?

e203自定義指令硬件模塊設計,修改內核,綜合沒錯誤,軟件也修改工具鏈通過并產生verilog文件,但在vivado硬件里自定義指令識別為非法指令怎么解決

發表于 03-07 07:34

關于Vivado綜合設置使用總結

關于Vivado綜合設置使用總結

評論