在我之前寫的FPGA時(shí)序約束教程中,有一篇中講到了虛擬時(shí)鐘:

FPGA時(shí)序約束理論篇之時(shí)鐘周期約束

但文中對(duì)虛擬時(shí)鐘的應(yīng)用介紹的還不夠詳細(xì),因此這里我們?cè)賹?duì)虛擬時(shí)鐘做一個(gè)更加細(xì)致的介紹。

首先,虛擬時(shí)鐘用于什么地方?

虛擬時(shí)鐘通常用于設(shè)定輸入和輸出的延時(shí),即set_input_delay和set_output_delay。可能有同學(xué)忘記這兩個(gè)約束的用法了,這里我們?cè)僬故疽幌拢?/p>

set_input_delay 0.5 -clock clkA [get_ports A] set_output_delay 1 -clock clkB [get_ports B]

其中clkA和clkB就是我們使用create_clock創(chuàng)建的主時(shí)鐘或者虛擬時(shí)鐘。

主時(shí)鐘在創(chuàng)建的時(shí)候需要指定時(shí)鐘輸入端口,虛擬時(shí)鐘不需要指定端口,所以稱之為虛擬時(shí)鐘。那什么場景下要用到虛擬時(shí)鐘呢?

1. 外部IO的參考時(shí)鐘并不是設(shè)計(jì)中的時(shí)鐘

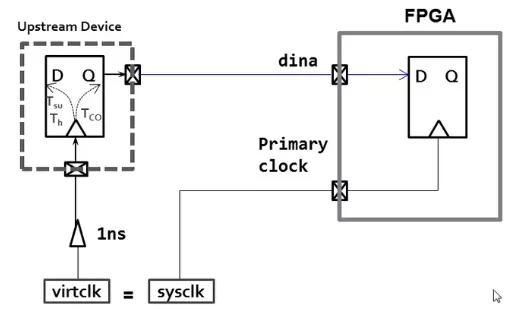

下圖中,外部IO的參考時(shí)鐘比設(shè)計(jì)中主時(shí)鐘的路徑上多了一個(gè)BUFFER,因此我們需要使用虛擬時(shí)鐘來進(jìn)行約束。

create_clock -name sysclk -period 10 [get_ports clkin] create_clock -name virtclk -period 10 set_clock_latency -source 1 [get_clock virtclk] set_input_delay -clock virtclk -max 4 [get_ports dina] set_input_delay -clock virtclk -min 2 [get_ports dina]

2. FPGA I/O路徑參考時(shí)鐘來源于內(nèi)部衍生時(shí)鐘,但與主時(shí)鐘的頻率關(guān)系并不是整數(shù)倍

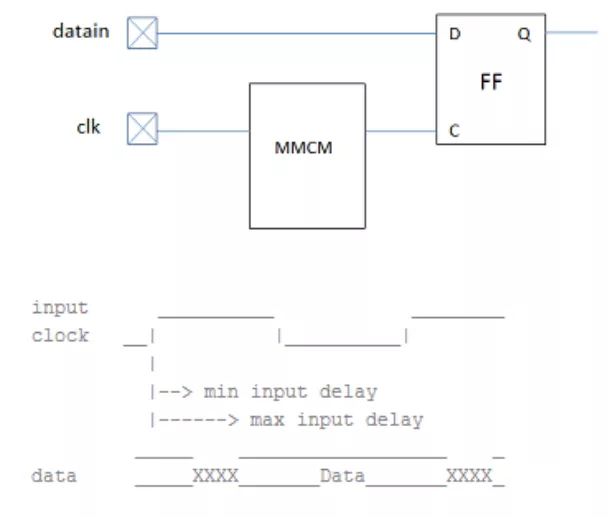

如果I/O路徑參考時(shí)鐘源于內(nèi)部的衍生時(shí)鐘,那set_input_delay和set_output_delay約束中-clock參數(shù)后的時(shí)鐘不能是衍生時(shí)鐘,比如下圖的例子中,輸入10MHz時(shí)鐘經(jīng)過了MMCM后去采輸入的數(shù)據(jù)。

a) 如果MMCM沒有負(fù)的相移而且輸出的頻率也是10MHz,那么直接使用主時(shí)鐘來約束input delay。

create_clock -period 100.000 -name clk [get_ports clk] set_input_delay -clock clk -max 2.000 [get_ports datain] set_input_delay -clock clk -min 1.000 [get_ports datain]

b) 如果MMCM輸出頻率是60MHz,那么這個(gè)衍生時(shí)鐘跟主時(shí)鐘并不是整數(shù)倍關(guān)系,這時(shí)就需要用到虛擬時(shí)鐘了

create_clock -period 100.000 -name clk [get_ports clk] create_clock -name clk_port_vclk -period 16.67 set_input_delay -clock clk_port_vclk -max 2 [get_ports datain] set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]

3. 在不修改時(shí)鐘特性的情況下針對(duì)I/O指定不同的jitter和latency

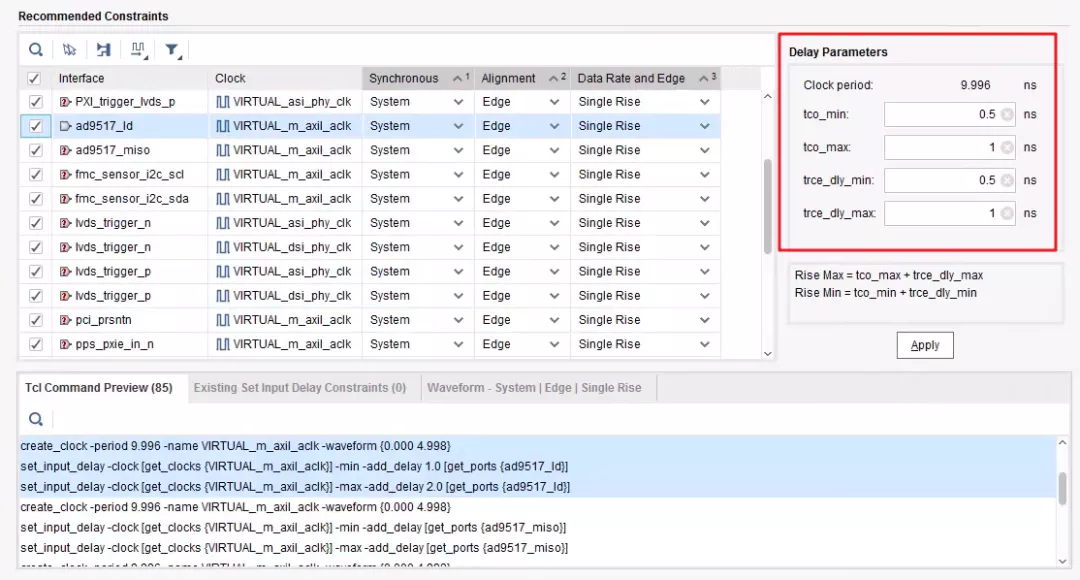

在設(shè)置完成后,可以看到Tcl Command Preview中提示的約束指令。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1660文章

22411瀏覽量

636266 -

端口

+關(guān)注

關(guān)注

4文章

1104瀏覽量

33963 -

虛擬時(shí)鐘

+關(guān)注

關(guān)注

0文章

5瀏覽量

6703

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx FPGA中IDELAYCTRL參考時(shí)鐘控制模塊的使用

ups電源的作用和使用方法詳解

易靈思FPGA DSP原語使用方法

數(shù)字IC/FPGA設(shè)計(jì)中的時(shí)序優(yōu)化方法

堆棧的定義,堆棧的使用方法

開源RISC-V處理器(蜂鳥E203)學(xué)習(xí)(二)修改FPGA綜合環(huán)境(移植到自己的Xilinx FPGA板卡)

條碼掃碼設(shè)備的使用方法

錫膏的儲(chǔ)存及使用方法詳解

LCR測試儀的使用方法與注意事項(xiàng)

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

PXI-8433/4的規(guī)范使用方法分享

FPGA虛擬時(shí)鐘的使用方法

FPGA虛擬時(shí)鐘的使用方法

評(píng)論