隨著人工智能浪潮席卷全球,AI算力正以前所未有的速度爆發式增長。在這場決定未來的技術競速中,穩定、高效、可靠的電力供應是算力基石的核心。而電容器作為電路中的“能量”來源,在整個AI服務器不見中起到重要作用。

上海永銘電子股份有限公司于2025年10月31日成功舉辦“AI服務器電容應用”專題會議,聚焦前沿領域,深入探討電容技術的創新與應用,攜手行業伙伴共赴算力新時代。

技術鋒芒:精準破解AI服務器電容挑戰

自動化 數字化 智能化

在新廠房,永銘的合作伙伴們實地探訪,親眼見證了永銘自動化產線與數字系統高效運轉、無縫協同的場景。會議現場,永銘總裁講解了自動化產線與數字化系統深度融合所創造的協同新高度。

永銘各類高可靠性電容

在AI服務器中的應用

會議全面深入貫穿AI服務器主供電源、備用電源(BBU)、企業級固態硬盤(SSD)、主板等核心應用場景。議題全方位凸顯了永銘電容器在高功率密度、超低ESR、超長壽命與毫秒級快速響應等方面的技術領先性。

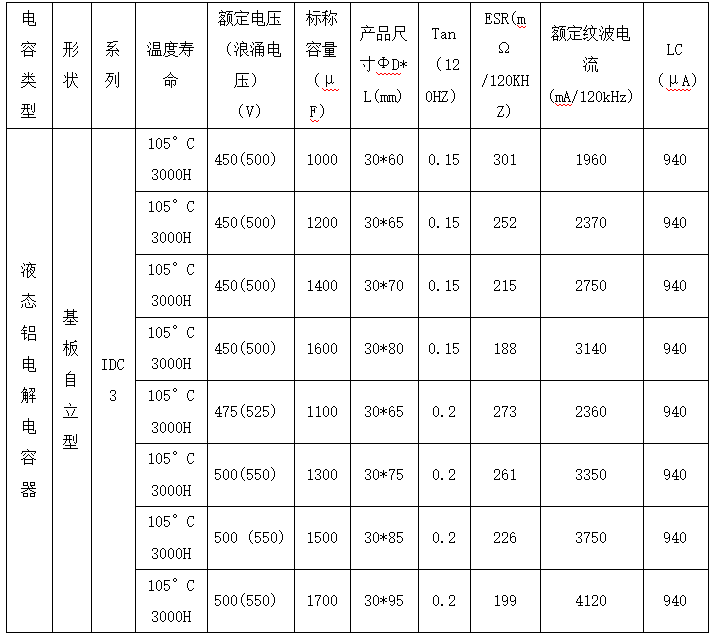

主供電源·突破密度極限:永銘的液態高壓牛角電容與固液混合電容,通過材料與結構創新,實現了單位體積容值的顯著提升,以更小體積提供更高儲能與更強紋波電流耐受能力,完美應對AI服務器電源高功率密度化的嚴苛挑戰。

BBU備用電源·瞬間的力量:永銘鋰離子超級電容方案,以其超低內阻(<1mΩ) 和超高倍率充放電性能,實現了對GPU負載微秒級/毫秒級劇烈波動的“瞬間”補償,將備用電源的響應與調節能力提升至全新高度,保障AI服務器運行永不中斷。

SSD斷電保護·守護數據基石:面對PCIe 5.0/6.0 SSD萬兆級讀寫速度下的數據安全危機,永銘斷電保護電容憑借超低ESR特性,確保在斷電瞬間能以毫秒級速度釋放能量,完成數據保全,為企業級存儲的可靠性構筑起堅不可摧的防線。

主板供電·決勝毫厘之間:永銘超低ESR疊層/聚鉭電容,緊貼CPU/GPU布局,以其極低的能量損耗和優異的高頻特性,為核心處理器提供精準、純凈、不間斷的能量供給,是保障AI算力在“毫厘之間”穩定輸出的關鍵。

AI服務器芯片廠商

現場,從納微聚焦的《AI服務器電源——一站式解決方案》,到鋁電解技術專家解析的《鋁電解電容可靠性要求》,覆蓋從尖端電源架構到核心元器件可靠性,完整展現了雙方從技術前沿到質量根基的協同布局。

圓 桌 會

在最后的圓桌討論環節,永銘技術人員與多為AI服務器技術專家,就《AI服務器電源800VHVDC直流配電系統--面臨的機遇與挑戰》展開了深度對話。討論聚焦于高電壓平臺對電容等核心器件提出的新要求、技術瓶頸與未來趨勢,現場思想碰撞,共識凝聚。

END

算力時代依然覺醒,AI共生成為未來主題。上海永銘電子以“國產高端電容優秀供應商”為定位,以其不斷迭代升級的自動化、數字化、智能化制程與卓越的品質保證能力,矢志為全球AI服務器的蓬勃發展保駕護航。

我們誠邀各位業界伙伴,與永銘攜手,共同開拓屬于智能時代的無限可能。

-

電容

+關注

關注

100文章

6496瀏覽量

159748 -

人工智能

+關注

關注

1819文章

50177瀏覽量

266164 -

AI服務器

+關注

關注

3文章

184瀏覽量

5559

發布評論請先 登錄

電氣水熱 智聯萬物 | 上海永銘電子誠邀您蒞臨電力電子專題會議

邊緣AI算力臨界點:深度解析176TOPS香橙派AI Station的產業價值

2026年上海永銘電子代理商會議圓滿落幕:確定的方向,有限的窗口,攜手搶占未來賽道

AI算力背后的隱形英雄:Φ30×70mm 450V/1400μF、105℃/3000H的國產高壓電容如何破解服務器電源三大難題

AI算力背后的隱形英雄:Φ30×70mm 450V/1400μF、105℃/3000h的國產高壓電容如何破解服務器電源三大難題

算力覺醒 · AI共生——上海永銘電子2025AI服務器電容應用專題會議圓滿落幕

算力覺醒 · AI共生——上海永銘電子2025AI服務器電容應用專題會議圓滿落幕

評論