1、軟件版本vivado202001。

2、其中程序的源文件都是拷貝過(guò)來(lái)的只是稍作修改,對(duì)其中的操作步驟做細(xì)化分析,參考文檔UG585

https://blog.csdn.net/weixin_41922484/article/details/104037513

3、串口打印FSBL中啟動(dòng)信息。

只需要在以下位置的的fsbl_debug.h中,添加一個(gè)宏定義即可。

#define FSBL_DEBUG_INFO

4、新建兩個(gè)app

hello_test1.c

#include

#include "platform.h"

#include "xil_printf.h"

#include "xil_io.h"

#include "sleep.h"

#define PSS_RST_CTRL_REG 0xF8000200 //PSS_RST_CTRL寄存器,絕對(duì)地址,

#define SLCR_UNLOCK_ADDR 0xF8000008 //SLCR_UNLOCK寄存器,絕對(duì)地址,

#define UNLOCK_KEY 0xDF0D //使能碼

#define PSS_RST_MASK 0x01 //復(fù)位碼

void PsSoftwareReset(void)

{

Xil_Out32(SLCR_UNLOCK_ADDR, UNLOCK_KEY); //寫使能

Xil_Out32(PSS_RST_CTRL_REG, PSS_RST_MASK); //復(fù)位

}

#define XDCFG_MULTIBOOT_ADDR_OFFSET_REG 0xF800702C //MULTIBOOT寄存器,絕對(duì)地址,

#define XDCFG_UNLOCK_OFFSET_ADDR 0xF8007034 //XDCFG_UNLOCK_寄存器,絕對(duì)地址,

#define UNLOCK_XDCFG_KEY 0x757BDF0D //使能碼

#define APP1_LOCATION 0

#define APP2_LOCATION 128

void ModifyMultiBoot(void)

{

Xil_Out32(XDCFG_UNLOCK_OFFSET_ADDR , UNLOCK_XDCFG_KEY ); //寫使能

Xil_Out32(XDCFG_MULTIBOOT_ADDR_OFFSET_REG , APP2_LOCATION ); //更改MULTIBOOT

}

int main()

{

init_platform();

print("111111111111111111111111111111111111111\r\n");

sleep(5);

ModifyMultiBoot();

PsSoftwareReset();

cleanup_platform();

return 0;

}

hello_test2.c

#include

#include "platform.h"

#include "xil_printf.h"

#include "xil_io.h"

#include "sleep.h"

#define PSS_RST_CTRL_REG 0xF8000200 //PSS_RST_CTRL寄存器,絕對(duì)地址,

#define SLCR_UNLOCK_ADDR 0xF8000008 //SLCR_UNLOCK寄存器,絕對(duì)地址,

#define UNLOCK_KEY 0xDF0D //使能碼

#define PSS_RST_MASK 0x01 //復(fù)位碼

void PsSoftwareReset(void)

{

Xil_Out32(SLCR_UNLOCK_ADDR, UNLOCK_KEY); //寫使能

Xil_Out32(PSS_RST_CTRL_REG, PSS_RST_MASK); //復(fù)位

}

#define XDCFG_MULTIBOOT_ADDR_OFFSET_REG 0xF800702C //MULTIBOOT寄存器,絕對(duì)地址,

#define XDCFG_UNLOCK_OFFSET_ADDR 0xF8007034 //XDCFG_UNLOCK_寄存器,絕對(duì)地址,

#define UNLOCK_XDCFG_KEY 0x757BDF0D //使能碼

#define APP1_LOCATION 0

#define APP2_LOCATION 128

void ModifyMultiBoot(void)

{

Xil_Out32(XDCFG_UNLOCK_OFFSET_ADDR , UNLOCK_XDCFG_KEY ); //寫使能

Xil_Out32(XDCFG_MULTIBOOT_ADDR_OFFSET_REG , APP2_LOCATION ); //更改MULTIBOOT

}

int main()

{

init_platform();

print("222222222222222222222222222222222\r\n");

sleep(5);

ModifyMultiBoot();

PsSoftwareReset();

cleanup_platform();

return 0;

}

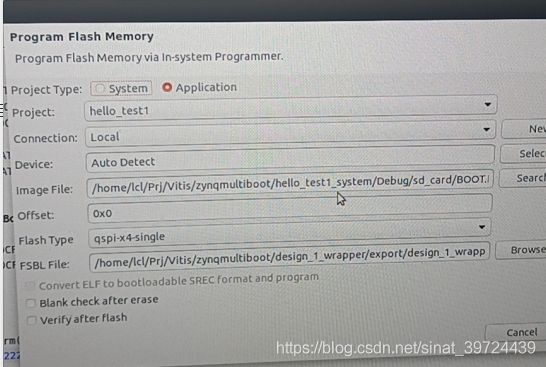

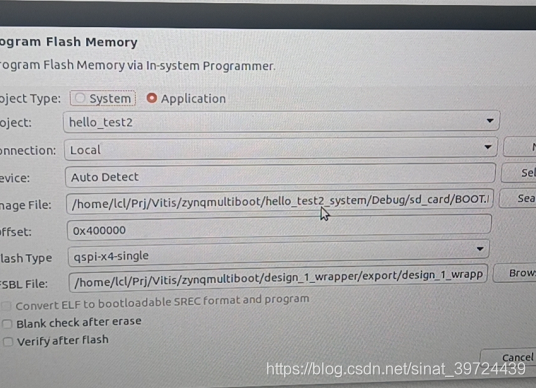

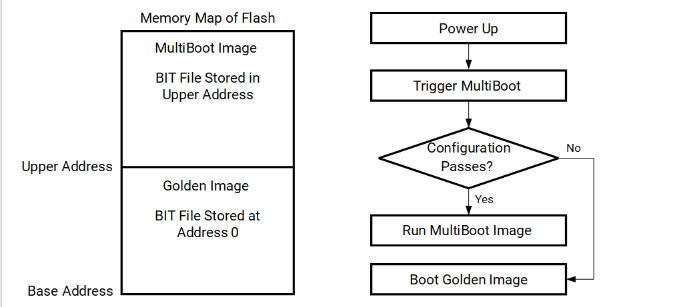

5、分別生成bin文件,且需要注意生成的bin文件大小,因?yàn)槭欠侄螣龑慺lash,第一個(gè)bin與第二個(gè)bin的間隔要比第一個(gè)bin的文件要大,且間隔為32KB的整數(shù)倍,此次實(shí)驗(yàn)中,生成的bin都是2.2MB,所以把第二個(gè)的bin起始地址設(shè)置為128*32KB。

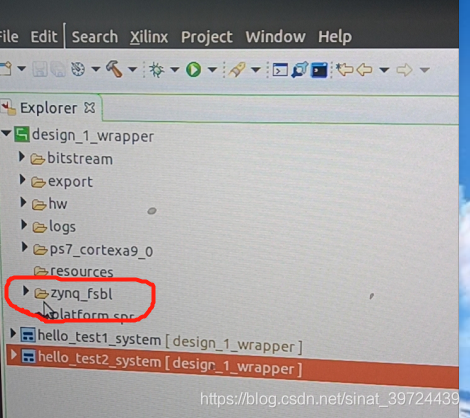

6、在JTAG模式下燒寫FLASH

7、在QSPI模式下啟動(dòng)

串口打印輸出

[15:07:38.243]收←◆

Xilinx First Stage Boot Loader

Release 2020.1 Mar 24 2021-03:07:57

Devcfg driver initialized

Silicon Version 3.1

Boot mode is QSPI

Single Flash Information

FlashID=0xEF 0x40 0x19

WINBOND 256M Bits

QSPI is in single flash connection

QSPI is in 4-bit mode

QSPI Init Done

Flash Base Address: 0xFC000000

Reboot status register: 0x60480000

Multiboot Register: 0x0000C000

Image Start Address: 0x00000000

Partition Header Offset:0x00000C80

Partition Count: 3

Partition Number: 1

Header Dump

Image Word Len: 0x0007F2E8

Data Word Len: 0x0007F2E8

Partition Word Len:0x0007F2E8

Load Addr: 0x00000000

Exec Addr: 0x00000000

Partition Start: 0x000065D0

Partition Attr: 0x00000020

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFFE7BF06

Bitstream

In FsblHookBeforeBitstreamDload function

[15:07:38.610]收←◆P

[15:07:38.640]收←◆CAP:StatusReg = 0x40000A30

PCAP:device ready

PCAP:Clear done

Level Shifter Value = 0xA

Devcfg Status register = 0x40000A30

PCAP:Fabric is Initialized done

PCAP register dump:

PCAP CTRL 0xF8007000: 0x4C00E07F

PCAP LOCK 0xF8007004: 0x0000001A

PCAP CONFIG 0xF8007008: 0x00000508

PCAP ISR 0xF800700C: 0x0802000B

PCAP IMR 0xF8007010: 0xFFFFFFFF

PCAP STATUS 0xF8007014: 0x50000F30

PCAP DMA SRC ADDR 0xF8007018: 0x00100001

PCAP DMA DEST ADDR 0xF800701C: 0xFFFFFFFF

PCAP DMA SRC LEN 0xF8007020: 0x0007F2E8

PCAP DMA DEST LEN 0xF8007024: 0x0007F2E8

PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF

PCAP MBOOT 0xF800702C: 0x0000C000

PCAP SW ID 0xF8007030: 0x00000000

PCAP U

[15:07:38.694]收←◆NLOCK 0xF8007034: 0x757BDF0D

PCAP MCTRL 0xF8007080: 0x30800100

DMA Done !

FPGA Done !

In FsblHookAfterBitstreamDload function

Partition Number: 2

Header Dump

Image Word Len: 0x00002002

Data Word Len: 0x00002002

Partition Word Len:0x00002002

Load Addr: 0x00100000

Exec Addr: 0x00100000

Partition Start: 0x000858C0

Partition Attr: 0x00000010

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFFD744C8

Application

Handoff Address: 0x00100000

In FsblHookBeforeHandoff function

SUCCESSFUL_HANDOFF

FSBL Status = 0x1

11111111111111111111111111111111111111111

[15:07:43.911]收←◆

Xilinx First Stage Boot Loader

Release 2020.1 Mar 24 2021-03:07:57

Devcfg driver initialized

Silicon Version 3.1

Boot mode is QSPI

Single Flash Information

FlashID=0xEF 0x40 0x19

WINBOND 256M Bits

QSPI is in single flash connection

QSPI is in 4-bit mode

QSPI Init Done

Flash Base Address: 0xFC000000

Reboot status register: 0x60480000

Multiboot Register: 0x0000C080

Image Start Address: 0x00400000

Partition Header Offset:0x00400C80

Partition Count: 3

Partition Number: 1

Header Dump

Image Word Len: 0x0007F2E8

Data Word Len: 0x0007F2E8

Partition Word Len:0x0007F2E8

Load Addr: 0x00000000

Exec Addr: 0x00000000

Partition Start: 0x000065D0

Partition Attr: 0x00000020

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFFE7BF06

Bitstream

In FsblHookBeforeBitstreamDload function

[15:07:44.276]收←◆PCAP:StatusReg = 0x40000A30

PCAP:device ready

PCAP:Clear done

Level Shifter Value = 0xA

Devcfg Status register = 0x40000A30

PCAP:Fabric is Initialized done

PCAP register dump:

PCAP CTRL 0xF8007000: 0x4C00E07F

PCAP LOCK 0xF8007004: 0x0000001A

PCAP CONFIG 0xF8007008: 0x00000508

PCAP ISR 0xF800700C: 0x0802000B

PCAP IMR 0xF8007010: 0xFFFFFFFF

PCAP STATUS 0xF8007014: 0x50000F30

PCAP DMA SRC ADDR 0xF8007018: 0x00100001

PCAP DMA DEST ADDR 0xF800701C: 0xFFFFFFFF

PCAP DMA SRC LEN 0xF8007020: 0x0007F2E8

PCAP DMA DEST LEN 0xF8007024: 0x0007F2E8

PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF

PCAP MBOOT 0xF800702C: 0x0000C080

PCAP SW ID 0xF8007030: 0x00000000

PCAP UNLOCK 0xF8007034: 0x757BDF0D

PCAP MCTRL 0xF8007080: 0x30800100

DMA Done !

FPGA Done !

In FsblHookAfterBitstreamDload function

Partition Number: 2

Header Dump

Image Word Len: 0x00002002

Data Word Len: 0x00002002

Partition Word Len:0x00002002

Load Addr: 0x00100000

Exec Addr: 0x00100000

Partition Start: 0x000858C0

Partition Attr: 0x00000010

Partition Checksum Offset: 0x00000000

Section Count: 0x00000001

Checksum: 0xFFD744C8

Application

Handoff Address: 0x00100000

In FsblHookBeforeHandoff function

SUCCESSFUL_HANDOFF

FSBL Status = 0x1

22222222222222222222222222222222222222222

測(cè)試成功。

審核編輯:符乾江

-

測(cè)試

+關(guān)注

關(guān)注

9文章

6203瀏覽量

131352 -

Zynq

+關(guān)注

關(guān)注

10文章

630瀏覽量

49448

發(fā)布評(píng)論請(qǐng)先 登錄

如何在Zynq UltraScale+ MPSoC平臺(tái)上通過(guò)JTAG啟動(dòng)嵌入式Linux鏡像

電源模塊紋波測(cè)試方法解析說(shuō)明(手動(dòng)測(cè)試+自動(dòng)測(cè)試)

【ALINX 教程】FPGA Multiboot 功能實(shí)現(xiàn)——基于 ALINX Artix US+ AXAU25 開發(fā)板

如何在ZYNQ本地部署DeepSeek模型

基于AXI DMA IP核的DDR數(shù)據(jù)存儲(chǔ)與PS端讀取

ZYNQ PS與PL數(shù)據(jù)交互方式

Zynq7100 BSP移植,MSH終端不能正確顯示是為什么?

ZYNQ UltraScalePlus RFSOC QSPI Flash固化常見問題說(shuō)明

CH367連接zynq問題

ZYNQ FPGA的PS端IIC設(shè)備接口使用

詳解Zynq中的SPI控制器

Zynq7000處理器的配置詳解

基于ZYNQ的multiBoot測(cè)試說(shuō)明

基于ZYNQ的multiBoot測(cè)試說(shuō)明

評(píng)論