在搭建完Block Design以及硬件代碼后,生成bit;

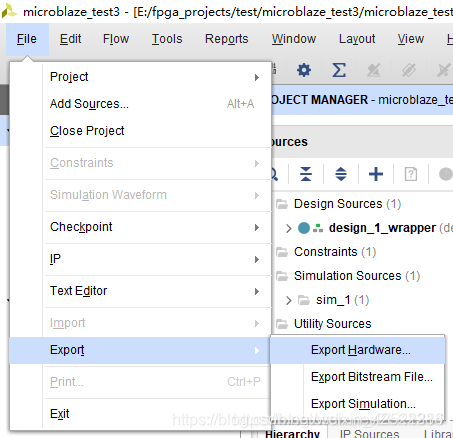

bit文件生成成功后,點擊Export Hardware,導出xsa文件:(xsa做連接使用)

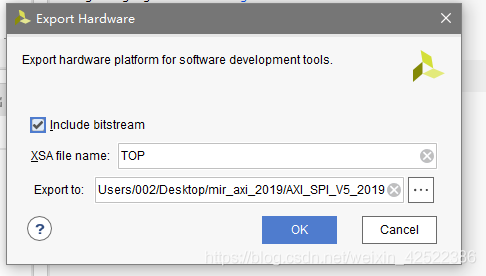

勾選 include bitstream

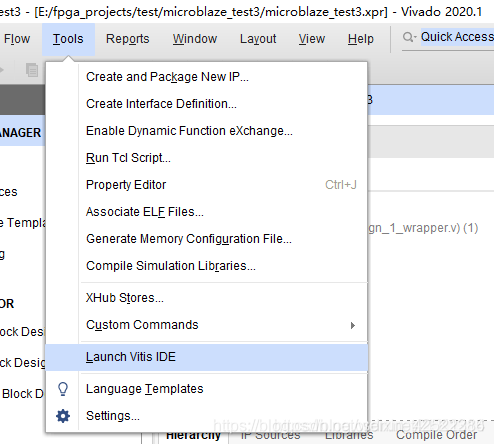

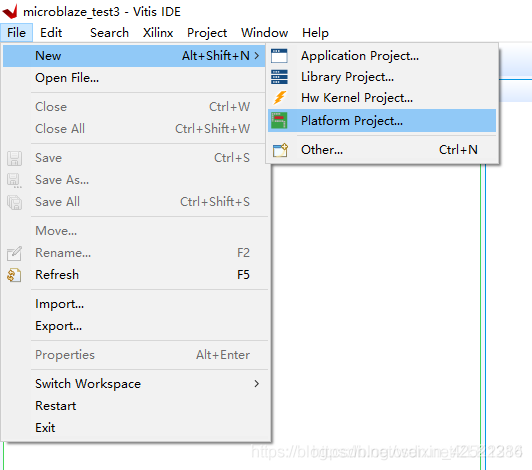

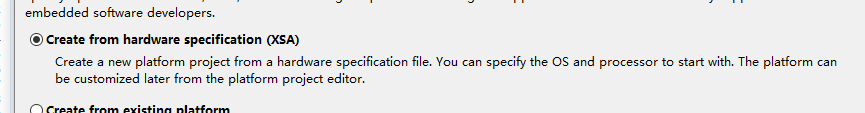

有了xsa文件,就可以啟動Vitis 了。

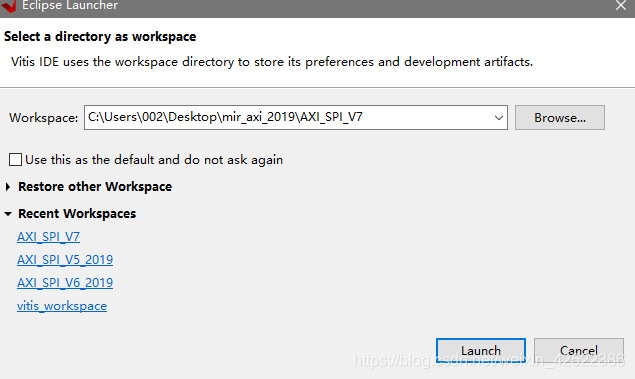

選擇工作目錄

選擇使用xsa后,選擇XSA路徑即可。完成后bulid project!!!

再建立一個APP project工程,用于代碼書寫。寫完后bulid project!!!

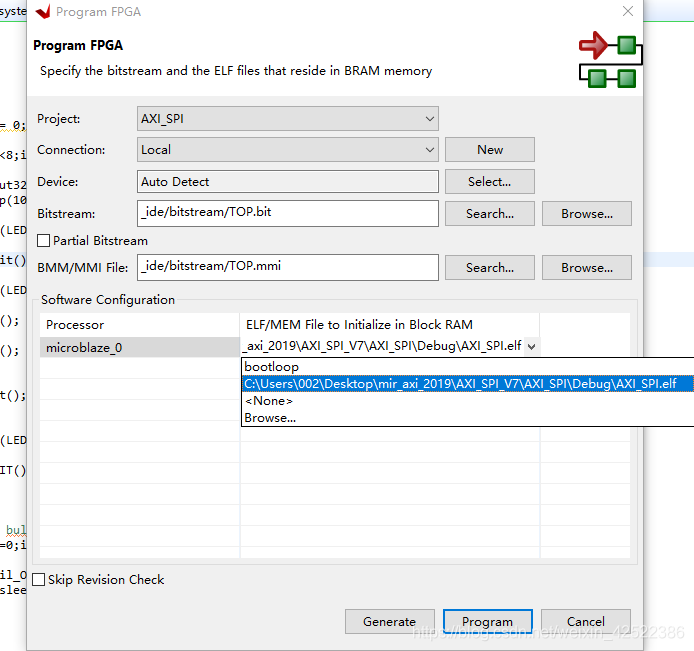

開始固化

固化需要兩步。

第一步是在Program FPGA對話框里面,將bit文件和Vitis工程elf文件合并成一個download.bit文件:

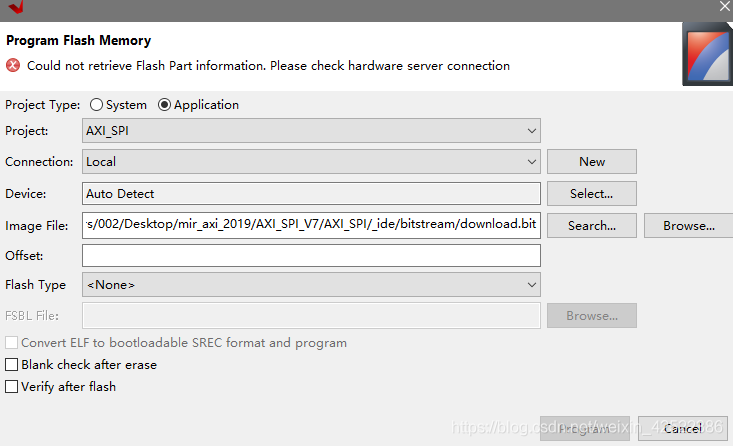

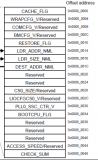

第二步就是在Program Flash對話框中,把合并后的download.bit文件燒寫到SPI Flash里面:

選擇對應型號flash即可。

若更改vivado代碼更改了,新生成了bit文件,然后,整個Vitis工程都必須刪了重建!!!!!!

重新建立Platform工程,Build一下,再重新建立Application工程,再Build一下

點Program FPGA生成download.bit,再點Program Flash把download.bit固化到flash

審核編輯:符乾江

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

代碼

+關注

關注

30文章

4968瀏覽量

74010 -

Vitis

+關注

關注

0文章

157瀏覽量

8359

發布評論請先 登錄

相關推薦

熱點推薦

3562 單板機 Linux 系統固化完全指南:從 SD 卡啟動到 eMMC 永久部署

本文為創龍科技 3562 單板機系統固化操作指南,核心涵蓋 SD 啟動卡、升級卡制作,以及 eMMC 芯片系統固化與啟動驗證。文檔詳細說明專用工具使用、鏡像燒錄參數配置、多方式啟動測試流程

Vivado+Vitis將程序固化的Flash的操作流程

ZYNQ 的程序固化是指將程序代碼永久存儲到非易失性存儲器中,使系統上電后能自動加載運行的過程。主要固化方式:QSPI Flash固化:常用方式,容量小,如啟動

基于Vitis Model Composer完成全流程AI Engine開發

基于Vitis Model Composer進行AI Engine(AIE)開發,核心優勢體現在AIE專屬優化、開發流程簡化、靈活的適配性、高效驗證及量產適配等方面。

如何在AMD Vitis Unified IDE中使用系統設備樹

您將在這篇博客中了解系統設備樹 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 維護來自 XSA 的硬件元數據。本文還講述了如何對 SDT 進行操作,以便在 Vitis Unified IDE 中實現更靈活的使用場景。

AMD Vitis AI 5.1測試版發布

AMD Vitis AI 5.1全新發布——新增了對 AMD Versal AI Edge 系列神經網絡處理單元 (NPU) 的支持。Vitis AI 包含優化的 NPU IP、模型編譯工具和部署 API,可在嵌入式平臺上實現可擴展的高性能推理。

E203軟核提高CPU時鐘頻率方法

本文將分享我們團隊提高E203軟核主頻的辦法。

查閱芯來科技官方出版的《手把手教你設計CPU——RISC-V處理器篇》教材,我們發現,原本設計的E203主時鐘域應該是100MHZ

發表于 10-29 06:19

芯來e203移植開發分享(二)——仿真文件簡述與itcm固化程序

根據上次的分享,已經把e203成到verdi與vcs仿真環境下。這次簡單介紹一下e203的仿真文件與itcm固化程序的仿真。

仿真文件

簡單分析一下e203的自帶的仿真文件,跟著上次的分享,我們

發表于 10-27 06:04

ZYNQ UltraScalePlus RFSOC QSPI Flash固化常見問題說明

璞致 ZYNQ UltraScalePlus RFSOC QSPI Flash 固化常見問題說明

發表于 08-08 15:49

?0次下載

如何在Unified IDE中創建視覺庫HLS組件

最近我們分享了開發者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統 IDE)和開發者分享|AMD Vitis HLS 系列 2:AM

使用AMD Vitis Unified IDE創建HLS組件

這篇文章在開發者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統 IDE) 的基礎上撰寫,但使用的是 AMD Vitis Unifie

如何使用AMD Vitis HLS創建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創建一個 HLS IP,通過 AXI4 接口從存儲器讀取數據、執行簡單的數學運算,然后將數據寫回存儲器。接著會在 AMD Vivado Design Suite 設計中使用此 HLS IP,并使用嵌入式 Vitis 應

中軟國際亮相中國核建2025數字生態大會

此前,5月13日至14日,中國核建2025數字生態大會在雄安會展中心隆重召開。大會以“數智賦能新生態,轉型共贏創未來”為主題,由中國核學會指導、中國核建成員單位中核華輝承辦。中

RZT2H CR52雙核BOOT流程和例程代碼分析

RZT2H是多核處理器,啟動時,需要一個“主核”先啟動,然后主核根據規則,加載和啟動其他內核。本文以T2H內部的CR52雙核為例,說明T2H多核啟動

Vitis軟核固化代碼流程說明

Vitis軟核固化代碼流程說明

評論