1、對(duì)于AXI4-FULL總線時(shí),握手信號(hào)共有5路,包括寫(xiě)地址,寫(xiě)數(shù)據(jù),寫(xiě)應(yīng)答,讀地址,讀數(shù)據(jù)。

2、當(dāng)主機(jī)burst寫(xiě)時(shí),每發(fā)起一次猝發(fā)交易,需要有一筆應(yīng)答對(duì)應(yīng)。

3、當(dāng)主機(jī)進(jìn)行讀數(shù)據(jù)時(shí),接受數(shù)據(jù)即可。

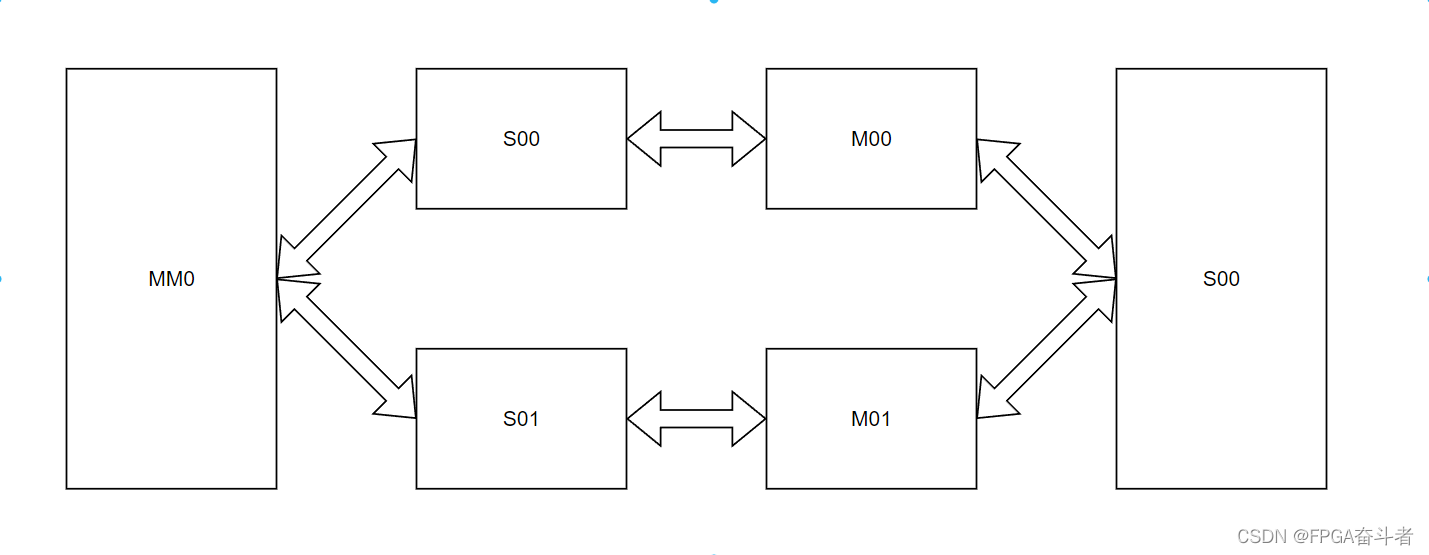

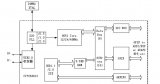

4、具體如圖所示

5、共5路信號(hào),每路信號(hào)都包括握手信號(hào),ready和valid,當(dāng)ready和valid都有效時(shí),此時(shí)數(shù)據(jù)才有效,且信號(hào)不存在相互等待關(guān)系,以免發(fā)生死鎖現(xiàn)象。

6、包括aw,w,b,ar,r,每路信號(hào)都應(yīng)用FIFO做緩存,使數(shù)據(jù)對(duì)齊。

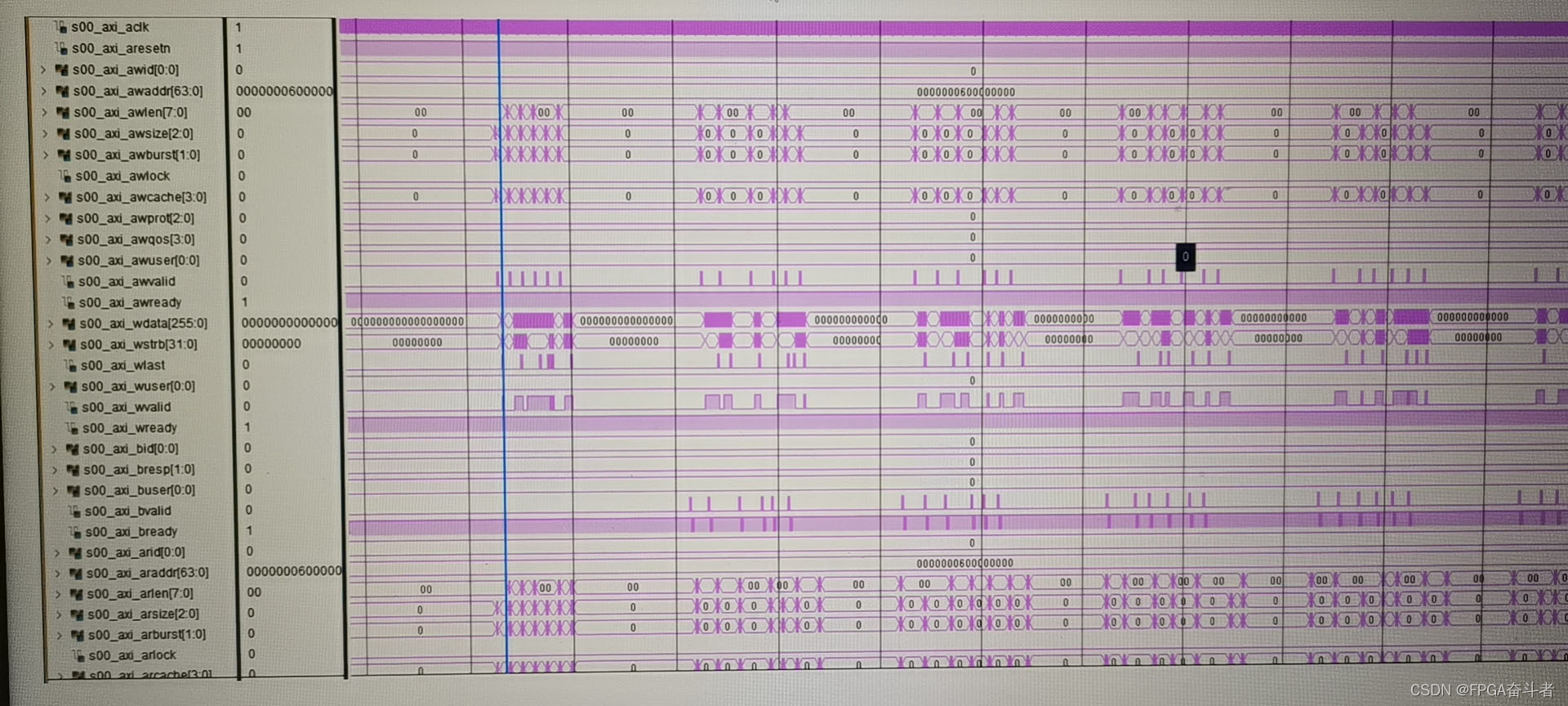

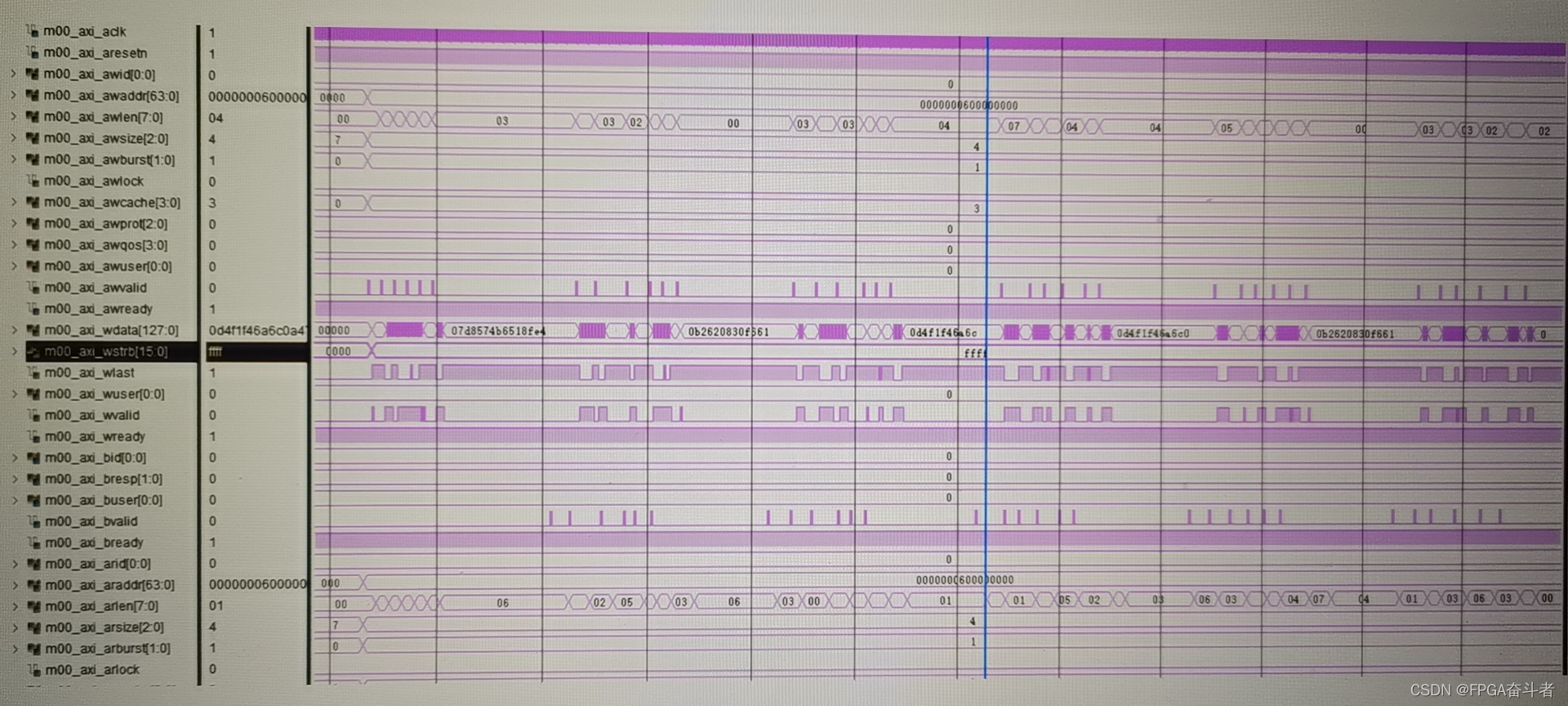

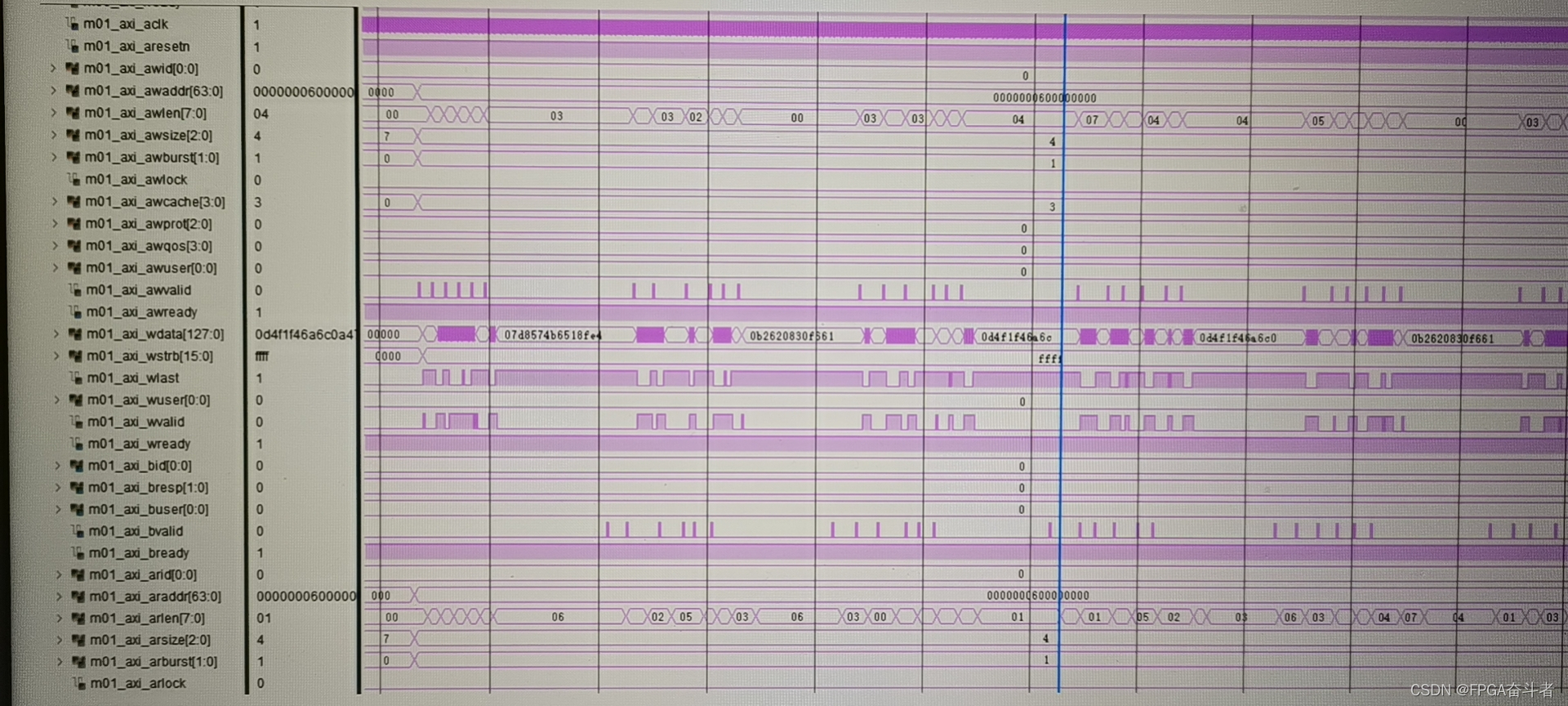

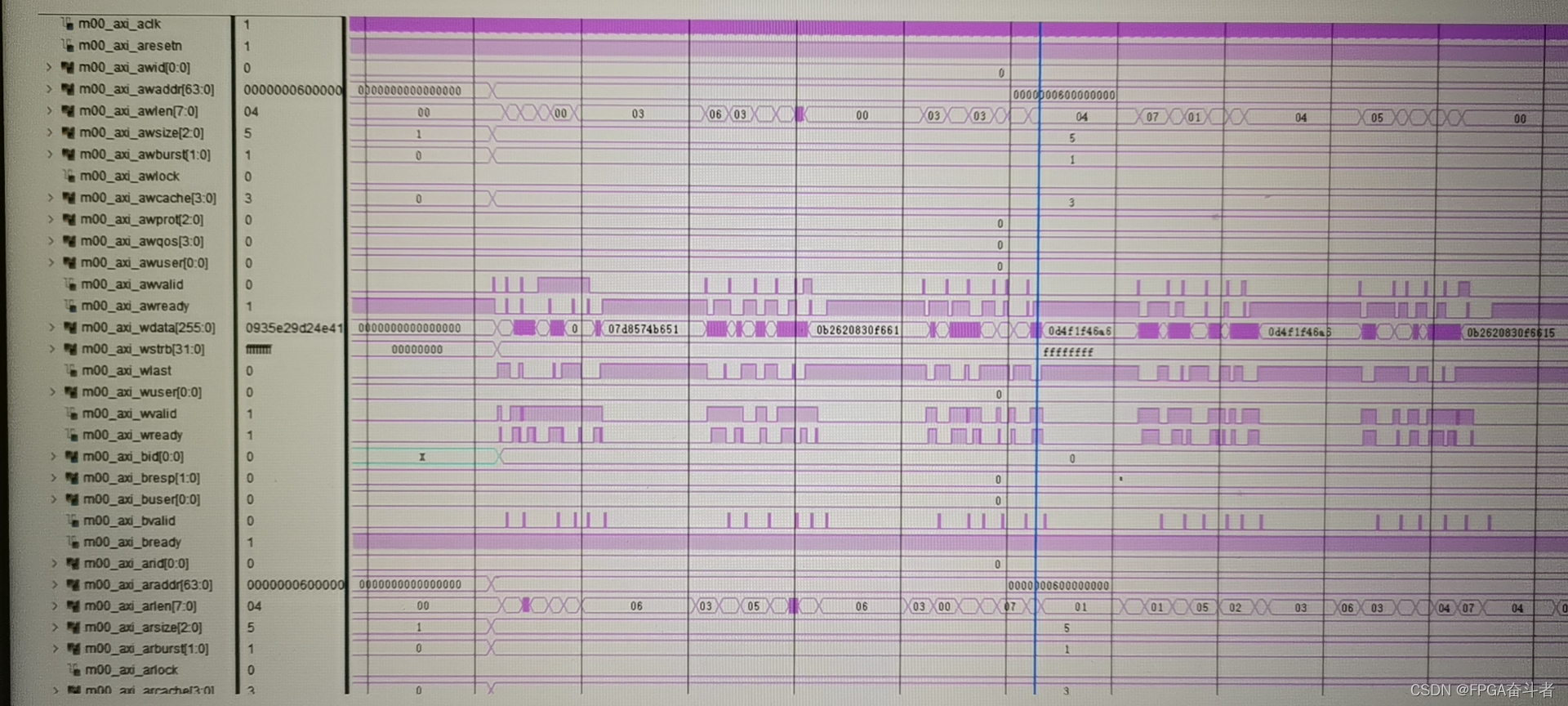

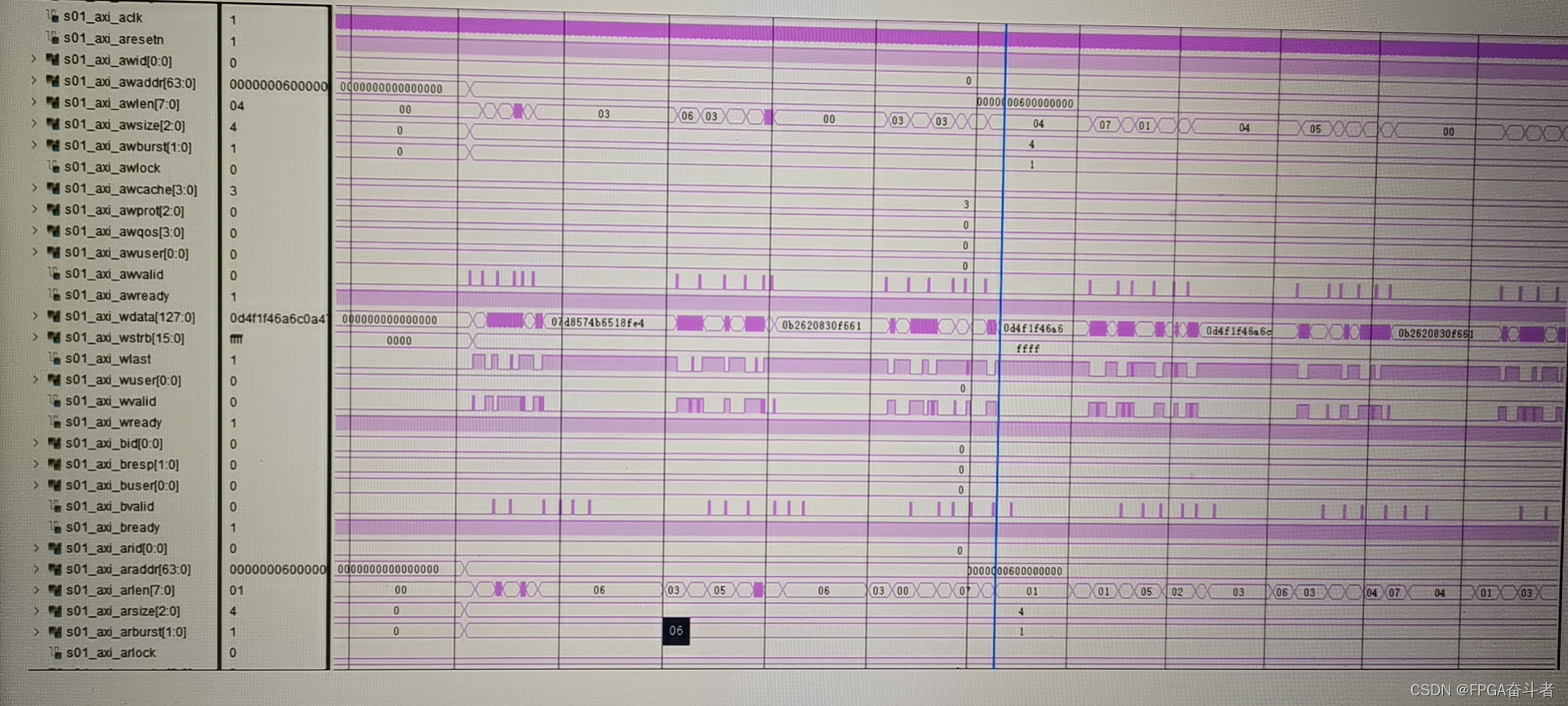

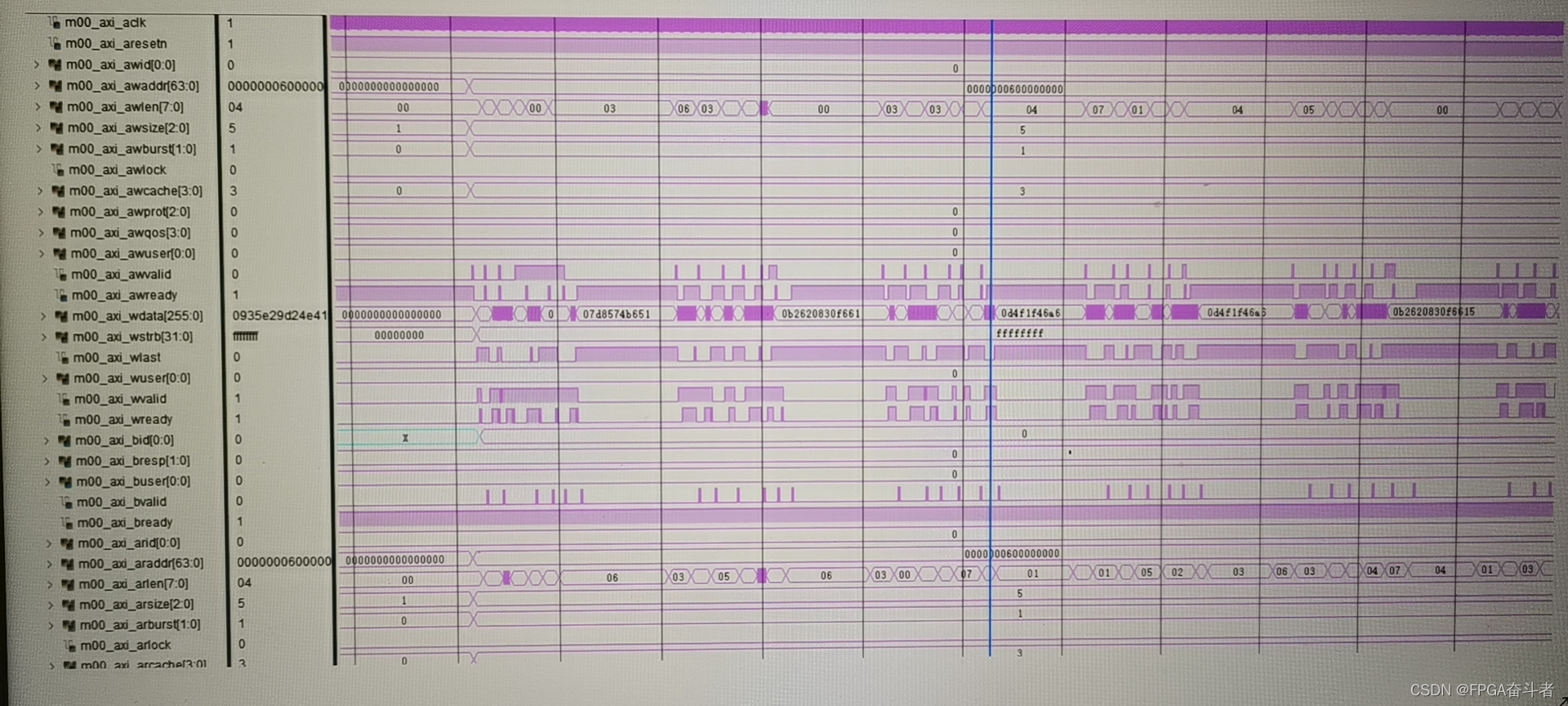

7、代碼仿真如下

(1)

(2)

(3)

(4)

(5)

(6)

8、對(duì)其中的一組數(shù)據(jù)加延時(shí),同樣也可以使數(shù)據(jù)對(duì)齊,容忍度為FIFO的大小。

審核編輯:符乾江

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7335瀏覽量

94755 -

總線

+關(guān)注

關(guān)注

10文章

3040瀏覽量

91658 -

AXI4

+關(guān)注

關(guān)注

0文章

21瀏覽量

9183

發(fā)布評(píng)論請(qǐng)先 登錄

探索DS92LX1621/DS92LX1622:高速數(shù)據(jù)傳輸的理想選擇

探索DS92LV0411/DS92LV0412:高速數(shù)據(jù)傳輸的理想選擇

探索DS100KR401:高速數(shù)據(jù)傳輸的理想中繼器

RDMA設(shè)計(jì)4:技術(shù)需求分析2

基于FPGA的USB數(shù)據(jù)傳輸

RDMA簡(jiǎn)介9之AXI 總線協(xié)議分析2

RDMA簡(jiǎn)介8之AXI 總線協(xié)議分析1

NVMe IP之AXI4總線分析

NVMe協(xié)議簡(jiǎn)介之AXI總線

SPI數(shù)據(jù)傳輸緩慢問(wèn)題求解

捷多邦的IoT PCB:數(shù)據(jù)傳輸的未來(lái)

AXI4-FULL總線多通道數(shù)據(jù)傳輸,合并生成一組數(shù)據(jù)的討論

AXI4-FULL總線多通道數(shù)據(jù)傳輸,合并生成一組數(shù)據(jù)的討論

評(píng)論