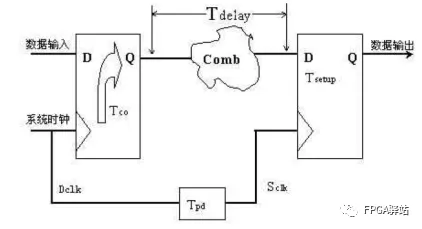

面積通常指一個設計消耗FPGA/CPLD的邏輯資源的數量,通常用可消耗的FF(觸發器)和LUT(查找表)來衡量。速度指設計在芯片上穩定運行所能達到的最高頻率,這個頻率由設計的時序狀況來決定,以及設計滿足的時鐘要求:PAD to PAD time 、Clock Setup Time、Clock Hold Time、Clock-to-Output Delay等眾多時序特征量密切相關,具體示意圖如下圖所示:

要求同時具備設計面積最小、運行頻率最高是不現實的。更科學的設計目標應該是在滿足設計時序要求(包括對設計頻率要求)的前提下,占用最小的芯片面積。或者在所規定的面積下,使設計的時序余量更大、頻率跑得更高。這兩種目標充分體現了面積和速度的平衡思想。

作為矛盾的兩個組成部分,面積和速度的地位是不一樣的。相比之下,滿足時序、工作頻率的要求更重要一些,當兩者沖突時,采用速度優先的準則。

02. 硬件和系統原則

硬件原則主要針對HDL代碼編寫而言:Verilog是采用了C語言形式的硬件的抽象,它的本質作用在于描述硬件;它的最終實現結果是芯片內部的實際電路。所以評判一段HDL代碼優劣的最終標準是:其描述并實現的硬件電路性能,包括面積和速度兩個方面。

評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件向HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在更大程度上取決于設計工程師所構想的硬件實現方案的效率以及合理性。(HDL代碼僅僅是硬件設計的表達形式之一)。

初學者片面追求代碼的整潔、簡短是錯誤的,是與HDL的標準背道而馳的。正確的編碼方法首先要做到對所需實現的硬件電路胸有成竹,對該部分的硬件的結構和連接十分清晰,然后再用適當的HDL語句表達出來即可。

系統原則包含兩個層次的含義:更高層面上看,是一個硬件系統,一塊單板如何進行模塊劃分和任務分配、什么樣的算法和功能適合放在FPGA里面實現、什么樣的算法和功能適合放在DSP/CPU里面實現、以及FPGA的規模估算數據接口設計等。具體到FPGA設計就要對設計的全局有個宏觀上的合理安排,比如時鐘域、模塊復用、約束、面積、速度等問題,在系統上模塊的優化最為重要。

一般來說實時性要求高,頻率快的功能模塊適合FPGA實現。而FPGA和CPLD相比,更適合實現規模較大、頻率較高、寄存器較多的設計。使用FPGA/CPLD設計時,應該對芯片內部的各種底層硬件資源和可用的設計資源有一個較深刻的認識。

03. 同步設計原則

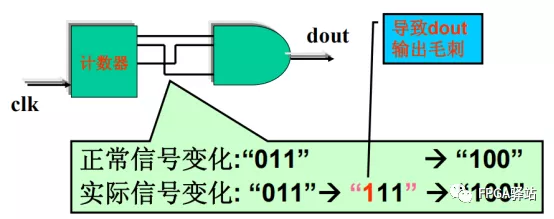

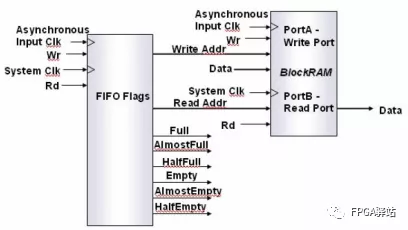

異步電路的邏輯核心是用組合邏輯電路實現,比如異步的FIFO/RAM讀寫信號,地址譯碼等電路。電路的主要信號、輸出信號等并不依賴于任何一個時鐘性信號,不是由時鐘信號驅動FF產生的。異步時序電路的最大缺點是容易產生毛刺,毛刺產生的機理主要有爭和冒險導致毛刺、組合延時和布線延時不平衡導致譯碼輸出毛刺以及線間的信號耦合導致毛刺。具體如下圖所示:

同步時序電路的核心邏輯是用各種各樣的觸發器實現,電路的主要信號、輸出信號都是由某個時鐘沿驅動觸發器產生出來的。同步時序電路可以很好的避免毛刺。

同步時序電路的延時一般是通過時序控制完成的,換句話說,同步時序電路的延時被當做一個電路邏輯來設計。對于比較大的和特殊定時要求的延時,一般用高速時鐘產生一個計數器,通過計數器的計數控制延遲;對于比較小的延時,可以用D觸發器打一下,這種做法不僅僅使信號延時了一個時鐘周期,而且完成了信號與時鐘的初次同步,在輸入信號采樣和增加時序約束余量中使用。

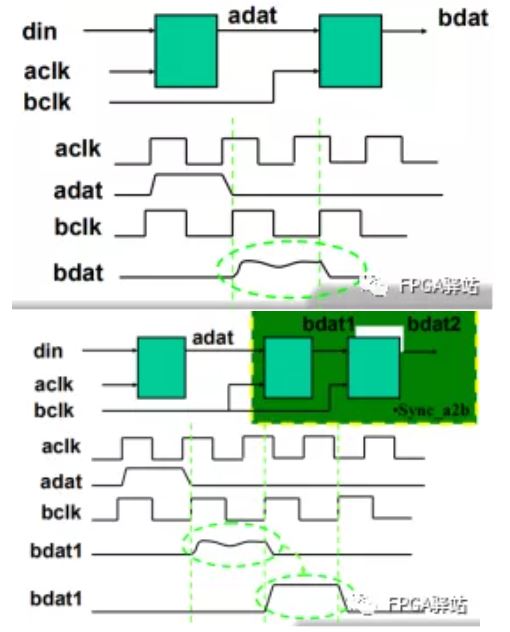

同步時序電路的時鐘如何產生?時鐘的質量和穩定性直接決定著同步時序電路的性能。輸入信號的同步時序電路要求對輸入信號進行同步化,如果輸入數據的節拍和本級芯片的處理時鐘同頻,并且建立保持時間匹配,可以直接用本級芯片的主時鐘對輸入數據寄存器采樣,完成輸入數據的同步化。如果輸入數據和本級芯片的處理時鐘是異步的,特別是頻率不匹配的時候,則要用處理時鐘對輸入數據做兩次寄存器采樣,才能完成輸入數據的同步化。

是不是定義為Reg型,就一定綜合成寄存器,并且是同步時序電路呢?答案是否定的。Verilog中最常用的兩種數據類型Wire和Reg,一般來說,Wire型指定輸數據和網線通過組合邏輯實現,而reg型指定的數據不一定就是用寄存器實現。

04. 乒乓操作及串并轉換設計

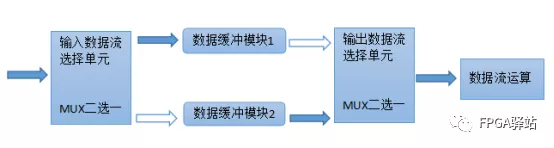

“ 乒乓操作 ”是一個常常應用于數據流控制的處理技巧。乒乓操作的處理流程為:輸入數據流通過“ 輸入數據選擇單元 ”將數據流等時分配到兩個數據緩沖區,數據緩沖模塊可以為任何存儲模塊,比較常用的存儲單元為雙口 RAM(DPRAM) 、單口 RAM(SPRAM) 、 FIFO 等。

在第一個緩沖周期,將輸入的數據流緩存到“ 數據緩沖模塊 1”;在第 2 個緩沖周期,通過“ 輸入數據選擇單元 ”的切換,將輸入的數據流緩存到“ 數據緩沖模塊 2”,同時將“ 數據緩沖模塊 1”緩存的第 1 個周期數據通過“ 輸入數據選擇單元 ”的選擇,送到“ 數據流運算處理模塊 ”進行運算處理;在第 3 個緩沖周期通過“ 輸入數據選擇單元 ”的再次切換,將輸入的數據流緩存到“ 數據緩沖模塊 1”,同時將“ 數據緩沖模塊 2”緩存的第 2 個周期的數據通過“ 輸入數據選擇單元 ”切換,送到“ 數據流運算處理模塊 ”進行運算處理。如此循環。

典型的乒乓操作方法

乒乓操作的最大特點是,通過輸入數據選擇單元和輸出數據選擇單元進行運算和處理。把乒乓操作模塊當成一個整體,站在兩端看數據,輸入數據和輸出數據流都是連續不斷的,沒有任何停頓,因此非常適合對數據流進行流水線式處理。所以乒乓操作常常應用于流水線式算法,完成數據的無縫緩沖和處理。另外,巧妙運用乒乓操作還可以達到用低速模塊處理高速數據流的效果。如下圖所示:

從理論上講,如果一個設計時序余量較大,所能跑的速度遠遠高于設計要求,那么就通過功能模塊的復用來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串并轉換的思想運行。

串并轉換是 FPGA 設計的一個重要技巧,它是數據流處理的常用手段,也是面積與速度互換思想的直接體現。串并轉換的實現方法多種多樣,根據數據的排序和數量的要求,可以選用寄存器、 RAM 等實現。

前面在乒乓操作的圖例中,就是通過 FIFO 實現了數據流的串并轉換,而且由于使用了 FIFO ,數據的緩沖區可以開得很大,對于數量比較小的設計可以采用寄存器完成串并轉換。如無特殊需求,應該用同步時序設計完成串并之間的轉換。比如數據從串行到并行,數據排列順序是高位在前,可以用下面的編碼實現:prl_temp

05. 流水線操作設計思想

流水線處理是高速設計中的一個常用設計手段。如果某個設計的處理流程分為若干步驟,而且整個數據處理是“ 單流向 ”的,即沒有反饋或者迭代運算,前一個步驟的輸出是下一個步驟的輸入,則可以考慮采用流水線設計方法來提高系統的工作頻率。

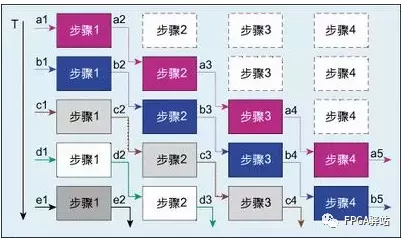

流水線設計的結構示意圖如圖所示。其基本結構為:將適當劃分的 n 個操作步驟單流向串聯起來。流水線操作的最大特點和要求是,數據流在各個步驟的處理從時間上看是連續的,如果將每個操作步驟簡化假設為通過一個 D 觸發器 ( 就是用寄存器打一個節拍 ) ,那么流水線操作就類似一個移位寄存器組,數據流依次流經 D 觸發器,完成每個步驟的操作。

流水線設計的一個關鍵在于整個設計時序的合理安排,要求每個操作步驟的劃分合理。如果前級操作時間恰好等于后級的操作時間,設計最為簡單,前級的輸出直接匯入后級的輸入即可;如果前級操作時間大于后級的操作時間,則需要對前級的輸出數據適當緩存才能匯入到后級輸入端;如果前級操作時間恰好小于后級的操作時間,則必須通過復制邏輯,將數據流分流,或者在前級對數據采用存儲、后處理方式,否則會造成后級數據溢出。

流水線處理方式之所以頻率較高,是因為復制了處理模塊,它是面積換取速度思想的又一種具體體現。

06. 異步時鐘處理原則

許多系統要求在同一設計內采用多時鐘,最常見的例子是“兩個異步微處理器之間的接口”或“微處理器和異步通信通道的接口”。由于兩個時鐘信號之間要求一定的建立和保持時間, 所以上述應用引進了附加的定時約束條件, 它們會要求將某些異步信號同步化。

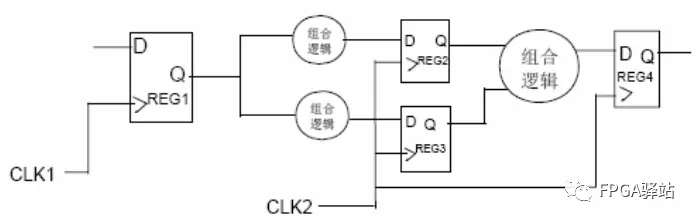

如果一個系統中存在多個獨立(異步)時鐘,并且存在多時鐘域(clock domain)之間的信號傳輸,那么電路會出現亞穩態。具體如下圖所示:

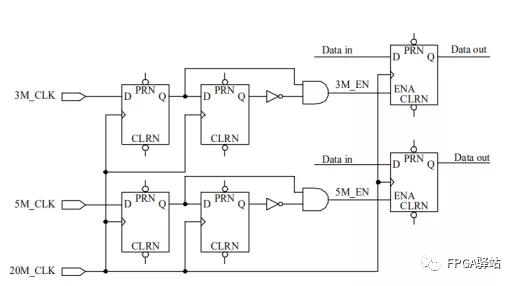

在許多應用中只將異步信號同步化還是不夠的,當系統中有兩個或兩個以上非同源時鐘的時候,數據的建立和保持時間很難得到保證,設計人員將面臨復雜的時間分析問題。最好的方法是將所有非同源時鐘同步化。這時就需要使用帶使能端的D觸發器, 并引入一個高頻時鐘來實現信號的同步化。具體如下圖所示:

07. 數據接口的同步原則

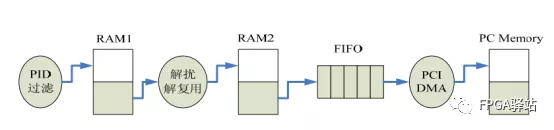

數據接口的同步是 FPGA/CPLD 設計的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據接口的同步有問題。輸入、輸出的延時 ( 芯片間、 PCB 布線、一些驅動接口元件的延時等 ) 不可測,或者有可能變動的條件下,如何完成數據同步?對于數據的延遲不可測或變動,就需要建立同步機制,可以用一個同步使能或同步指示信號。另外,使數據通過 RAM 或者 FIFO 的存取,也可以達到數據同步目的。

設計數據接口同步是否需要添加約束?建議最好添加適當的約束,特別是對于高速設計,一定要對周期、建立、保持時間等添加相應的約束。這里附加約束的作用有兩點:提高設計的工作頻率,滿足接口數據同步要求;獲得正確的時序分析報告。

08. 總 結

數字系統設計應該明確如下觀點:

1. 無論是ASIC、FPGA還是DSP,都只是一種實現手段;

2. 無論采用哪種HDL或哪種開發工具,都不能單純從語言或工具本身作出評價;

3. 關鍵是看應用環境,只有選擇最適合于應用的實現方式和工具才是最好的設計方案;

4. 設計應該注重硬件設計本身,只有先有了良好的設計,才可能有高效的描述和實現。

5. 數字模擬電路、HDL語言等知識和實際經驗比了解軟件更重要。比如FPGA一般觸發器資源豐富,CPLD的組合邏輯資源更加豐富。FPGA/CPLD一般是由底層可編程硬件單元、BRAM、布線資源、可配置IO單元、時鐘資源等構成。

?免責聲明:本文為網絡轉載文章,轉載此文目的在于傳播相關技術知識,版權歸原作者所有,如涉及侵權,請聯系小編刪除(聯系郵箱:service@eetrend.com )。

審核編輯:符乾江

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636268 -

設計

+關注

關注

4文章

826瀏覽量

71318

發布評論請先 登錄

探索IGLOO2 FPGA與SmartFusion2 SoC FPGA的電氣特性與應用潛力

Microsemi IGLOO2 FPGA與SmartFusion2 SoC FPGA深度剖析

SDH光端機組網原則:構建可靠通信網絡的核心規劃要點

合科泰揭秘電路設計中的可制造性原則

如何理解MOSFET器件溝道電荷分配原則

從入門到精通:PCB設計必須遵守的5大核心原則

浪涌保護器參數設置原則與行業安裝應用指南

Altera Agilex? 3 FPGA和SoC FPGA

智多晶FPGA設計工具HqFpga接入DeepSeek大模型

安路科技助力FPGA產學研深度融合 第一屆“國產FPGA教育大會”在重慶圓滿落幕

是否有關于如何通過 I2C 總線上的 uProcessor 或 FPGA 與芯片通信的文檔?

高速PCB布局/布線的原則

關于FPGA設計的幾項重要原則

關于FPGA設計的幾項重要原則

評論