文章來源:SPICE 模型

原文作者:若明

在模擬集成電路設計中,精確的MOSFET模型是確保電路性能預測準確性的基石。而溝道電荷分配原則,正是連接晶體管直流特性與交流特性的關鍵橋梁。如果簡單地認為所有電荷都均勻分配或不隨偏置變化,就會嚴重錯誤地估計電路的速度(fT)、延時和AC特性。今天,我們將從物理本質出發,深入解析這一重要概念。

為什么需要關注溝道電荷分配?

簡單來說:溝道電荷的分配方式直接決定了MOSFET的本征電容特性。

當我們分析電路的高頻性能、開關速度或穩定性時,晶體管的電容參數(Cgs、Cgd、Cgb等)起著決定性作用。這些電容并非固定值,而是隨著偏置電壓劇烈變化的非線性元件。 傳統的簡單模型認為溝道電荷均勻分布,但這與物理現實相去甚遠。

實際上:

在線性區(Vds很小),溝道電荷近似均勻分布

在飽和區(Vds > Vdsat),溝道在漏端夾斷,電荷分布極度不均勻

在亞閾值區,電荷分布又呈現不同的特征

如果忽略這種非均勻性,將嚴重誤判電路性能!

溝道電荷分配的物理本質

理論基礎:Ward-Dutton電荷分配模型 1978年,Ward和Dutton提出了奠基性的電荷導向模型。其核心思想是:基于電荷守恒原則,將總溝道電荷合理地"分配"到器件的四個端口(柵、源、漏、體)。

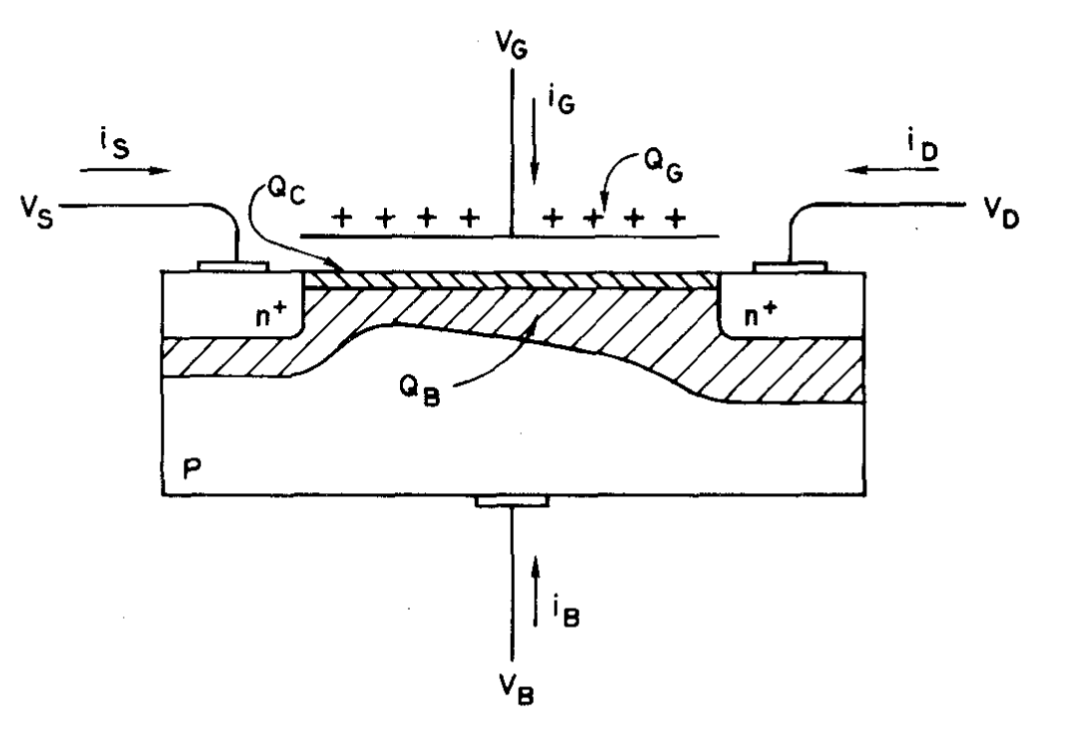

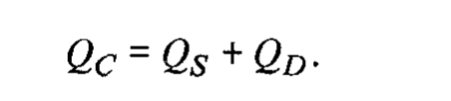

圖1:電荷導向模型 電荷導向模型:

所提出的模型基于MOS結構中的實際電荷分布(如圖1所示)。對于任何空間區域,我們可以寫:

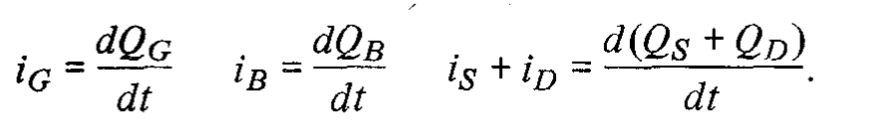

其中 i 是流入該區域的凈電流,Q 是該區域中包含的總電荷。因此,我們可以寫:

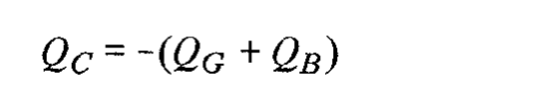

電荷守恒方程: QG+QS+QD+QB=0 其中總溝道電荷 QC可表示為:

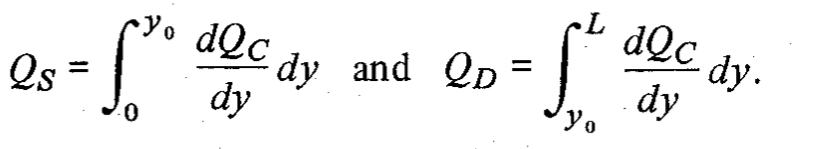

并且與源電荷和漏電荷有關:

不幸的是,漏極和源極電荷的定義不如柵極和體電荷,必須通過分配通道電荷來獲得。因此,我們必須有一個將Qc劃分為QD和QS的算法。這種拆分可以通過多種方式完成。

1. 物理分割

將溝道按照溝道中的某一點y0分割,y0=a*L,L是溝道長度,因此可以按照如下方式分配:

2. 數學分配

數學分配中,QD = b*Qc, QS = (1 - b)*Qc,其中0 <= b <= 1。通常,b 可能是端子電壓的函數。

在線性區,雖然溝道均勻,但載流子從源端注入,導致源端"感應"到更多電荷。在飽和區,溝道在漏端夾斷,幾乎沒有電荷歸屬于漏端,大部分電荷聚集在源端附近。通過理論推導和實驗驗證,我們得到了兩個經典分配規則:

線性區(40/60規則):

a) 漏端電荷 Qd ≈ 40% QI

b) 源端電荷 Qs ≈ 60% QI 飽和區(0/67規則):

a) 漏端電荷 Qd ≈ 0% QI b) 源端電荷 Qs ≈ 67% QI

c) 柵端電荷 Qg ≈ 33% QI

從理論到實踐:連續可微的分配函數

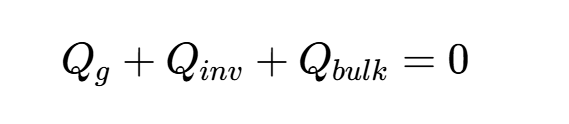

Tsividis的平滑過渡方案 經典的40/60和0/67規則只是兩個極端情況。在實際電路中,晶體管工作在連續的偏置范圍內,我們需要平滑的過渡函數。以BSIM3V3模型為例,我們簡單了解一下工程中是如何實現的。 BSIM3v3 將襯底電荷 Qbulk和反型層電荷 Qinv分開處理。總柵電荷 Qg滿足電荷守恒方程:

BSIM3v3 手冊中詳細描述了如何通過一個平滑函數將工作區域劃分為三個部分,并對溝道電荷進行分配。模型通過一個關鍵參數Vgsteff(有效的柵電壓過驅動)來平滑連接亞閾值區和強反型區。同時,通過另一個參數Vdseff(有效的漏源電壓)來平滑連接線性區和飽和區。

// *** BSIM3v3 電荷模型 Verilog-A 實現 , 部分代碼 ****// // 電荷計算核心函數 //================================================================== functioncalculate_charges; input Vgsteff, Vdseff, Vdsat, Abulk, Cox, W, L; realVgsteff, Vdseff, Vdsat, Abulk, Cox, W, L; // 電荷變量 realQinv_total, Qd, Qs, Qg, Qb; realx_share;// 電荷分配系數 begin // 6. 總反型層電荷計算 Qinv_total =calculate_Qinv_total(Vgsteff, Vdseff, Vdsat, Abulk, Cox, W, L); // 7. 電荷分配系數計算 - Ward-Dutton 方法 x_share =calculate_charge_partition(Vdseff, Vdsat); // 8. 各端口電荷計算 Qd = x_share * Qinv_total; // 分配到漏端的電荷 Qs = (1- x_share) * Qinv_total;// 分配到源端的電荷 Qb =calculate_bulk_charge(Vgsteff, Vbs, Cox, W, L);// 襯底電荷 Qg = -(Qinv_total + Qb); // 柵電荷 (電荷守恒) // 9. 使用ddt貢獻電荷到端口 I(g,s) <+?ddt(Qg); ? ??I(d,s) <+?ddt(Qd); ? ??I(s,d) <+?ddt(Qs);? ? ??I(b,s) <+?ddt(Qb); end endfunction

關鍵算法解析

1. 兩個核心平滑函數

Vgsteff- 亞閾值/強反型平滑過渡:

// Verilog-A 代碼 // 使用對數指數函數實現平滑過渡Verilog-A Vgsteff = Vtm *log(1+exp(Vgst / (n * Vtm)));Vdseff- 線性區/飽和區平滑過渡:

// Verilog-A 代碼 // 使用平方根函數避免導數不連續 Vdseff = Vdsat -0.5* (Vdsat - Vds - delta +sqrt((Vdsat - Vds - delta)^2+4* delta * Vdsat));

2. 電荷分配算法

BSIM3 使用連續的分配系數x_share:

// Verilog-A 代碼

// ==================================================================

// 電荷分配系數計算 - BSIM3核心算法

// ==================================================================

function real calculate_charge_partition;

input Vdseff, Vdsat;

real Vdseff, Vdsat;

real x, Fsat, beta;

begin

if(Vdsat ==0)begin

x=0.5;// 避免除零

endelsebegin

// 飽和因子

Fsat = Vdseff / Vdsat;

beta =2.0;// 平滑因子

// BSIM3 平滑分配函數

if(Fsat 0.9)begin

x=0.0;// 深飽和區

endelsebegin

// 過渡區平滑函數

x =0.5* pow(1- Fsat, beta);

end

end

calculate_charge_partition=x;

end

endfunction

總結

溝道電荷分配原則是MOSFET建模從"簡單近似"走向"物理精確"的關鍵一步。從Ward-Dutton的理論奠基,到Tsividis的平滑過渡方案,再到現代SPICE模型的工程實現,這一領域的發展體現了半導體建模的精髓:在物理精確性與計算效率之間尋求最佳平衡。

對于電路設計師而言,理解這一概念不僅有助于選擇正確的模型,更能深入理解器件工作的物理本質,從而在電路優化中做出更明智的決策。

-

集成電路

+關注

關注

5461文章

12634瀏覽量

375306 -

MOSFET

+關注

關注

151文章

10197瀏覽量

234399 -

電荷

+關注

關注

1文章

665瀏覽量

37397

原文標題:如何理解MOSFET器件溝道電荷分配原則

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何理解MOSFET器件溝道電荷分配原則

如何理解MOSFET器件溝道電荷分配原則

評論