大家好!轉(zhuǎn)眼又是年底了。這一年馬上要過去,不知道大家今年收獲到了什么呢?

高速ADC一直是個特別火的課題,無論是科研還是實際項目。與此同時,高速動態(tài)comparator的設(shè)計也就隨之非常普遍。在這里,作者君想跟大家分享一下自己所采用的兩種對comparator input referred noise的仿真方法。大家有什么疑問或者經(jīng)驗分享,請在評論區(qū)留言。

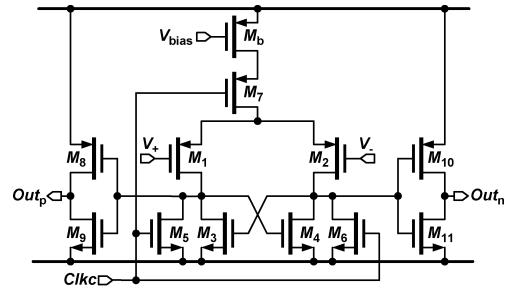

一個典型的dynamic comparator,如圖所示:

來自:Liu, Chun-Cheng, Soon-Jyh Chang, Guan-Ying Huang, and Ying-Zu Lin. “A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure.” IEEE Journal of Solid-State Circuits 45, no. 4 (2010): 731-740.

這篇來自CC.Liu的SAR ADC 設(shè)計,目前citations已經(jīng)過千,想必很多讀者都看過了。沒看過的建議去看看,確實是經(jīng)典。

對于一個這樣的comparator,沒有傳統(tǒng)的模擬pre-amp,整個電路都是dynamic的。因此,如何對input referred noise進行仿真呢?作者君有如下兩種方法:

Transient noise

大致的思路是這樣的:

加一個快于實際工作的時鐘頻率;

在輸入端加一個DC的差(比如一端是0.5VDD,另外一端加0.5VDD+0.2mV);

計算仿真時間內(nèi)的counting number,和correct counting number(比如時鐘頻率是1GHz,仿真時間是1us,那么應(yīng)該是1000個counts;用viva的calculator計算正確的counts);

掃描不同的輸入DC差之下,正確的counts的數(shù)量(比如輸入差是0.1mV,0.2mV,0.3mV,etc.);

當(dāng)正確的counts數(shù)量大約是84%的時候,我們認為此時的input差就是一個sigma(50%+0.5*68%=84%);

當(dāng)PVT改變的時候,可以不斷重復(fù)上面的步驟,來求得對應(yīng)的sigma;

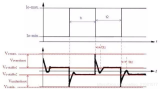

Transient Noise settings and simulation results (Input difference is 0.1mV)

作者君的transient noise設(shè)置和仿真結(jié)果如上圖。可以看到,當(dāng)input的差別很小的時候(Vip大于Vin),本來應(yīng)該是只有Vop出現(xiàn)pulse,Von全部應(yīng)該是0。但是由于noise的存在,導(dǎo)致某些錯誤的輸出。

按照前面的方法,用calculator計算出全部和正確的counts數(shù)量。可以看到,目前的正確counts大概是84%,也就是對于一個input referred noise sigma.

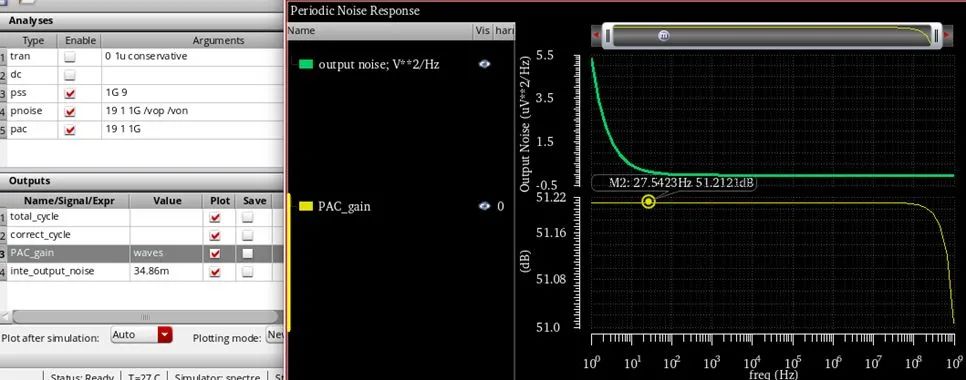

PSS+Pnoise

大致的思路是這樣的:

加一個快于實際工作的時鐘頻率;

在輸入端加一個DC的差;

采用PSS,PAC, Pnoise的仿真;

Pnoise計算出integrated output noise(用V^2/Hz作積分然后sqrt做開方);

PAC計算出comparator的gain;

第四步得到的noise除以第五步得到的gain,就是input referred noise;

Input difference is 0.1mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 34.86mV.With PAC gain of 51dB (363.584), the input referred noise is 0.096mV ~ 0.1mV.

相比于Transient noise,這種pnoise的方法一步就能得出input referred noise;所以也有paper專門對比過效率。

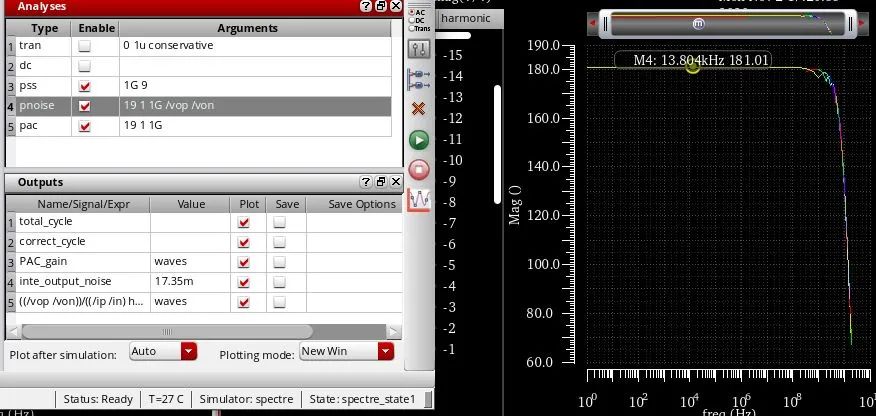

上面這張圖是input差為0.1mV時候的仿真結(jié)果。作者君又勤快了點,多跑了一個仿真:

Input difference is 0.2mV.Pnoise integration is from 1Hz to 500MHz. The output noise is 17.35mV.With PAC gain of 45dB (181), the input referred noise is 0.096mV ~ 0.1mV.

當(dāng)input差別變成0.2mV的時候,相對應(yīng)的輸出pnoise變小了差不多一半(34mV變成17mV),同樣的,PAC得到的增益gain也減小了一半。因此,最后得到的input referred noise也基本上沒變。

最后,對比一下transient noise 和Pnoise的結(jié)果,可以看到,我們拿到的input referred noise差不多都是0.1mV。哈哈哈,結(jié)果挺相符的,太棒了!(作者君這個comparator做得不錯吧?加大input pair的size真的是挺有用的……就是面積有點大……囧)

參考文獻:

https://www.cadence.com/content/dam/cadence-www/global/en_US/videos/tools/custom-_ic_analog_rf_design/NoiseAnalyisposting201612Chalk%20Talk.pdf

https://www.researchgate.net/publication/270105586_Noise-aware_simulation-based_sizing_and_optimization_of_clocked_comparators

PS:關(guān)于加的時鐘頻率比實際工作頻率要高這點,作者君不是特別確定。希望讀者們可以給出評論。謝謝大家!

在正常的用vpwl sweep comparator一端,固定另外一端的transient仿真時,比如工作頻率是250MHz,可能出現(xiàn)因為時鐘上升沿剛好沒有對齊輸入過零點導(dǎo)致的誤差。這種情況下,加500MHz的時鐘,可能會避免出現(xiàn)這種誤差。

編輯:jq

-

噪聲

+關(guān)注

關(guān)注

13文章

1156瀏覽量

49223 -

仿真

+關(guān)注

關(guān)注

54文章

4482瀏覽量

138244 -

Comparator

+關(guān)注

關(guān)注

0文章

120瀏覽量

33803

原文標題:Comparator動態(tài)噪聲的仿真

文章出處:【微信號:analogIC_gossip,微信公眾號:通向模擬集成電路設(shè)計師之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

解析矢量網(wǎng)絡(luò)分析儀核心參數(shù):動態(tài)范圍

是德頻譜分析儀N9322C相位噪聲測量的實用指南

過采樣技術(shù)如何提高ADC的動態(tài)性能

ADM-10699PSM寬帶低噪聲放大器

eVTOL艙內(nèi)噪聲響應(yīng)分析的仿真流程

使用FSWP相位噪聲分析儀進行動態(tài)噪聲系數(shù)測量

電動機噪聲、振動和聲振粗糙度開發(fā):使用低計算成本的系統(tǒng)級模型預(yù)測早期噪聲、振動和聲振粗糙度

無刷直流電機狀態(tài)方程系數(shù)矩陣的動態(tài)更新

同步電機失步淺析

三相異步電機切換過程的動態(tài)分析與系統(tǒng)仿真

詳解ADC電路的靜態(tài)仿真和動態(tài)仿真

求助,關(guān)于二階巴特沃斯低通濾波器中電阻噪聲曲線出現(xiàn)波峰的問題求解

EMC 時鐘信號的噪聲源頭是什么?

淺析Comparator動態(tài)噪聲的仿真

淺析Comparator動態(tài)噪聲的仿真

評論