orcad怎么去瀏覽DRC檢測過后的全部DRC錯誤呢?

答:對原理圖文件進行DRC檢測以后,按照設置的DRC檢測的選項,會在原理圖中留下DRC的標記,對于分頁的原理圖來說,每一頁每一頁的去查看DRC的標記,比較繁瑣,這里可以運用Browse功能,查看所有的DRC,操作方法如下:

第一步,選中原理圖的根目錄,執行菜單Edit→Browse功能,然后選擇DRC Marks,進行DRC標記的查看。

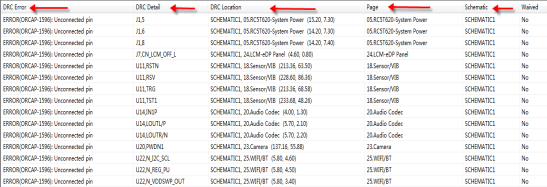

第二步,執行命令以后,如圖3-67所示,DRC ERROE顯示的是錯誤的類型說明,DRC Detail顯示的是該錯誤所屬器件與位號,DRC Location顯示的是DRC的位置,Page顯示的DRC所在的頁面。

圖3-67 DRC Marks顯示示意圖

責任編輯:haq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

檢測

+關注

關注

5文章

4859瀏覽量

94138 -

DRC

+關注

關注

2文章

156瀏覽量

38172

原文標題:【知識分享】34.orcad怎么去瀏覽DRC檢測過后的全部DRC錯誤呢?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+第六章節 PCB設計

規則設計好,選好檢查哪些項目,檢查的標準就是規則里面的內容。

PCB投產后能不能調試好,都是靠DRC檢查來判定的,不然這里短路,那里不同怎么辦。

檢查后,根據檢查結果來修改自己PCB中的錯誤項就行。

最后最好再來下DFM分析

一般使用的都是華秋。

發表于 02-26 11:05

altium designer 如何畫短路兩個或者三個網絡的封裝?

如何我畫了一個天線,有3個引腳,TX1,TX2,GND, 但實際上這三個引腳是連在一起的。我導入pcb后,會報DRC警告,這個該怎么解決?

發表于 02-12 19:30

從設計階段排查預防PCB短路

問題確實可能被遺漏,從而不產生報錯:

1)使用錯誤的鋪銅對象,使用“實心填充 (Fill) ”而非“智能鋪銅 (Polygon Pour) ”,前者會無條件連接覆蓋區域內所有對象,可能導致短路而DRC

發表于 01-23 13:55

西門子PCB仿真分析工具HyperLynx 2510版本的新增功能

HyperLynx 2510 新版在原理圖分析、AMS、DRC、信號和電源完整性、高階解算器和企業數據管理方面帶來了一系列豐富的增強功能。這些更新提升了可用性、準確性和集成度,助力加快電子系統設計驗證與優化。我們一起來了解其中的亮點。

生成Bitstream的DRC LUTLP-1錯誤的解決辦法

vivado綜合和實現完成后,在生成Bit文件時出現已知設計原理的DRC錯誤。下面圖中的DRC LUTLP-1的loop錯誤是設計可接受的的。

且對仿真結果不影響,綜合實現都通過,到

發表于 10-30 07:42

Cortex-M0+處理器的HardFault錯誤介紹

在ARM處理器中,如果一個程序產生了錯誤并且被處理器檢測到,就會產生錯誤異常。Cortex-M0+處理器只有一種異常用以處理錯誤:HardFault。

華大九天Argus DRC技術詳解

在芯片設計領域,物理驗證是保障芯片成功流片且符合制造要求的核心要素。而設計規則檢查(DRC)作為物理驗證的關鍵環節,發揮著舉足輕重的作用。DRC主要聚焦于檢查芯片版圖設計是否契合制造工藝的設計規則

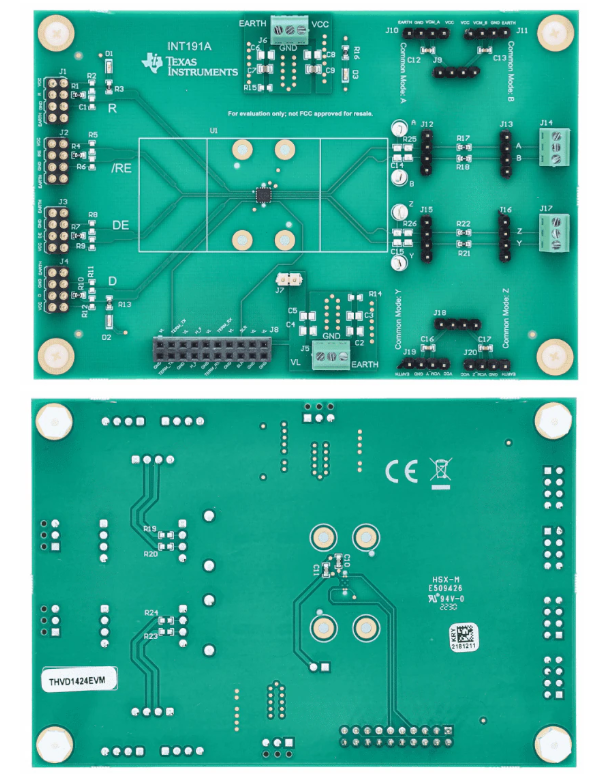

THVD1424EVM評估模塊技術解析與應用指南

exas Instruments THVD1424EVM評估模塊支持快速、輕松地評估THVD1424。THVD1424是一款全雙工RS-485收發器,具有可選數據速率和可切換集成端接電阻器,采用16-VQFN (RJT) 封裝。TI THVD1424EVM評估模塊開箱即用,預裝有THVD1424DRC。

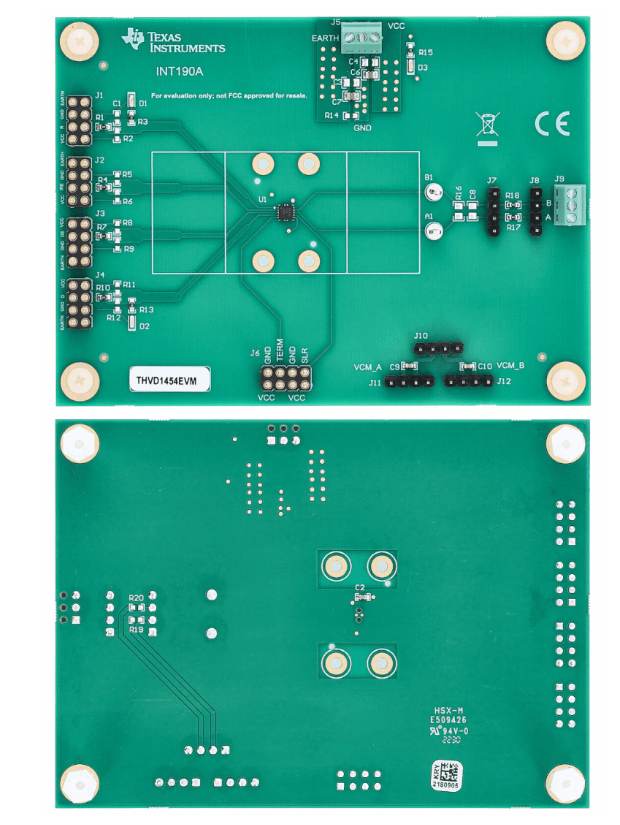

?TI THVD1454EVM評估模塊技術解析與應用指南

Texas Instruments THVD1454EVM評估模塊設計用于快速輕松地演示THVD1454。THVD1454是一款半雙工RS-485收發器,具有可選數據速率和可切換集成端接電阻器,采用10-VSON (DRC) 封裝。TI THVD1454EVM評估模塊開箱即用,預裝有THVD1454。

凡億Allegro Skill工藝輔助之導出公制的坐標

一般設計人員在pcb設計時使用英制單位,而在pcb設計完成后,我們需要導出坐標文件用于貼片廠進行貼片;有的板廠要求導出的坐標文件為公制單位,切換單位會比較麻煩且容易產生DRC錯誤或者誤差,因此,Fanyskill腳步提供一鍵輸出公制坐標的功能。

CX3 是否有可以檢測 MIPI CSI-2 RX 錯誤的寄存器?

CX3 是否有可以檢測 MIPI CSI-2 RX 錯誤的寄存器?

如果有可以檢測上述錯誤的寄存器,請告訴我詳細信息,包括如何檢查。

發表于 07-15 07:39

Microchip通過設計內signoff DRC在成熟節點定制IC設計中實現顯著的生產率提升

版圖設計人員和 CAD 工程師利用多種工具,例如 Calibre RealTime 平臺和 Calibre nmDRC Recon 早期設計 DRC 工具,來加速他們的 DRC 收斂過程,從而將其流片計劃縮短數周之多。

發表于 04-13 17:33

?958次閱讀

orcad怎么去瀏覽DRC檢測過后的全部DRC錯誤

orcad怎么去瀏覽DRC檢測過后的全部DRC錯誤

評論