賽靈思 Versal 自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 設(shè)計(jì)方法論是旨在幫助精簡(jiǎn) Versal 器件設(shè)計(jì)進(jìn)程的一整套最佳實(shí)踐。鑒于這些設(shè)計(jì)的規(guī)模與復(fù)雜性,因此必須通過(guò)執(zhí)行特定步驟與設(shè)計(jì)任務(wù)才能確保設(shè)計(jì)每個(gè)階段都能成功完成。

本指南將分為以下五大章節(jié),遵循指南里的步驟和最佳實(shí)踐進(jìn)行操作,將有助于您以盡可能最快且最高效的方式實(shí)現(xiàn)期望設(shè)計(jì)目標(biāo)。

PART 1

仿真流程

為了應(yīng)對(duì)仿真范圍、仿真抽象和仿真目的等方面的不同需求,賽靈思為 Versal ACAP 設(shè)計(jì)的各組件提供了專用的流程,包括 AI 引擎、PS 和 PL。此外,賽靈思還支持對(duì)由 PL、PS 和(可選)AI 引擎組件組成的完整系統(tǒng)進(jìn)行協(xié)同仿真。

具體章節(jié)提供了有關(guān)每個(gè)仿真流程的范圍和目的的詳細(xì)信息,請(qǐng)您下載完整版指南進(jìn)行查閱。

PART 2

設(shè)計(jì)收斂

設(shè)計(jì)收斂包括滿足所有系統(tǒng)性能、時(shí)序和功耗要求,并成功確認(rèn)硬件中的功能。在設(shè)計(jì)收斂階段,您可開(kāi)始通過(guò)實(shí)現(xiàn)工具運(yùn)行設(shè)計(jì),因此首先需要考量的就是時(shí)序和功耗注意事項(xiàng)。

在此設(shè)計(jì)收斂階段、估算設(shè)計(jì)利用率,時(shí)序和功耗可以得到準(zhǔn)確性更高的結(jié)果。這樣即可為您提供機(jī)會(huì)來(lái)重新確認(rèn)時(shí)序和功耗目標(biāo)是可達(dá)成的。為確認(rèn)設(shè)計(jì)能夠滿足其要求,賽靈思建議制定時(shí)序基線和功耗基線。時(shí)序基線側(cè)重于在定義準(zhǔn)確的時(shí)序約束之后,評(píng)估時(shí)序路徑。功耗基線則需要為 Vivado 提供正確的翻轉(zhuǎn)信息,以便確定準(zhǔn)確的動(dòng)態(tài)功耗信息。

當(dāng)您基于基線開(kāi)始迭代后,應(yīng)在改善時(shí)序時(shí)復(fù)檢功耗數(shù)值。通常,建議您盡早開(kāi)啟整套功耗節(jié)省功能,然后對(duì)導(dǎo)致出現(xiàn)時(shí)序問(wèn)題的個(gè)別項(xiàng)進(jìn)行縮減,這樣有助于達(dá)成適當(dāng)?shù)钠胶猓瑥亩鴿M足設(shè)計(jì)收斂目標(biāo)。在實(shí)現(xiàn)階段盡早聯(lián)動(dòng)開(kāi)展功耗分析和時(shí)序分析能夠節(jié)省工程設(shè)計(jì)時(shí)間,實(shí)現(xiàn)更準(zhǔn)確的工程規(guī)劃。這樣即可留出更多時(shí)間用于探索各種工程設(shè)計(jì)解決方案,不至于在設(shè)計(jì)周期后期才發(fā)現(xiàn)更合適的解決方案。

PART 3

系統(tǒng)性能收斂

Versal 器件是圍繞異構(gòu)計(jì)算引擎來(lái)構(gòu)建的,這些引擎通過(guò) NoC 或 PL 彼此相連并通過(guò)高性能收發(fā)器和 I/O 連接到外部系統(tǒng)。在系統(tǒng)應(yīng)用與映射階段,器件接口和總體計(jì)算要求可用于指定器件中實(shí)現(xiàn)的每個(gè)計(jì)算和控制功能的目標(biāo)性能。每個(gè)功能都設(shè)計(jì)為映射到最合適的硬件資源,此類資源使用對(duì)應(yīng)編程語(yǔ)言和編譯軟件(例如,對(duì)應(yīng)嵌入式處理器系統(tǒng)使用系統(tǒng)軟件,對(duì)應(yīng) AI 引擎或 PL 內(nèi)核使用 C/C++ 語(yǔ)言、對(duì)應(yīng)高性能 PL 內(nèi)核或固件則使用 RTL 等)。

各設(shè)計(jì)團(tuán)隊(duì)必須先在功能級(jí)別確認(rèn)功能和期望的性能,然后再將其集成到部分系統(tǒng)應(yīng)用或整個(gè)系統(tǒng)中。在集成階段中,功能可能失效,且性能可能降級(jí)。由于 Versal 器件所支持的系統(tǒng)應(yīng)用的復(fù)雜性和異構(gòu)性質(zhì),因此必須事先明確并規(guī)劃分析和調(diào)試方法論。

Vitis 和 Vivado 工具均為綜合性且互補(bǔ)性的設(shè)計(jì)環(huán)境,可提供在硬件中進(jìn)行功能仿真、設(shè)計(jì)特性報(bào)告以及數(shù)據(jù)測(cè)量或探測(cè)所需的所有功能。具體章節(jié)提供了分步驟分析方法建議,詳情請(qǐng)下載完整版指南進(jìn)行查閱。

PART 4

配置與調(diào)試

成功完成設(shè)計(jì)實(shí)現(xiàn)后,下一步就是將設(shè)計(jì)加載到器件中并在硬件上運(yùn)行。配置是指將特定應(yīng)用的數(shù)據(jù)加載到器件內(nèi)部存儲(chǔ)器中的過(guò)程。如果設(shè)計(jì)在硬件上不滿足要求,則需要進(jìn)行調(diào)試。具體詳細(xì)信息,可參閱相關(guān)資源獲取。

PART 5

確認(rèn)

Versal ACAP 的多種不同計(jì)算域給傳統(tǒng) FPGA 確認(rèn)方法帶來(lái)了諸多挑戰(zhàn)。除了可編程邏輯和處理器子系統(tǒng)外,Versal器件還包含 AI 引擎,使系統(tǒng)確認(rèn)任務(wù)比傳統(tǒng) FPGA 更復(fù)雜。

此確認(rèn)方法是圍繞以下關(guān)鍵概念構(gòu)建的:

? 塊/IP 確認(rèn):PL 內(nèi)各 RTL 和 HLS IP 可先單獨(dú)確認(rèn),然后再執(zhí)行系統(tǒng)集成。

? AI 引擎確認(rèn):位于接口級(jí)別的 AI 引擎可視作為 AXI-MM 或 AXI4-Stream IP。

? 系統(tǒng)確認(rèn):完成各塊確認(rèn)后,即可確認(rèn)整個(gè)系統(tǒng)、使用處理器來(lái)協(xié)調(diào)數(shù)據(jù)流、測(cè)試矢量生成、監(jiān)控等。

責(zé)任編輯:haq

-

仿真

+關(guān)注

關(guān)注

55文章

4526瀏覽量

138587 -

ACAP

+關(guān)注

關(guān)注

1文章

54瀏覽量

8746

原文標(biāo)題:Versal ACAP 系統(tǒng)集成和確認(rèn)方法指南

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

賽靈思FPGA電源解決方案全解析

AMD Versal自適應(yīng)SoC中eMMC燒錄/啟動(dòng)調(diào)試檢查表(上)

使用Aurora 6466b協(xié)議實(shí)現(xiàn)AMD UltraScale+ FPGA與AMD Versal自適應(yīng)SoC的對(duì)接

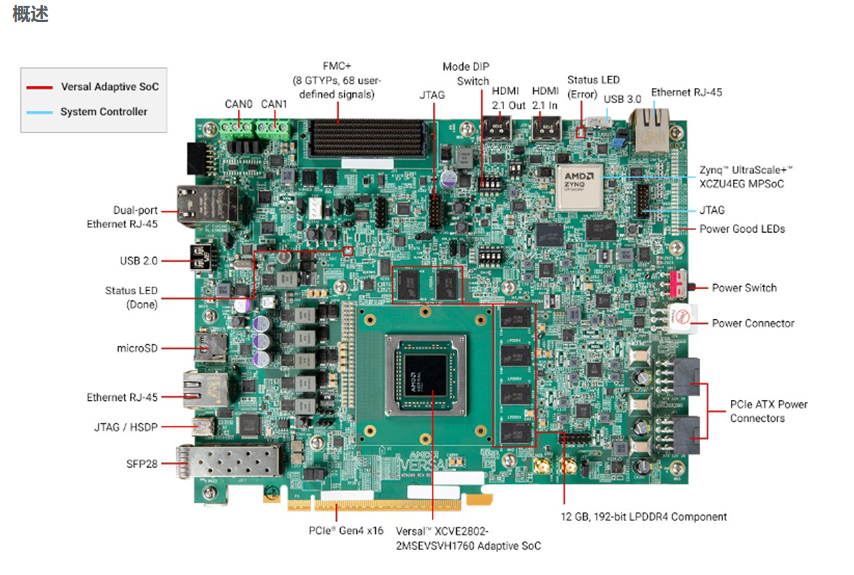

工程師必入!288 元解鎖賽靈思開(kāi)發(fā)板

AMD Versal自適應(yīng)SoC內(nèi)置自校準(zhǔn)的工作原理

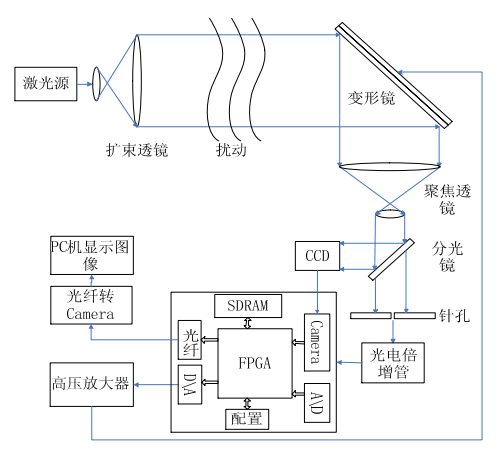

高壓放大器驅(qū)動(dòng):基于FPGA的SPGD自適應(yīng)光學(xué)控制平臺(tái)的探索

MicroBlaze V處理器嵌入式設(shè)計(jì)用戶指南

電磁干擾自適應(yīng)抑制系統(tǒng)平臺(tái)全面解析

在AMD Versal自適應(yīng)SoC上使用QEMU+協(xié)同仿真示例

利用AMD VERSAL自適應(yīng)SoC的設(shè)計(jì)基線策略

Versal 600G DCMAC Subsystem LogiCORE IP產(chǎn)品指南

適用于Versal的AMD Vivado 加快FPGA開(kāi)發(fā)完成Versal自適應(yīng)SoC設(shè)計(jì)

第二代AMD Versal Premium系列SoC滿足各種CXL應(yīng)用需求

面向AI與機(jī)器學(xué)習(xí)應(yīng)用的開(kāi)發(fā)平臺(tái) AMD/Xilinx Versal? AI Edge VEK280

賽靈思Versal自適應(yīng)計(jì)算加速平臺(tái)指南

賽靈思Versal自適應(yīng)計(jì)算加速平臺(tái)指南

評(píng)論