AMD 自適應(yīng)計算文檔按一組標(biāo)準(zhǔn)設(shè)計進(jìn)程進(jìn)行組織,以便幫助您查找當(dāng)前開發(fā)任務(wù)相關(guān)的內(nèi)容。您可以在設(shè)計中心頁面上訪問 AMD Versal 自適應(yīng) SoC 設(shè)計進(jìn)程。您還可以使用設(shè)計流程助手來更深入了解設(shè)計流程,并找到特定于預(yù)期設(shè)計需求的內(nèi)容。本文檔涵蓋了以下設(shè)計進(jìn)程:

嵌入式軟件開發(fā):基于硬件平臺來創(chuàng)建軟件平臺,并使用嵌入式 CPU 開發(fā)應(yīng)用代碼。還涵蓋 XRT 和計算圖 API。本文檔中適用于此設(shè)計進(jìn)程的主題包括:

第 2 章:在嵌入式設(shè)計中使用 MicroBlaze V 處理器

硬件、IP 和平臺開發(fā):為硬件平臺創(chuàng)建 PL IP 塊、創(chuàng)建 PL 內(nèi)核、功能仿真以及評估 AMD Vivado 時序收斂、資源使用情況和功耗收斂。還涉及為系統(tǒng)集成開發(fā)硬件平臺。本文檔中適用于此設(shè)計進(jìn)程的主題包括:

第 3 章:含存儲器 IP 核的設(shè)計

第 4 章:IP integrator 中的復(fù)位和時鐘拓?fù)浣Y(jié)構(gòu)

器件工具流程概述

AMD Vivado 工具基于處理器提供了特定的編程流程。Vivado IDE 使用 IP integrator 搭配圖形化連接屏幕以指定器件、選擇外設(shè)和配置硬件設(shè)置。

您可使用 IP integrator 捕獲硬件平臺信息并導(dǎo)出 XML 格式的應(yīng)用程序,搭配其他數(shù)據(jù)文件來為 AMD 處理器開發(fā)設(shè)計。各軟件設(shè)計工具使用 XML 來執(zhí)行以下任務(wù)。

創(chuàng)建并配置板級支持包( BSP )庫

推斷編譯器選項

對處理器邏輯( PL )進(jìn)行編程

定義 JTAG 設(shè)置

自動執(zhí)行需要有關(guān)硬件的信息的其他操作

AMD MicroBlaze V 嵌入式處理器是精簡指令集計算機(jī)( RISC )核,專為在 AMD 現(xiàn)場可編程門陣列( FPGA 和自適應(yīng) SoC )中實現(xiàn)而優(yōu)化。該核基于 RISC-V 開源指令集架構(gòu)。

要創(chuàng)建嵌入式 MicroBlaze V 處理器設(shè)計,請參閱第 2 章:在嵌入式設(shè)計中使用 MicroBlaze V 處理器,以便了解如何使用 IP integrator 和其他 AMD 工具。如需了解更多處理器信息,請參閱《MicroBlaze V 處理器參考指南》( UG1629 )。

AMD 提供了設(shè)計工具,用于為 AMD 處理器開發(fā)和調(diào)試軟件應(yīng)用,包括但不限于:

軟件 IDE

基于 GNU 的編譯器工具鏈

調(diào)試工具

這些工具支持您開發(fā)無需操作系統(tǒng)的裸機(jī)應(yīng)用和用于基于開源 Linux 操作系統(tǒng)的應(yīng)用。

AMD 提供硬件設(shè)計和軟件開發(fā)集成,并支持集成流程向下延伸至 AMD Vitis 軟件平臺。Vitis 是獨(dú)立產(chǎn)品,可從 AMD 網(wǎng)站下載。如需了解有關(guān)該工具使用方法的更多信息,請參閱《Vitis 統(tǒng)一軟件平臺文檔》。

注釋:MicroBlaze V 要求使用 Vitis Unified IDE。

在嵌入式設(shè)計中使用 MicroBlaze V 處理器

AMD Vivado IDE IP integrator 是一款強(qiáng)大的工具,支持您將基于處理器的系統(tǒng)縫合在一起。

MicroBlaze V 嵌入式處理器是專為在 AMD 現(xiàn)場可編程門陣列( FPGA )中實現(xiàn)而優(yōu)化的精簡指令集計算機(jī)( RISC )。

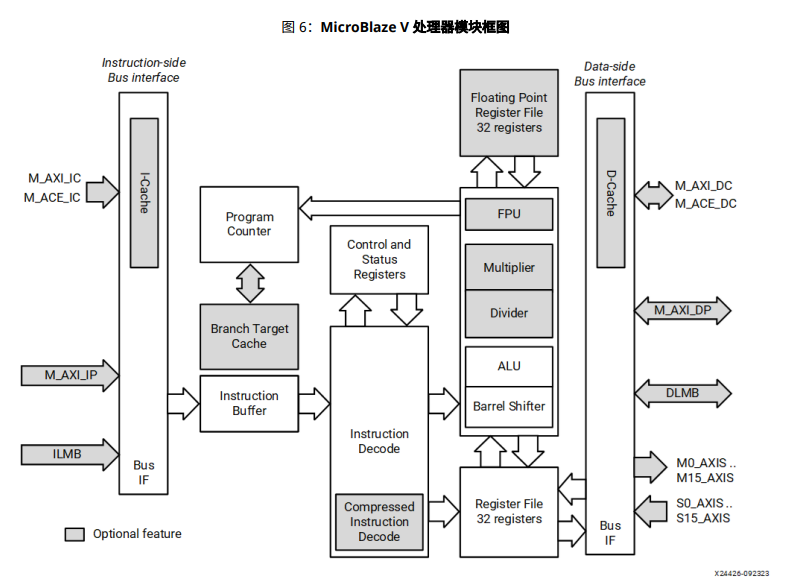

下圖顯示了該 MicroBlaze V 核的功能模塊框圖。

MicroBlaze V 處理器高度可配置。您可按設(shè)計所需選擇一組特定的功能特性。固定的處理器功能集包括:

32 個 32 位或 64 位通用寄存器

32 位指令字

32 位地址總線,可擴(kuò)展至 64 位

單發(fā)射流水線

除這些固定功能特性外,MicroBlaze V 處理器還包含參數(shù)化值,支持有選擇地啟用附加功能。

如需了解更多信息,請參閱《MicroBlaze V 處理器參考指南》( UG1629 )。

根據(jù)用戶要求,MicroBlaze V 可作為 32 位處理器或 64 位處理器來實現(xiàn)。一般來說,除非無法滿足特定要求,否則 AMD 建議您選擇 32 位處理器實現(xiàn)。64 位處理器會將通用寄存器擴(kuò)展到 64 位,提供指令用于處理 64 位數(shù)據(jù),并能使用最多 64 位地址對指令和數(shù)據(jù)進(jìn)行透明化尋址。

另請參閱《Triple Modular Redundancy( TMR )LogiCORE IP 產(chǎn)品指南》( PG268 ),其中提供了適用于 AMD 器件的軟核錯誤檢測、糾正和恢復(fù)。本指南描述了該解決方案所包含的 IP 核,并解釋了各種典型用例。

-

處理器

+關(guān)注

關(guān)注

68文章

20298瀏覽量

253603 -

amd

+關(guān)注

關(guān)注

25文章

5696瀏覽量

140231 -

存儲器

+關(guān)注

關(guān)注

39文章

7745瀏覽量

171999

原文標(biāo)題:MicroBlaze V 處理器嵌入式設(shè)計用戶指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

深度解析ADSP - TS101S TigerSHARC嵌入式處理器

ADSP - BF561:高性能嵌入式對稱多處理器的深度解析

ADSP - BF592:高性能嵌入式處理器的全方位解析

過時的 Blackfin 嵌入式處理器:ADSP - BF51x 系列

AMD銳龍AI嵌入式P100系列處理器產(chǎn)品簡介

什么是嵌入式應(yīng)用開發(fā)?

AMD重磅打造邊緣AI,CES2026官宣這顆嵌入式處理器!

AMD推出 EPYC 嵌入式 2005 系列處理器 滿足長期部署需求

為什么RISC-V是嵌入式應(yīng)用的最佳選擇

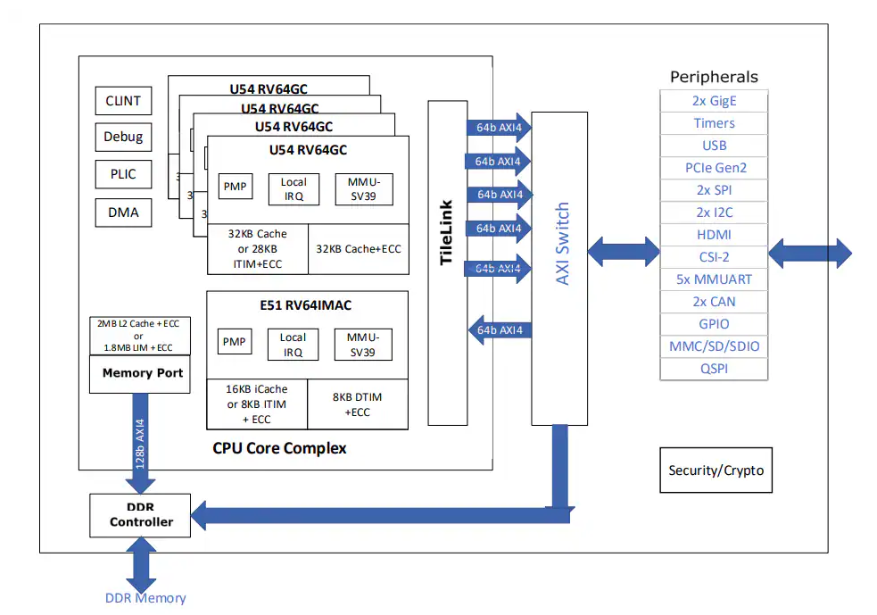

PIC64GX1000 RISC-V MPU:一款面向嵌入式計算的高性能64位多核處理器

AMD 推出 EPYC? 嵌入式 4005 處理器,助力低時延邊緣應(yīng)用

MicroBlaze處理器嵌入式設(shè)計用戶指南

AMD嵌入式處理器為您的應(yīng)用添能助力

嵌入式開發(fā)入門指南:從零開始學(xué)習(xí)嵌入式

嵌入式主板開發(fā)詳細(xì)指南

MicroBlaze V處理器嵌入式設(shè)計用戶指南

MicroBlaze V處理器嵌入式設(shè)計用戶指南

評論