自去年起,臺積電和三星等晶圓代工廠紛紛推出了5nm的工藝,如今更是在鉆研5nm以下的先進制程。但制程的提升不單單只靠EUV光刻機就能輕易實現的,短溝道效應使得傳統的FinFET技術已經滿足不了更高的半導體工藝。

目前的工藝水平在深度學習、圖形分析等基礎AI應用上已經可以滿足要求,但在神經形態芯片和量子計算上,仍需要更先進的制程來提供支持。面對這些挑戰,三星、臺積電和英特爾紛紛選擇了GAA技術來突破這一壁障。

GAA何時面世?

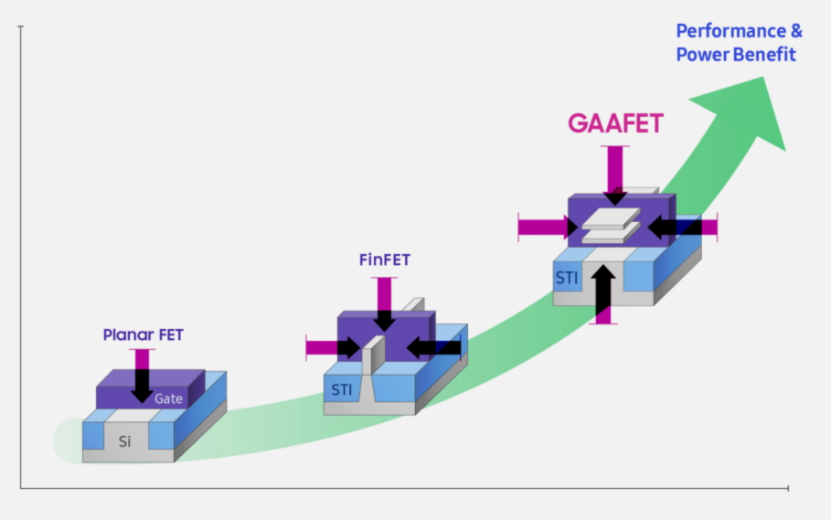

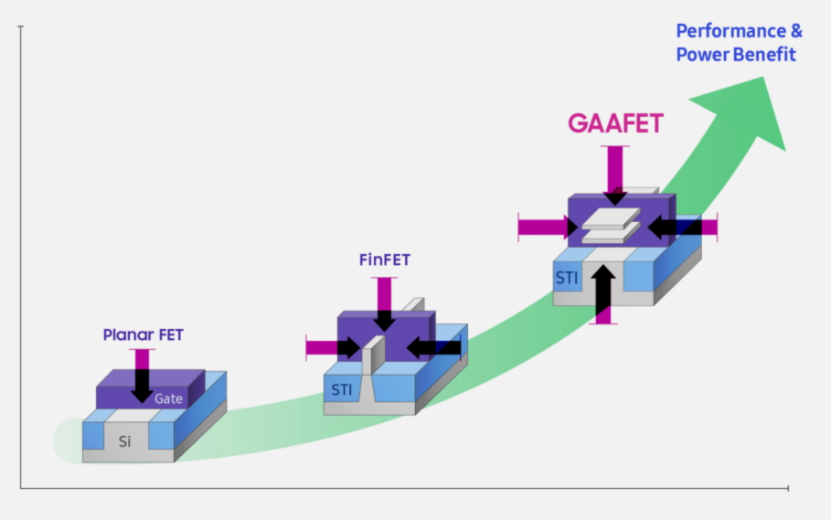

晶體管結構的演進 / 三星

三星在2019年就公布了其GAA 技術MBCFET,并發布了初版PDK。GAA結構進一步提到了柵極與溝道之間的接觸面積,并支持垂直堆疊的方式來獲得更強的載流能力,而非像FinFET一樣橫向堆疊鰭片。三星也同時宣布,將在3nm工藝節點引入GAA技術。根據三星給出的PPA數據,先進節點的MBCFET與7nm的FinFET相比,功耗減少50%,性能提升30%,面積減小了50%。

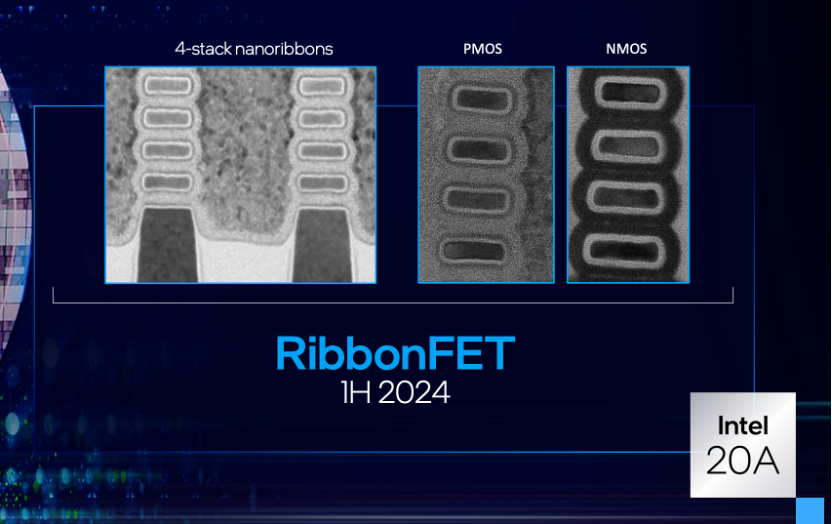

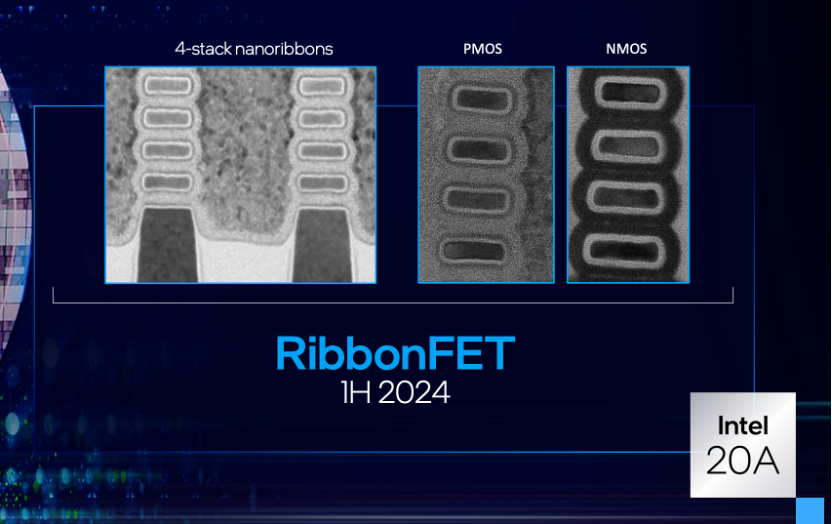

堆疊四層納米帶的RibbonFET / 英特爾

IBM全球首發的2nm芯片上,也用到了納米片GAA技術。今年6月底,三星宣布與新思合作的3nm GAA試產芯片已經成功流片。根據目前的消息來看,預計三星會在2022年推出早期GAA技術的制程3GAE,在2023年推出基于MBCFET的3GAP。英特爾也在近期的Intel Accelerated發布會中宣布,將在其20A工藝節點中引入其GAA技術RibbonFET,預計2024年上半年推出。而臺積電則在今年的技術論壇上宣布,FinFET技術只會用到3nm,2nm將用納米片晶體管來取代現有結構。

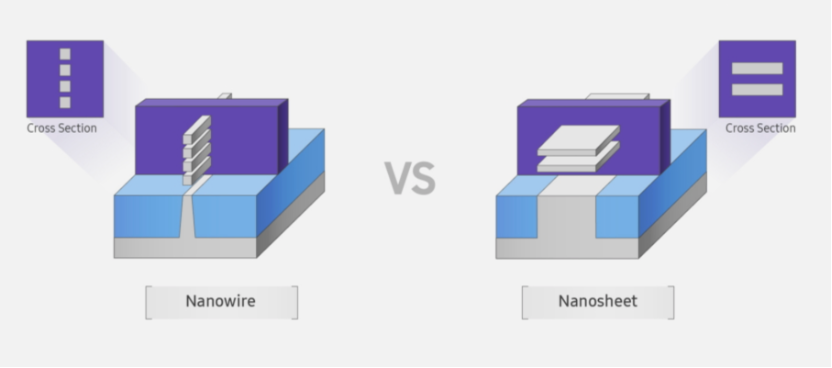

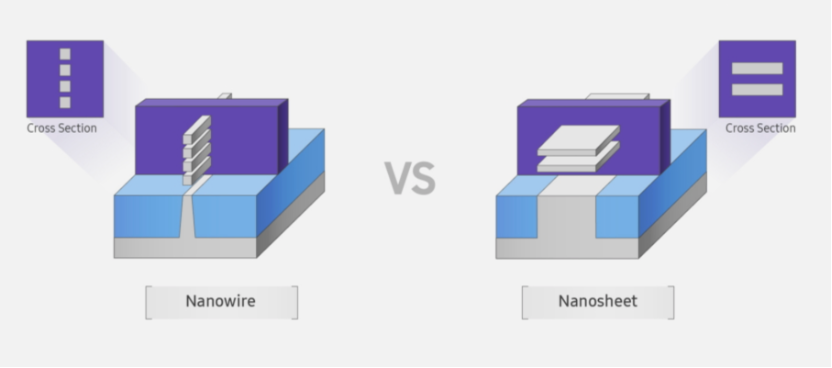

然而令許多人不解的是,GAA中通道的命名有納米線、納米片和納米帶,這些究竟是營銷術語不同,還是另有玄機呢?

納米線、納米帶與納米片

其實這些并不是花哨的營銷術語,而是對通道物理特質不同的描述。納米線的寬度和通道厚度基本相近,而納米片則選擇了更大的寬度,納米帶則是一個折中的方案,也可以看做是寬度更小的納米片。那么不同的通道對其性能又有何影響呢?由于2D結構約束所帶來優秀的短溝道特性,納米線在低功率應用上的表現更好。而納米片因為更大有效寬度實現了更大的接觸面積,載流性能要更為優異,適合一些高性能的應用,

納米線與納米片的截面對比 / 三星

雖然通道有所差異,但三星等廠商都不約而同的采用了堆疊通道的方式來繼續增加GAA結構的載流性能。不過FinFET中的鰭并不能無限疊加,GAA中的通道也是如此。這種載流能力的提升速度會隨著源極/漏極外延處的寄生電阻而減慢,不僅如此,柵極電容也會隨著通道數的增加而增大,因此為了保證最小的RC延遲,GAA一般會選擇3或4的通道數。

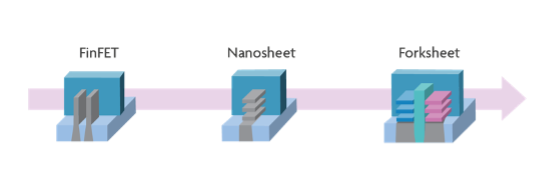

2nm及之后的晶體管結構

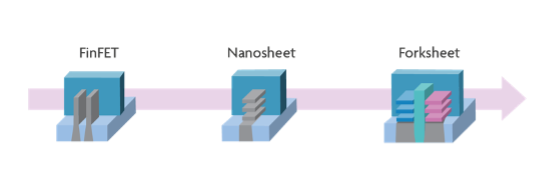

分叉片結構 / IMEC

至于2nm及之后的晶體管結構,比利時微電子研究中心(IMEC)提出了一種新的替代結構,名為分叉片(Forksheet)。該結構中,這些納米片由分叉式的柵極結構來控制,這種結構在柵極圖案化之前,為pMOS和nMOS之間引入了一個絕緣強,將p柵極溝道和n柵極溝道隔絕開來,提供了比FinFET和納米片都要窄的np間距。由此,分叉片可以提供更好的面積和性能擴展能力,并將單元高度從5T減小至4.3T,也實現了更低的寄生電容。

FinFET、納米片、CFET單元高度對比 / IMEC

為了挺進1nm這一制程,單元高度的要求也減小至了3T,但由于布通率的限制,即便是分叉片也無法滿足這一條件。因此,IMEC又推出了名為CFET的技術,一種互補的FET。CFET的概念就是將nFET疊在pFET上,從而提供了更多內部單元布線的自由,并減小了單元面積。在IMEC的初步評估中,運用CFET技術的4T FinFET在功耗和性能的表現上,可以打平甚至超過5T的標準FinFET,而且占用面積還要小25%。至于運用了CFET的納米片晶體管,不僅邏輯單元高度可以做到3T,還能提供額外的性能提升。

結語

就像平面晶體管自然演進至FinFET一樣,FinFET也將讓位給GAAFET。CMOS器件在結構上演化的過程,也是半導體不斷挑戰摩爾定律的過程。除此之外,其實也有不少公司正在探索CMOS之外的晶體管方案,試圖消除CMOS本身的一些缺點,比如英國公司Search For The Next推出的Bizen。但從現在追求PPA的潮流來看,這些方案還遠遠不能成為市場主流。2022年之后的半導體市場,高NA的EUV光刻機和GAAFET必將成為5nm制程以下的關鍵因素。

目前的工藝水平在深度學習、圖形分析等基礎AI應用上已經可以滿足要求,但在神經形態芯片和量子計算上,仍需要更先進的制程來提供支持。面對這些挑戰,三星、臺積電和英特爾紛紛選擇了GAA技術來突破這一壁障。

GAA何時面世?

晶體管結構的演進 / 三星

三星在2019年就公布了其GAA 技術MBCFET,并發布了初版PDK。GAA結構進一步提到了柵極與溝道之間的接觸面積,并支持垂直堆疊的方式來獲得更強的載流能力,而非像FinFET一樣橫向堆疊鰭片。三星也同時宣布,將在3nm工藝節點引入GAA技術。根據三星給出的PPA數據,先進節點的MBCFET與7nm的FinFET相比,功耗減少50%,性能提升30%,面積減小了50%。

堆疊四層納米帶的RibbonFET / 英特爾

IBM全球首發的2nm芯片上,也用到了納米片GAA技術。今年6月底,三星宣布與新思合作的3nm GAA試產芯片已經成功流片。根據目前的消息來看,預計三星會在2022年推出早期GAA技術的制程3GAE,在2023年推出基于MBCFET的3GAP。英特爾也在近期的Intel Accelerated發布會中宣布,將在其20A工藝節點中引入其GAA技術RibbonFET,預計2024年上半年推出。而臺積電則在今年的技術論壇上宣布,FinFET技術只會用到3nm,2nm將用納米片晶體管來取代現有結構。

然而令許多人不解的是,GAA中通道的命名有納米線、納米片和納米帶,這些究竟是營銷術語不同,還是另有玄機呢?

納米線、納米帶與納米片

其實這些并不是花哨的營銷術語,而是對通道物理特質不同的描述。納米線的寬度和通道厚度基本相近,而納米片則選擇了更大的寬度,納米帶則是一個折中的方案,也可以看做是寬度更小的納米片。那么不同的通道對其性能又有何影響呢?由于2D結構約束所帶來優秀的短溝道特性,納米線在低功率應用上的表現更好。而納米片因為更大有效寬度實現了更大的接觸面積,載流性能要更為優異,適合一些高性能的應用,

納米線與納米片的截面對比 / 三星

雖然通道有所差異,但三星等廠商都不約而同的采用了堆疊通道的方式來繼續增加GAA結構的載流性能。不過FinFET中的鰭并不能無限疊加,GAA中的通道也是如此。這種載流能力的提升速度會隨著源極/漏極外延處的寄生電阻而減慢,不僅如此,柵極電容也會隨著通道數的增加而增大,因此為了保證最小的RC延遲,GAA一般會選擇3或4的通道數。

2nm及之后的晶體管結構

分叉片結構 / IMEC

至于2nm及之后的晶體管結構,比利時微電子研究中心(IMEC)提出了一種新的替代結構,名為分叉片(Forksheet)。該結構中,這些納米片由分叉式的柵極結構來控制,這種結構在柵極圖案化之前,為pMOS和nMOS之間引入了一個絕緣強,將p柵極溝道和n柵極溝道隔絕開來,提供了比FinFET和納米片都要窄的np間距。由此,分叉片可以提供更好的面積和性能擴展能力,并將單元高度從5T減小至4.3T,也實現了更低的寄生電容。

FinFET、納米片、CFET單元高度對比 / IMEC

為了挺進1nm這一制程,單元高度的要求也減小至了3T,但由于布通率的限制,即便是分叉片也無法滿足這一條件。因此,IMEC又推出了名為CFET的技術,一種互補的FET。CFET的概念就是將nFET疊在pFET上,從而提供了更多內部單元布線的自由,并減小了單元面積。在IMEC的初步評估中,運用CFET技術的4T FinFET在功耗和性能的表現上,可以打平甚至超過5T的標準FinFET,而且占用面積還要小25%。至于運用了CFET的納米片晶體管,不僅邏輯單元高度可以做到3T,還能提供額外的性能提升。

結語

就像平面晶體管自然演進至FinFET一樣,FinFET也將讓位給GAAFET。CMOS器件在結構上演化的過程,也是半導體不斷挑戰摩爾定律的過程。除此之外,其實也有不少公司正在探索CMOS之外的晶體管方案,試圖消除CMOS本身的一些缺點,比如英國公司Search For The Next推出的Bizen。但從現在追求PPA的潮流來看,這些方案還遠遠不能成為市場主流。2022年之后的半導體市場,高NA的EUV光刻機和GAAFET必將成為5nm制程以下的關鍵因素。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

三星電子

+關注

關注

34文章

15894瀏覽量

183116 -

臺積電

+關注

關注

44文章

5803瀏覽量

176330 -

intel

+關注

關注

19文章

3508瀏覽量

191288 -

晶體管

+關注

關注

78文章

10396瀏覽量

147762 -

FinFET

+關注

關注

12文章

260瀏覽量

92259

發布評論請先 登錄

相關推薦

熱點推薦

1600TOPS!美國新勢力車企自研5nm芯片,轉用激光雷達硬剛特斯拉

的2025 AI Day上,也首次公布了自研自動駕駛大模型,以及自研的5nm定制芯片,同時還明確了激光雷達是其下一代自動駕駛系統的核心傳感器之一。 ? 5nm芯片、高速互連、全新神經網

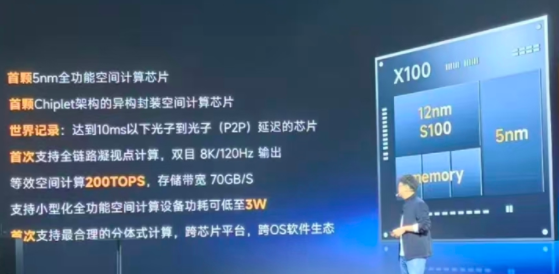

國內首顆5nm MR芯片問世: Chiplet架構、9ms P2P延遲打破紀錄

)正式發布三款自主研發的空間計算芯片——極智G-X100、極眸G-VX100與極顏G-EB100。 ? 其中,旗艦產品極智G-X100作為中國首顆5nm制程全功能空間計算MR芯片,填補了國產高端空間計算

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

最近扒了扒國產芯片的進展,發現中芯國際(官網鏈接:https://www.smics.com)的 14nm FinFET 制程已經不是 “實驗室技術” 了 —— 從消費電子的中端處理器,到汽車電子

發表于 11-25 21:03

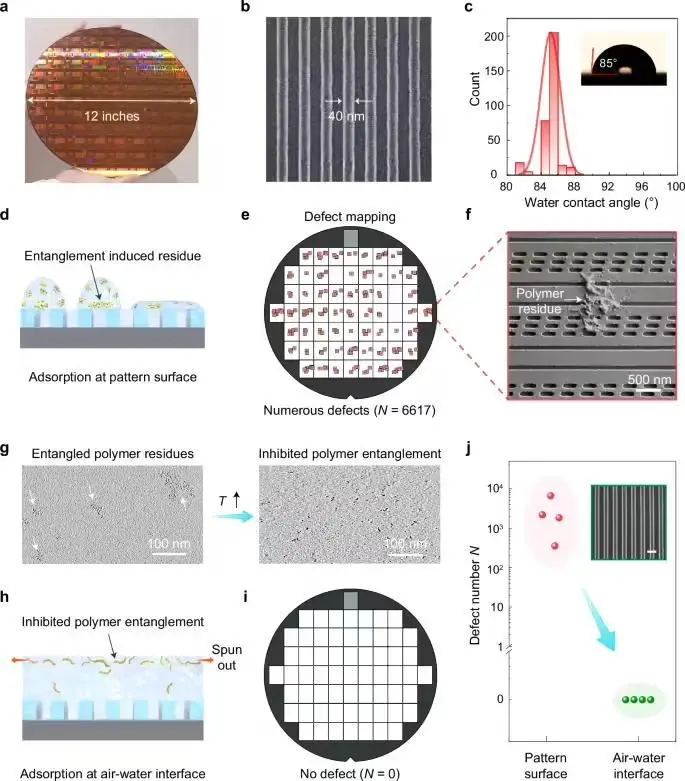

國產光刻膠重磅突破:攻克5nm芯片制造關鍵難題

分布與纏結行為,成功研發出可顯著減少光刻缺陷的產業化方案。相關研究成果已刊發于國際頂級期刊《自然·通訊》,標志著我國在光刻膠關鍵材料領域取得實質性突破。 ? 此次成果對國產芯片制造而言具有里程碑式意義:團隊利用

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

%。至少將GAA納米片提升幾個工藝節點。

2、晶背供電技術

3、EUV光刻機與其他競爭技術

光刻技術是制造3nm、5nm等工藝節點的高端半導體芯片的關鍵技術。是將設計好的

發表于 09-15 14:50

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

。

FinFET是在22nm之后的工藝中使用,而GAA納米片將會在3nm及下一代工藝中使用。

在叉形片中,先前獨立的兩個晶體管NFET和PFET被

發表于 09-06 10:37

全球首款2nm芯片被曝準備量產 三星Exynos 2600

據外媒韓國媒體 ETNews 在9 月 2 日發文報道稱全球首款2nm芯片被曝準備量產;三星公司已確認 Exynos 2600 將成為全球首款采用 2nm 工藝的移動 SoC

今日看點丨蔚來自研全球首顆車規5nm芯片!;沃爾沃中國區啟動裁員計劃

1. 蔚來自研全球首顆車規5nm 芯片!將對全行業開放 ? 據了解,李斌在直播中介紹了蔚來自研神璣NX9031芯片,他表示:“這是全球首顆車規5nm的智駕

發表于 07-08 10:50

?2143次閱讀

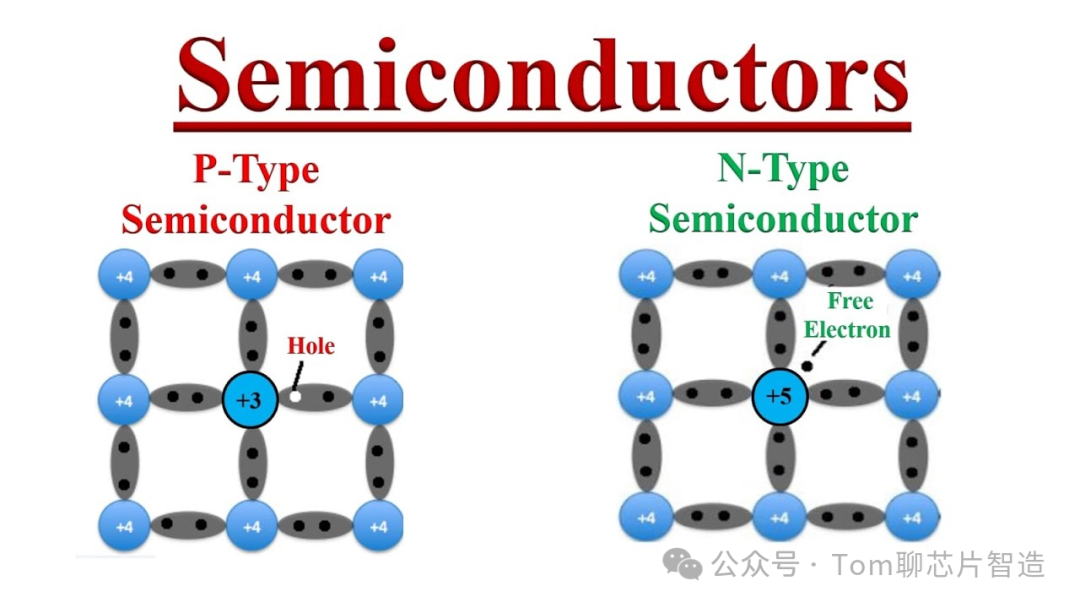

體硅FinFET和SOI FinFET的差異

在半導體制造領域,晶體管結構的選擇如同建筑中的地基設計,直接決定了芯片的性能上限與能效邊界。當制程節點推進到22nm以下時,傳統平面晶體管已無法滿足需求,鰭式場效應晶體管(FinFET

下一代高速芯片晶體管解制造問題解決了!

在半導體工藝演進到2nm,1nm甚至0.7nm等節點以后,晶體管結構該如何演進?2017年,imec推出了叉片晶體管(forksheet),作為環柵(GAA)晶體管的自然延伸。不過,產

發表于 06-20 10:40

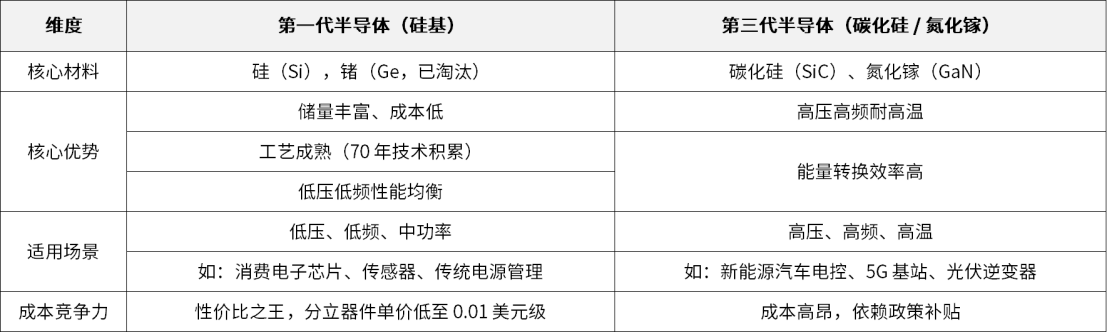

第一代半導體被淘汰了嗎

在半導體產業的百年發展歷程中,“第一代半導體是否被淘汰”的爭議從未停歇。從早期的鍺晶體管到如今的硅基芯片,以硅為代表的第一代半導體材料,始終以不可替代的產業基石角色,支撐著全球95%以上的電子設備

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

我們很高興能在此宣布,Cadence 基于 UCIe 標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現首次流片成功。這一里程碑彰顯了我們持續提供高性能車規級 IP 解決方案?的承諾,可滿足新一代汽車電子和高性能計算應用的嚴格要求。

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片怎樣制造

玻璃板;不透光材料是鉻金屬薄膜,被電鍍在基板上,該薄膜上制作了電路版圖上某一層的幾何圖形。光掩膜版上有鉻金屬薄膜的地方不透光,無鉻金屬薄膜的地方則可以很好地透光。下圖為光掩膜版作為芯片設計與芯

發表于 04-02 15:59

被淘汰的FinFET,5nm之后的芯片該如何制造?

被淘汰的FinFET,5nm之后的芯片該如何制造?

評論