1.1早期的PROM技術實現

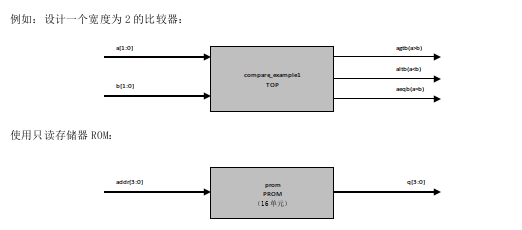

在上世紀60年代以后,小規模集成電路出現,需要實現一個組合邏輯的方法,是一種基于PROM(Programable ROM Based)的技術,其原理是將組合電路的真值表寫入ROM中,用PROM設備實現定制邏輯的真值表,等效于實現定制邏輯。

這里控制信號從略。

首先,將比較器的真值表填寫:

| 索引號 | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

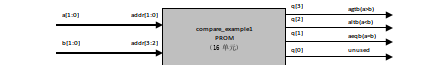

將真值表寫入PROM中,使用PROM設備實現比較器:

等效的實現定制邏輯。

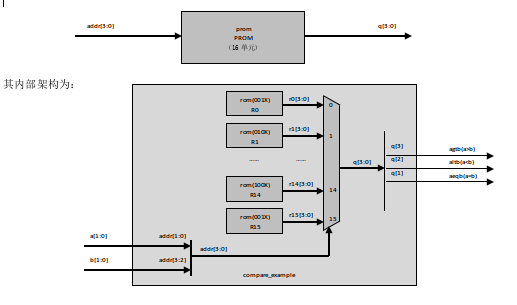

為了進一步了解PROM技術的本質,需要知道ROM設備的架構和原理:

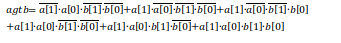

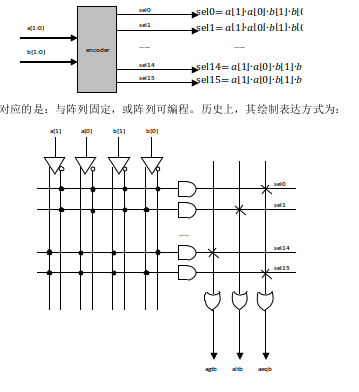

1.2基于PROM技術的SOP(積之和最小項)

數字電路中,將真值表用邏輯門實現的常用方法為SOP(Sum Of Products):

| 索引號 | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

PROM設備中,多路器的選擇信號對應地址的譯碼邏輯

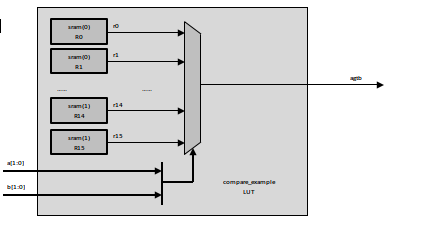

1.3基于查找表技術的定制邏輯

上世紀80年代,CPLD的出現,以及之后的FPGA,為了解決輸入端和存儲單元的2的n次方問題,出現了查找表LUT技術。查找表LUT其原理同樣是用固定的(硬核)多路器,基于SRAM技術,實現定制邏輯的真值表,從而等效的實現定制邏輯。其中一個重要的變化,是將真值表項寫入SRAM(靜態存儲器)中,而不是用反溶絲技術(OTP),從而實現在線編程(沿用至今)。同樣用上面的二輸入比較器為例:

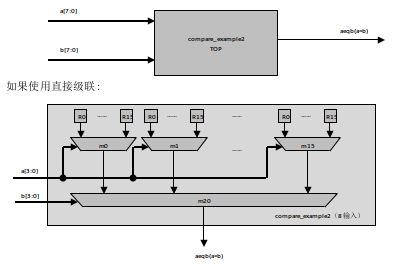

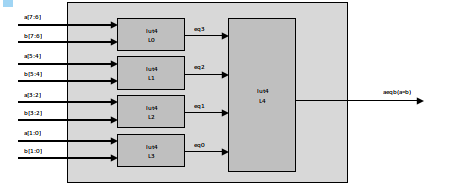

以上例子中,所需要的存儲器單元仍然是16個單元,為2的4次方。為了清楚LUT的減輸入法過程,我們將輸入端增加到16(與或陣列,需要65536單元):

這里使用的存儲器為:16*16=65536。并沒有解決存儲器數量增加的問題。但使用四輸入LUT的實際架構(含減輸入法)為:

這里,僅僅使用了5*16=80個存儲器單元。

1.4在線編程技術

CPLD出現之前,PLD設備大多采用反熔絲技術(Anti-Fuse),交叉編程位置在編程前為高阻抗,編程后為很低的阻抗,為導通態。反熔絲技術為一次性編程(OTP),實際使用并不方便,但其好處是便于保護知識產權。在LUT技術出現以后,設計者的定制邏輯真值表和整個設計的網表(含路由),是寫入靜態存儲器SRAM中,具有速度快,支持在線編程(可反復擦除),但其缺點是揮發性(掉電即失),FPGA每次上電以后,需要重新裝入(有一個比較復雜的配置過程)。

責任編輯:haq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636303 -

存儲器

+關注

關注

39文章

7739瀏覽量

171672 -

硬件

+關注

關注

11文章

3595瀏覽量

69011

原文標題:FPGA學習——FPGA的硬件架構和工作原理

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

基于DSP與FPGA異構架構的高性能伺服控制系統設計

嵌入式和FPGA的區別

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

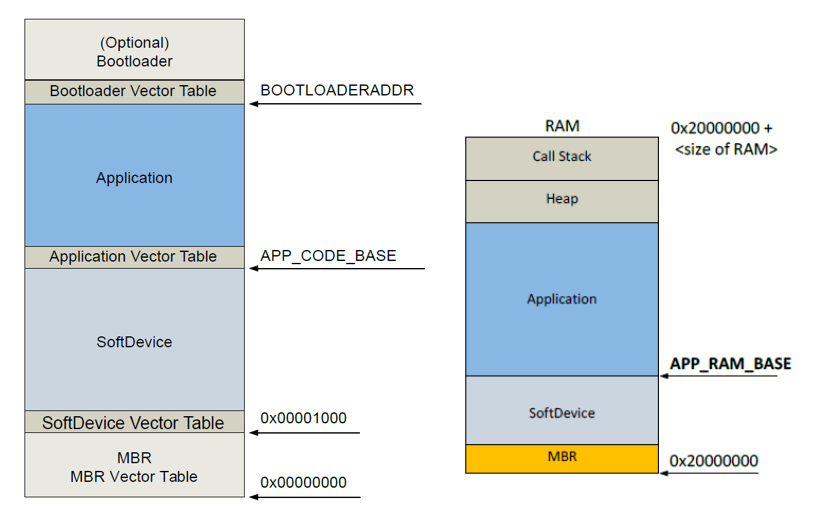

nRF5 SDK軟件架構及softdevice工作原理

異構計算解決方案(兼容不同硬件架構)

GPIO配置的工作原理是什么?

云電競服務器 工作原理

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

FPGA的硬件架構和工作原理

FPGA的硬件架構和工作原理

評論