仿真是我們在驗證邏輯功能的常用手段。通過仿真,我們可以提早發現一些隱含的邏輯Bug。仿真一般分為功能仿真和時序仿真,有的時候也稱作前仿真和后仿真。這兩者的主要區別是在功能仿真里暫時忽略了邏輯延時和布局布線延時,仿真的模型相對簡單,仿真的運行速度更快。

可以用來驗證功能的正確性。時序仿真通過反標的方式將加入延時信息,這樣仿真的結果更接近實際芯片的工作情況。但正因為如此,時序仿真的模型更為復雜,需要計算的信息更多,運行的時間更長。一般情況下,我們首先通過邏輯仿真驗證功能,然后再運行時序仿真驗證時序的正確性。

當然現在也有一些做法是在做功能仿真的時候,人為的設定一些延時,雖然不能百分之百的擬合實際的芯片運行情況,但可以覆蓋大多數的應用場景。帶來的好處是仿真的運行比時序仿真要快很多。

各個EDA公司都有自己的仿真工具,針對FPGA/CPLD來說,用的比較多的是Modelsim和Aldec。無論用哪個仿真工具,有一個細節經常會被初學者會忽略。在設計好testbench后,編譯都沒有問題,但在開始仿真的時候,軟件會報類似這樣的錯誤:

Fatal Error: ELAB2_0036 Unresolved hierarchical reference to“PUR_INST.PURNET” from module“tb_cdr_tb.UUT.top_cdr_u.receive_top_u.serial_data_in.FF_3” (modulenot found)。

Fatal Error: ELAB2_0036 Unresolved hierarchical reference to“GSR_INST.GSRNET” from module “tb_cdr_tb.UUT.top_cdr_u.receive_top_u.serial_data_in.FF_3”(module not found)。

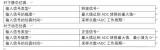

這是因為在芯片工作的時候,內部有PUR(Power Up Reset)和GSR(Global Set/Reset)模塊產生上電復位信號和接入全局復位/置位信號。這個信號在做綜合的時候是自動生成并加入的設計中的,但在仿真的時候編譯并不會加入這兩個模塊。所以如果要做仿真,一定要在你的testbench中加入這樣一段描述:

PUR PUR_INST(.PUR(1‘b1));

GSRGSR_INST(.GSR(1’b1));

本站資訊文章系編輯轉載,轉載目的在于傳遞更多信息,并不代表本站贊同其觀點和對其真實性負責。如涉及作品內容、版權和其它問題,請在30日內與本站聯系,我們將在第一時間刪除內容!

[聲明]本站文章版權歸原作者所有 內容為作者個人觀點 本站只提供參考并不構成任何投資及應用建議。

本站擁有對此聲明的最終解釋權。

編輯;jq

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636247 -

芯片

+關注

關注

463文章

54007瀏覽量

465952 -

cpld

+關注

關注

32文章

1259瀏覽量

173889 -

仿真

+關注

關注

54文章

4482瀏覽量

138251

發布評論請先 登錄

高速PCB打樣必知:細節決定成敗,這些點你不能忽視!

【產品介紹】Modelsim:HDL語言仿真軟件

各位大佬幫忙看一下,下面的assertion有啥問題?為什么用verdi吃文件的時候會報錯誤?

芯來e203移植開發分享(二)——仿真文件簡述與itcm固化程序

rt-studio支持仿真的時候變量實時刷新嗎?

rt-thread studio仿真的時候控制臺不停打印亂碼,導致軟件卡死怎么解決?

自動駕駛中常提的硬件在環是個啥?

PCB仿真結果天下無敵,板廠加工讓你一敗涂地

示波器最主要的作用

使用STM32CubeMX進行配置USB的時候,有哪些小的需要注意的細節?

開關電源仿真

使用LTspice仿真一個LC電路,頻域分析和時域分析結果不一致

對齊熱測量與仿真

仿真的時候最主要的細節是啥?

仿真的時候最主要的細節是啥?

評論