本文通過(guò)以高速AD9361芯片為例進(jìn)行數(shù)據(jù)接口邏輯代碼的編寫,利用SelectIO IP快速高效完成芯片驅(qū)動(dòng)的生成。

2 AD93612.1 芯片簡(jiǎn)介

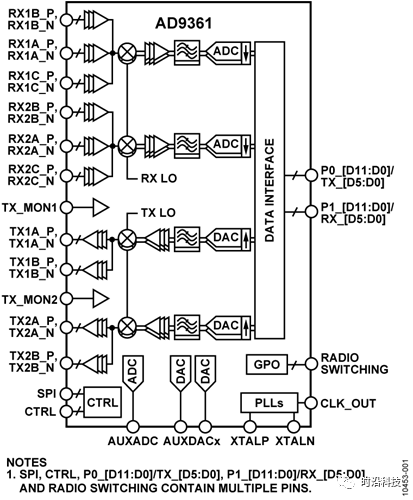

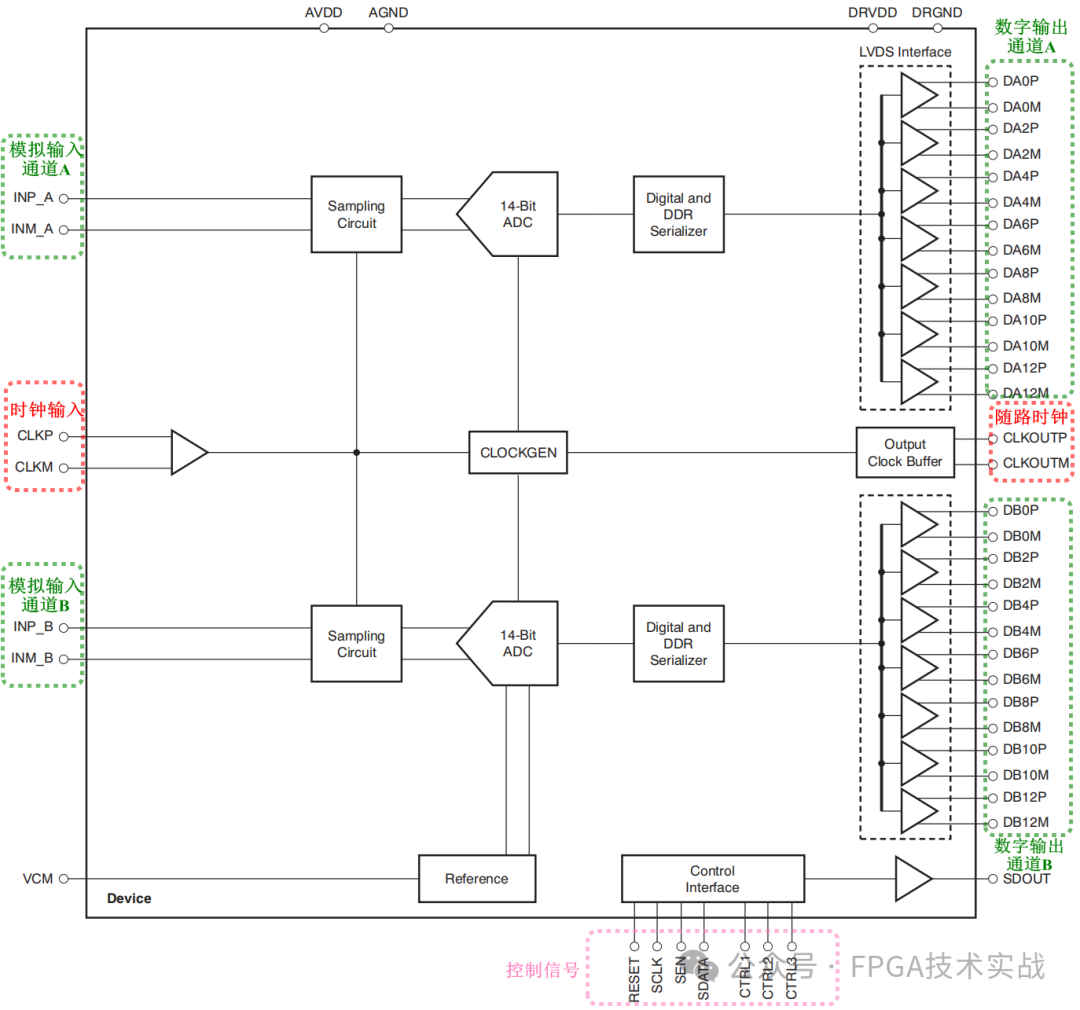

AD9361是一款面向3G和4G基站應(yīng)用的高性能、高集成度的射頻(RF)Agile Transceiver捷變收發(fā)器。該器件的可編程性和寬帶能力使其成為多種收發(fā)器應(yīng)用的理想選擇。該器件集RF前端與靈活的混合信號(hào)基帶部分為一體,集成頻率合成器,為處理器提供可配置數(shù)字接口,從而簡(jiǎn)化設(shè)計(jì)導(dǎo)入。

AD9361接收器LO工作頻率范圍為70 MHz至6.0 GHz,發(fā)射器LO工作頻率范圍為47 MHz至6.0 GHz,涵蓋大部分特許執(zhí)照和免執(zhí)照頻段,支持的通道帶寬范圍為200 kHz以下至56 MHz,整體結(jié)構(gòu)圖如圖 1 AD9361整體結(jié)構(gòu)圖所示。

圖 1 AD9361整體結(jié)構(gòu)圖

? 集成12位DAC和ADC的RF 2 × 2收發(fā)器

? TX頻段:47 MHz至6.0 GHz

? RX頻段:70 MHz至6.0 GHz

? 支持TDD和FDD操作

? 可調(diào)諧通道帶寬:《200 kHz至56 MHz

? 雙通道接收器:6路差分或12路單端輸入

? 出色的接收器靈敏度,噪聲系數(shù)為2 dB (800 MHz LO)

? RX增益控制

o 實(shí)時(shí)監(jiān)控和控制信號(hào)用于手動(dòng)增益

o 獨(dú)立的自動(dòng)增益控制

? 雙發(fā)射器:4路差分輸出

? 高線性度寬帶發(fā)射器

o TX EVM:≤?40 dB

o TX噪聲:≤?157 dBm/Hz本底噪聲

o TX監(jiān)控器:動(dòng)態(tài)范圍≥66 dB,精度=1 dB

? 集成式小數(shù)N分頻頻率合成器

? 2.4 Hz最大本振(LO)步長(zhǎng)

? 多器件同步

? CMOS/LVDS數(shù)字接口

2.2 參數(shù)配置

用戶可以根據(jù)自己的需求將數(shù)據(jù)接口通過(guò)SPI配置成LVDS或CMOS接口,也可以還可以選擇FDD或TDD工作方式,以及數(shù)據(jù)速率可以選擇SDR或DDR。只需要通過(guò)配置軟件設(shè)置即可,如圖 2 AD9361數(shù)據(jù)接口配置參數(shù)所示,詳細(xì)的配置教程見AD936x Evaluation Software 詳細(xì)配置。

在進(jìn)行數(shù)據(jù)驗(yàn)證時(shí),也可以使用測(cè)試模式,對(duì)收發(fā)數(shù)據(jù)進(jìn)行驗(yàn)證以保證系統(tǒng)的正確性。另外,還可以對(duì)輸入時(shí)鐘進(jìn)行延時(shí)調(diào)節(jié)或者通過(guò)SelectIO的delay、delayctrl功能對(duì)時(shí)鐘信號(hào)進(jìn)行微調(diào),以滿足時(shí)序要求。

芯片數(shù)據(jù)時(shí)鐘與數(shù)據(jù)之間的時(shí)序可靠性也可以通過(guò)芯片內(nèi)部的延時(shí)寄存器0x006、0x007進(jìn)行條件,以此達(dá)到要求,具體的SPI配置寄存器時(shí)序如圖 3 AD9361 寄存器配置接口SPI時(shí)序所示。此方面不是本文重點(diǎn),不做展開,更多內(nèi)容參考官方data sheet。

本小節(jié)使用的數(shù)據(jù)接口參數(shù):LVDS、FDD、DDR,對(duì)應(yīng)的時(shí)序邏輯也是根據(jù)該參數(shù)進(jìn)行設(shè)計(jì)。

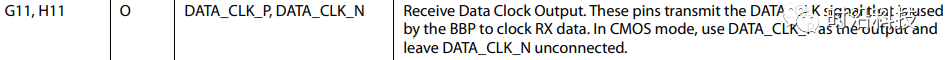

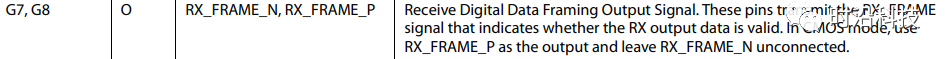

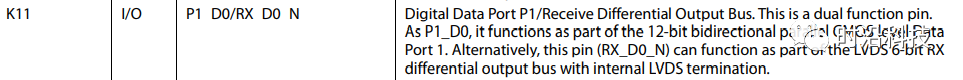

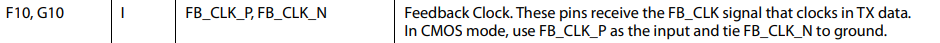

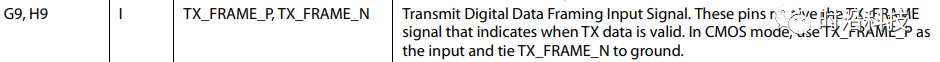

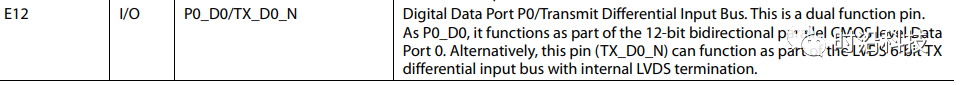

2.3 引腳

RX數(shù)據(jù)時(shí)序接口如下:

TX數(shù)據(jù)時(shí)序接口如下:

2.4 接口時(shí)序

以下使用的數(shù)據(jù)接口參數(shù):LVDS、FDD、DDR,根據(jù)不同的通道數(shù)可以得到不同的數(shù)據(jù)時(shí)序,用戶在解析數(shù)據(jù)時(shí)只要按照對(duì)應(yīng)的結(jié)構(gòu)進(jìn)行拼接即可。

3 參考代碼3.1 SelectIO配置

根據(jù)以上對(duì)AD9361的了解,就可以輕松的配置SelectIO IP的GUI界面了。芯片既包括發(fā)射模塊TX又包括接收模塊RX,所以IO類型選擇chip to chip。

根據(jù)上述參數(shù)配置部分,自然就選擇DDR。數(shù)據(jù)接口包括時(shí)鐘CLK、Frame對(duì)齊信號(hào)與差分?jǐn)?shù)據(jù)端Data[05:0],要同時(shí)對(duì)Frame與Data信號(hào)進(jìn)行時(shí)序解析,所以端口寬度設(shè)置為7.

由于芯片內(nèi)部寄存器0x006、0x007可以確保時(shí)鐘與數(shù)據(jù)滿足時(shí)序要求,所以不需要延時(shí)模塊,以節(jié)約FPGA邏輯資源。

3.2 數(shù)據(jù)解析

//-------------------------------------------------------------------

// 用于將接收時(shí)鐘與數(shù)據(jù)進(jìn)行單端與差分的變換

//-------------------------------------------------------------------

selectio_ip u_selectio_ip (

// From the system into the device

.DATA_IN_FROM_PINS_P (ad_rx_data_in_p),

//從AD接收端接收到的單端數(shù)據(jù)與標(biāo)志

.DATA_IN_FROM_PINS_N (ad_rx_data_in_n),

//從AD接收端接收到的單端數(shù)據(jù)與標(biāo)志

.DATA_IN_TO_DEVICE (ad_rx_data),

//將AD接收端接收到的數(shù)據(jù)與標(biāo)志轉(zhuǎn)換為單端數(shù)據(jù)

// From the device out to the system

.DATA_OUT_FROM_DEVICE (ad_tx_data),

//將要發(fā)送的DA數(shù)據(jù)與標(biāo)志轉(zhuǎn)換為單端數(shù)據(jù)

.DATA_OUT_TO_PINS_P (ad_tx_data_out_p),

//發(fā)送端的單端DA數(shù)據(jù)與標(biāo)志

.DATA_OUT_TO_PINS_N (ad_tx_data_out_n),

//發(fā)送端的單端DA數(shù)據(jù)與標(biāo)志

.CLK_TO_PINS_P (ad_fb_clk_p),

//將AD接收端的輸入時(shí)鐘用于發(fā)射時(shí)鐘

.CLK_TO_PINS_N (ad_fb_clk_n),

//將AD接收端的輸入時(shí)鐘用于發(fā)射時(shí)鐘

.CLK_IN_P (ad_data_clk_p),

//AD接收端的單端輸入時(shí)鐘

.CLK_IN_N (ad_data_clk_n),

//AD接收端的單端輸入時(shí)鐘

.CLK_OUT (ad9361_data_clk),

//將AD接收端的差分輸入時(shí)鐘轉(zhuǎn)變?yōu)閱味藭r(shí)鐘

.CLK_RESET (reset),

//用于AD輸入時(shí)鐘的復(fù)位,高有效

.IO_RESET (reset)

//用于單端、差分變換的復(fù)位,高有效

);

//-------------------------------------------------------------------

//發(fā)送數(shù)據(jù)的生成

//-------------------------------------------------------------------

assign ad_tx0_msb_q=ad_tx0_data[23:18];

assign ad_tx0_lsb_q=ad_tx0_data[17:12];

assign ad_tx0_msb_i=ad_tx0_data[11:06];

assign ad_tx0_lsb_i=ad_tx0_data[05:00];

assign ad_tx1_msb_q=ad_tx1_data[23:18];

assign ad_tx1_lsb_q=ad_tx1_data[17:12];

assign ad_tx1_msb_i=ad_tx1_data[11:06];

assign ad_tx1_lsb_i=ad_tx1_data[05:00];

reg [13:0] ad_tx_data;

//-------------------------------------------------------------------

//選擇要發(fā)送的I與Q數(shù)據(jù)

//-------------------------------------------------------------------

always @(posedge ad9361_data_clk or posedge reset) begin

if(reset)

ad_tx_data《=0;

else if((ad_tx_frame_reg==0)&&(ad_tx_frame==1))

ad_tx_data《={ad_tx_frame,ad_tx0_msb_q,ad_tx_frame,ad_tx0_msb_i};

else if((ad_tx_frame_reg==1)&&(ad_tx_frame==1))

ad_tx_data《={ad_tx_frame,ad_tx0_lsb_q,ad_tx_frame,ad_tx0_lsb_i};

else if((ad_tx_frame_reg==1)&&(ad_tx_frame==0))

ad_tx_data《={ad_tx_frame,ad_tx1_msb_q,ad_tx_frame,ad_tx1_msb_i};

else if((ad_tx_frame_reg==0)&&(ad_tx_frame==0))

ad_tx_data《={ad_tx_frame,ad_tx1_lsb_q,ad_tx_frame,ad_tx1_lsb_i};

end

//-------------------------------------------------------------------

//選擇接收的I與Q數(shù)據(jù)

//-------------------------------------------------------------------

always @(posedge ad9361_data_clk or posedge reset) begin

if(reset) begin

ad_rx0_msb_i《=0;

ad_rx0_msb_q《=0;

ad_rx0_lsb_i《=0;

ad_rx0_lsb_q《=0;

ad_rx1_msb_i《=0;

ad_rx1_msb_q《=0;

ad_rx1_lsb_i《=0;

ad_rx1_lsb_q《=0;

end

else if((ad_rx_frame_reg==0)&&(ad_rx_frame==1)) begin

ad_rx0_msb_i《=ad_rx_data[05:0];

ad_rx0_msb_q《=ad_rx_data[12:7];

end

else if((ad_rx_frame_reg==1)&&(ad_rx_frame==1)) begin

ad_rx0_lsb_i《=ad_rx_data[05:0];

ad_rx0_lsb_q《=ad_rx_data[12:7];

end

else if((ad_rx_frame_reg==1)&&(ad_rx_frame==0)) begin

ad_rx1_msb_i《=ad_rx_data[05:0];

ad_rx1_msb_q《=ad_rx_data[12:7];

end

else if((ad_rx_frame_reg==0)&&(ad_rx_frame==0)) begin

ad_rx1_lsb_i《=ad_rx_data[05:0];

ad_rx1_lsb_q《=ad_rx_data[12:7];

end

end

wire [23:0] ad_rx0_fifo_data;

wire [23:0] ad_rx1_fifo_data;

assign ad_rx0_fifo_data={ad_rx0_msb_q,ad_rx0_lsb_q,ad_rx0_msb_i,ad_rx0_lsb_i};

assign ad_rx1_fifo_data={ad_rx1_msb_q,ad_rx1_lsb_q,ad_rx1_msb_i,ad_rx1_lsb_i};

編輯:jq

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465909 -

發(fā)射器

+關(guān)注

關(guān)注

7文章

919瀏覽量

55328

原文標(biāo)題:FPGA實(shí)現(xiàn)AD9361數(shù)據(jù)接口邏輯

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

面向高速、遠(yuǎn)距離傳輸應(yīng)用的機(jī)器視覺數(shù)據(jù)接口(以Vieworks為例)

RDMA設(shè)計(jì)5:RoCE V2 IP架構(gòu)

NICE協(xié)處理器接口信號(hào)解讀--以demo為例

通用接口芯片國(guó)產(chǎn)替代進(jìn)程:以ASM1042為例看自主可控的現(xiàn)實(shí)意義

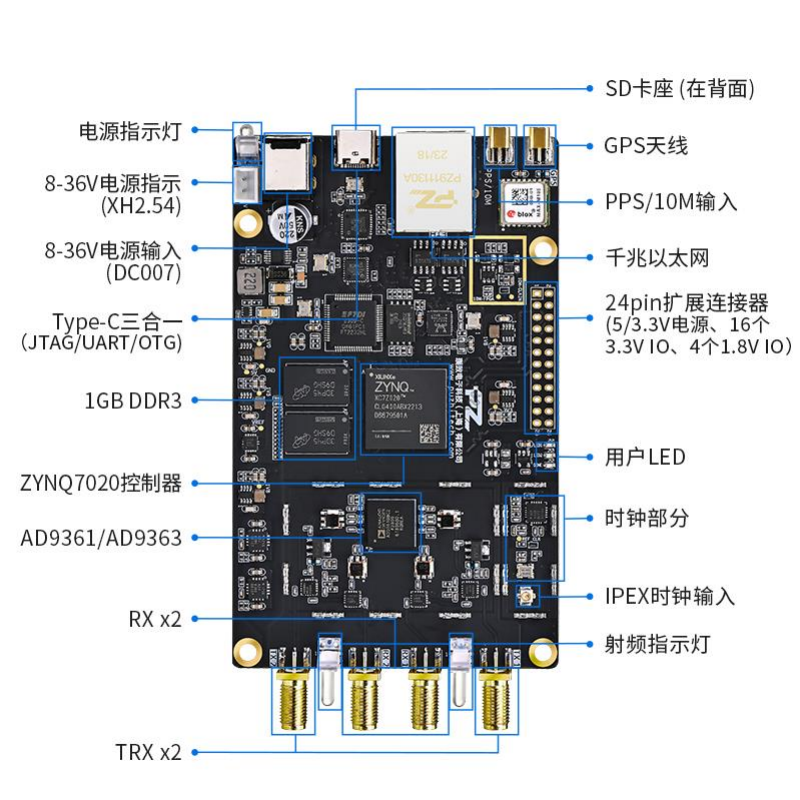

軟件無(wú)線電-AD9361 璞致 PZSDR 軟件無(wú)線電系列板卡之PZ-FL9361(FMCOMMS3)使用說(shuō)明

嵌入式接口通識(shí)知識(shí)之MIPI接口

PZSDR 軟件無(wú)線電 開發(fā)板系列板卡之P201Pro P203Pro 硬件說(shuō)明—AD9361 AD9363

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計(jì)18:UVM驗(yàn)證平臺(tái)

【PZSDR AD9361】——璞致PZ-FL9361 軟件無(wú)線電模塊:工業(yè)級(jí)射頻解決方案的技術(shù)標(biāo)桿

I2S 串行數(shù)據(jù)輸入顯示延遲串行數(shù)據(jù)輸出?

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設(shè)計(jì)

以高速AD9361芯片為例進(jìn)行數(shù)據(jù)接口邏輯代碼的編寫

以高速AD9361芯片為例進(jìn)行數(shù)據(jù)接口邏輯代碼的編寫

評(píng)論