數據時代對計算提出新需求

在過去的一年半中,全球經歷了新冠疫情的肆虐。雖然已經有多種疫苗開始實施接種,但是新冠疫情在未來相當長的一段時間里對我們的生活依舊持續帶來影響。我們很多人已經習慣了通過電子設備在家辦公、上網課、開會甚至舉辦線上大型會議。2020年,全球市值最大的10家公司中前8家公司都是基于互聯網和大數據開展業務,另外值得關注的是半導體制造商臺積電(TSMC)位列第9位。21世紀將會是數據的世紀,數據已經成為類似石油的新型資源。大數據、圖像分析、機器學習已經非常普遍,從數據中心、移動設備到物聯網設備都會成為數據處理的主要節點。高性能計算機前所未有地成為我們生活中的必需品,并且極大推動了對高算力計算芯片的龐大需求。

傳統集成技術下的摩爾定律已經不再有效

在1965年Gordon Moore提出摩爾定律到今天的近56年中,摩爾定律的效率已經逐步衰退到接近失效。Alphabet的董事長John Hennessy于2018年在美國國防高級研究計劃局電子復興計劃會議(DARPA ERI)上的演講中展示了一張圖片,是過去40年來計算機性能的增長趨勢。可以看到,在1978年到1986年,計算機性能的平均每年長率是25%,隨后的1986年到2003年的17年中,年平均增長率增加到52%。接下來的10年,計算機性能的年平均增長率開始下降到23%,隨后的幾年,進一步下降到12%,直到近5年,已經下降到了3.5%。

近40年來,計算機性能增長的趨勢

John Shalf在2019國際超級計算機會議上的演講中展示了一張圖片,在過去近50年中,計算機系統在晶體管數量、單線程性能、時鐘頻率、功耗以及內核數量這5個指標上的發展趨勢。可以看到,在2021年,這些指標都有可能趨于飽和。今天,我們正在面臨摩爾定律的終結,需要尋找一種新的路徑繼續提高電子產品的性能。

計算機技術發展趨勢在2021年趨于飽和

國際半導體技術藍圖(ITRS)自從1991年誕生到2016年7月發布了最后的版本,指出半導體體積到2021年將不再縮小。報告認為,半導體廠商將面積縮小、放下更多晶體管的做法在經濟上已經不劃算。此后,半導體廠商將更多關注3D芯片等其他技術增強計算性能。AMD的CEO Lisa Su在2019年的DARPA ERI會議上也展示了隨著工藝節點從45nm逐步過渡到5nm,單位芯片面積的成本增加到了最初的5倍。

摩爾定律的經濟效應遇到瓶頸

異構集成將推動摩爾定律趨勢繼續有效

2015年,ITRS的異構集成(Heterogeneous Integration)研究團隊與電氣電子工程師學會(IEEE)的元器件、封裝、制造技術學會(CPMT)簽署了一份諒解備忘錄,宣告異構集成藍圖(HIR)成立并開始完全代替ITRS。HIR 由IEEE的3個學會(電子封裝學會EPS、電子器件學會EDS、光電學會PS)和半導體設備和材料國際組織(SEMI) 與美國機械工程師學會的電子與光子封裝事業部 (ASME EPPD)共同組成。目的是為了維護把不同工藝制造的元器件集成在一起的先進封裝技術的進步步伐,以便使當今和未來的電子系統得到更增強的功能和操作體驗。

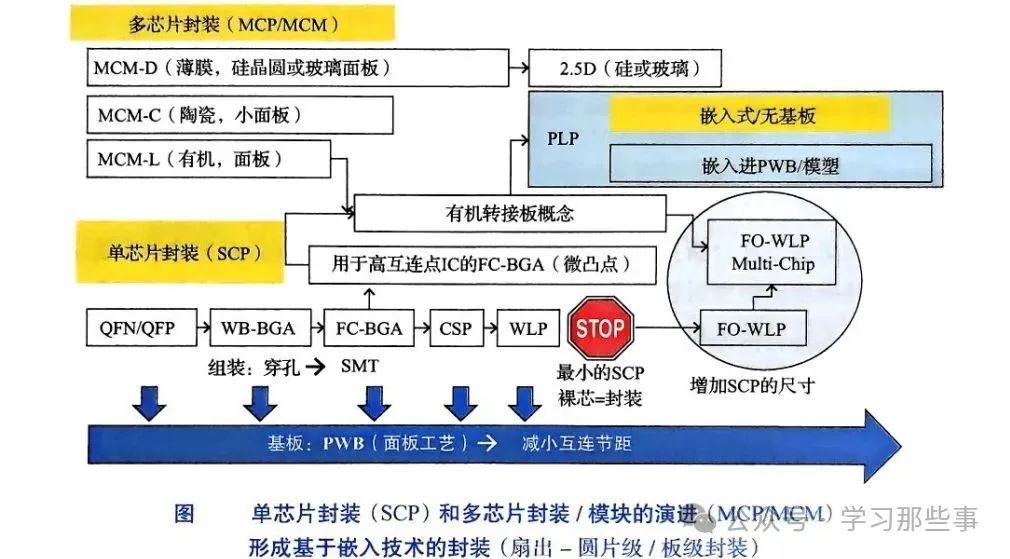

異構集成通過工藝技術的多樣性、功能多樣性和材料的多樣性進行系統級的集成或3D封裝,將進一步推動半導體工業第四波技術浪潮以便維持摩爾定律趨勢繼續有效。技術多樣性需要將不同工藝節點的芯片集成在一起,不同于傳統SoC技術手段去統一追求更先進的工藝節點,對于某些性能優異的工作穩定的IP或稱為小芯片(Chiplet)可以更長時間停留在較早的工藝節點上。對于功能多樣性體現在把數字、模擬、模數混合、光電子、微機械等等不同類別的芯片做集成,這在傳統SoC技術路徑上是很難做到的。材料多樣性是異構集成最重要的特性,不局限于傳統CMOS工藝,采用多種工藝結合的方式,比如采用光學系統的I/O。

異構集成是延長摩爾定律的第4波浪潮

Intel的 Agilex系列FPGA是非常典型的異構集成成功案例,它既包含了傳統FPGA靈活的可編程性,又結合了現代FPGA基于異構架構的敏捷性。通過Intel定義的EMIB總線將不同工藝節點的小芯片連接起來。

AMD的EPYC處理器是另一個異構集成的案例。在第一代EPYC中,處理器由4個14nm工藝的小芯片組合而成。而到第二代EPYC時,處理器由4組共八個7nm小芯片和一個14nm的I/O芯片組合而成。

以下是幾款主流手機處理器芯片的切面圖,可以看到,Apple A12采用了WLP Fan-out工藝封裝集成,而三星 EXYNOS9810和華為Kirin980都是采用了先進PoP工藝封裝集成。

異構集成不僅僅是封裝加工

異構集成對傳統的封裝測試廠商(OSAT)提出了更高要求,無論是從系統設計還是EMI/PI/SI協同優化仿真,熱性能優化和結構優化仿真都與傳統封裝廠的工藝技術有較大區別。未來,承擔異構集成設計的廠商絕不能僅僅是一家封裝代工廠,而是需要能夠提供完整的先進封裝設計與制造解決方案的廠商。在眾多廠商中,ASE、Amkor具備了優秀和完整的整體解決方案。國內廠商中,通富AMD和長電收購的星科金朋也有比較強的整體方案能力。

銳杰微科技在異構集成方面擁有多年積累

銳杰微在芯片封裝設計,電性能仿真、分析、優化,熱性能分析優化,機械應力分析優化方面經過大量的高端系統化芯片產品的項目經驗,構建了一套獨特的方案設計、仿真、優化思路,幫助國內百余家中高端科研、商業客戶完成大量業內首創產品,涵蓋國產CPU、GPU、FPGA、DSP以及ADC、手機處理器、AI、車載控制芯片領域,下面是銳杰微的經典案例中比較突出產品:

CPU+FPGA SiP(網絡處理芯片)

多芯片球陣列網絡處理器芯片,包含DDR3(1600Mbps),PCIE2.0(5Gbps)、XAUI(6.25Gbps)等高速信號,該項在有限的空間內部封裝有大量的高速信號互聯,并且實現互相干擾達標。61mm x61mm的大尺寸封裝同時也對設計和加工帶來極大挑戰

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:61mm x 61mm

Ball數量:3576

基板:10 層有機基板

CPU+FPGA+Flash SiP

該產品同樣屬于大尺寸封裝,50mm x 50mm,高速率、多信號,含 PCIE x 16 3.0,DDR3 x 72,USB 2.0 等高速接口,內部集成多芯片,并且結合Solder Ball 和 Copper Pillar 兩種倒裝工藝形式,基板的設計和表面處理工藝滿足兩種 Bump 加工工藝的設計與加工參數

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:50mm x 50mm

Ball數量:2089

基板:10 層有機基板

DSPSiP(處理芯片)

大規模的HFCBGA 封裝芯片,集高性能、高密度一體化數字處理模塊,高速串并行信號(PCIE 3.0;Serdes 10.125 Gbps;TDP 60W;內部集成 8 顆 4Gb DDR3 4 x 72bit 1600Mbps )和一顆 Flash 外加一顆 DSP 芯片。DDR 芯片原始設計為 WB 工藝,銳杰微對該芯片進行了 RDL 二次設計,使 DDR 芯片改為倒裝工藝,在基板的設計過程中對 DDR 拓樸的排布,封裝一次加工就達到了項目要求。9 顆大功耗的芯片集成在一個封裝內,特別是主芯片電流達到 30A,在如此小的封裝內部很好的滿足了大電流低電壓的電源完整性和散熱問題

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:35mm x 35mm

Ball數量:1024

基板:10 層有機基板

銳杰微同時在先進封裝領域也積累了2.5D高密度和復雜TSV 的設計及應用項目經驗,具備完整的設計、仿真、產品評估能力,下面是一款從設計到仿真(信號完整性、電源完整性、結構應力)、加工工藝、組裝工藝、表面處理工藝到產品的陶封TSV正反雙腔體、FC和WB混合工藝的SiP封裝產品:

CPGA(陶封)SiP

陶瓷正反雙腔體、TSV 2.5D 封裝結構、21 顆裸芯,正面 WB,反面 FC 混合工藝,包含 DDR3 、FPGA 、DSP 、AD 、Flash 及部分高速差分和模擬信號,大型陶瓷封裝,應用在高可靠性領域,封裝采用了先進的 2.5D 工藝,封裝內部集成了紅外光感芯片,DSPFPGA5片DDRAD芯片,集成度高,功能復雜。DDR 難度較大,在有限的空間內及針對陶瓷基板很好的匹配有限的工藝能力同時實現大功耗,高頻率的信號連接

封裝形式:CPGA (Ceramic Pin Grid Array)

封裝尺寸:40mm x 40mm

Ball數量:316

基板:23層陶瓷基板

銳杰微科技是一家高度重視知識產權的科技企業,建有一套完整的知識產權管理體系,不斷激勵創新。在公司發展的過程中,不斷地獲得政府和產業的高度認可。

在美國對華科技打壓的大背景下,異構集成是實現彎道追趕的最佳路徑

1947年,美國貝爾實驗室發明了世界上第一個晶體管。直到1956年,中國才成功制成第一根硅單晶棒。1958年,當時在TI工作的Jack Kilby做出的世界上首個集成電路。1968年,國防科工委決定在永川建立一個專業從事集成電路及相關技術研究的綜合性研究所——“中國人民解放軍一四二四研究所”,這也是我國第一個集成電路專業研究所。1972年6月成功研制出了我國第一塊PMOS型大規模集成電路——120位靜態移位寄存器(集成了1084個元件/片)。中國的集成電路行業,從起步就已經落后美國十幾年。這個行業一直是中國在追趕美國的步伐。

美國對中國在集成電路方面的打壓并不是近幾年才有的事情,對于最先進的工藝技術,很多年前就已經保持著對華封鎖的態勢,這也使得中國在工藝代差上始終落后美國至少2~3代。這種代差對于數字集成電路如CPU的性能影響尤其比較大。在摩爾定律最穩定的那段時間,工藝節點決定了芯片的性能。不過隨著摩爾定律的逐漸退化,近幾年來,用以提升處理器性能的方式已經不僅僅是采用先進工藝制程等,同時代差的影響已經沒有過去那么大了。

隨著多核架構、高吞吐存儲等方式的運用,采用10nm制程的多芯片異構集成方式處理器性能未必會遜色于采用7nm SoC單芯片方式的性能。Intel的Agilex FPGA就是個成功案例。這也給目前中國面臨的巨大國產替代壓力下的集成電路行業提供了一個新思路。通過已有的工藝能力加工出小芯片(chiplet),用異構集成的方式進行性能和功能的擴展集成,同樣可以實現小型化、高性能的芯片方案。而且隨著工藝節點的繼續升級,這種改善比單純依賴提高工藝水平的性價比高很多。

美國Intel成立了一個名為HI3(Heterogeneous Integration Incorporating Intel)的合作標準組織,發展Chiplet生態環境。目前已經有包括Intel、TSMC、GF等多個工藝節點的數十個Chiplet量產。

銳杰微科技也已在幾年前就致力于發展中國自有的chiplet標準,早在2019年就加入了中國軟件定義互連技術與產業創新聯盟(SDI),于2020年加入了中國計算機互連技術聯盟(CCITA)。在異構集成方面,中國完全不必按照美國的路徑追趕。通過建立自己的芯片互聯標準,完全可以在上一波摩爾定律退化失效而第4波浪潮還未起來的時候彎道趕上。在中美科技對抗的大環境下,這樣做也是必要的。

原文標題:展商動態 | 異構集成重新定義封裝在芯片產業鏈中的地位——銳杰微科技集團總裁 劉海川

文章出處:【微信公眾號:ELEXCON深圳國際電子展】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

463文章

54010瀏覽量

466107 -

封裝

+關注

關注

128文章

9249瀏覽量

148628 -

異構集成

+關注

關注

0文章

42瀏覽量

2293

原文標題:展商動態 | 異構集成重新定義封裝在芯片產業鏈中的地位——銳杰微科技集團總裁 劉海川

文章出處:【微信號:ELEXCON深圳國際電子展,微信公眾號:ELEXCON深圳國際電子展】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

3D IC設計中的信號完整性與電源完整性分析

華大九天Argus 3D重塑3D IC全鏈路PV驗證新格局

【2025九峰山論壇】破局摩爾定律:異質異構集成如何撬動新賽道?

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

電力電子中的“摩爾定律”(2)

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應用

AI時代,封裝材料如何助力實現更優的異構集成?

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

異構集成將推動摩爾定律趨勢繼續有效

異構集成將推動摩爾定律趨勢繼續有效

評論