日月光研發(fā)中心副總經(jīng)理洪志斌博士在ICEP 2021線上研討會(huì)上全面解析系統(tǒng)級(jí)封裝SiP如何推動(dòng)新系統(tǒng)集成,特別是嵌入式封裝(Embedded)、倒裝芯片封裝(Flip Chip)以及扇出型封裝(Fan Out)如何以更高密度、更小尺寸和更短周期設(shè)計(jì)流程來(lái)實(shí)現(xiàn)在AIoT、5G、汽車(chē)電子、邊緣運(yùn)算和大數(shù)據(jù)的應(yīng)用。

洪博士表示未來(lái)10年將呈現(xiàn)新的3C趨勢(shì),即收集(Collect)、互連(Connect)及運(yùn)算(Compute),利用傳感器、雷達(dá)等裝置采集信息并通過(guò)5G、WiFi、藍(lán)牙等方式在計(jì)算機(jī)進(jìn)行AI運(yùn)算和智能處理。人類(lèi)對(duì)電子產(chǎn)品的功能需求不斷升級(jí),推動(dòng)芯片和封裝技術(shù)朝功能最優(yōu)化但尺寸微型化方向發(fā)展,嵌入式系統(tǒng)集成封裝(a-EASI)和基板型嵌入式封裝(SESUB)因其技術(shù)特性和解決方案將廣泛應(yīng)用。

—嵌入式系統(tǒng)集成封裝(a-EASI)—

嵌入式系統(tǒng)集成封裝(a-EASI)是結(jié)合引線框架(Leadframe)和基板技術(shù)的封裝技術(shù),適用于所有的集成電源設(shè)備。利用引線框架的底座結(jié)構(gòu)使其具備強(qiáng)大的電流處理能力及散熱能力,是一種低損耗、高熱性能的解決方案,不僅設(shè)計(jì)靈活,可使芯片尺寸縮小50%,功耗降低80%以上,還能保持良好的穩(wěn)定性和可靠性。特別是在汽車(chē)應(yīng)用領(lǐng)域,a-EASI技術(shù)可以為ATV Grade 0級(jí)別汽車(chē)處理多達(dá)2000多個(gè)溫度循環(huán)檢測(cè), 提高汽車(chē)的高可靠性性能。

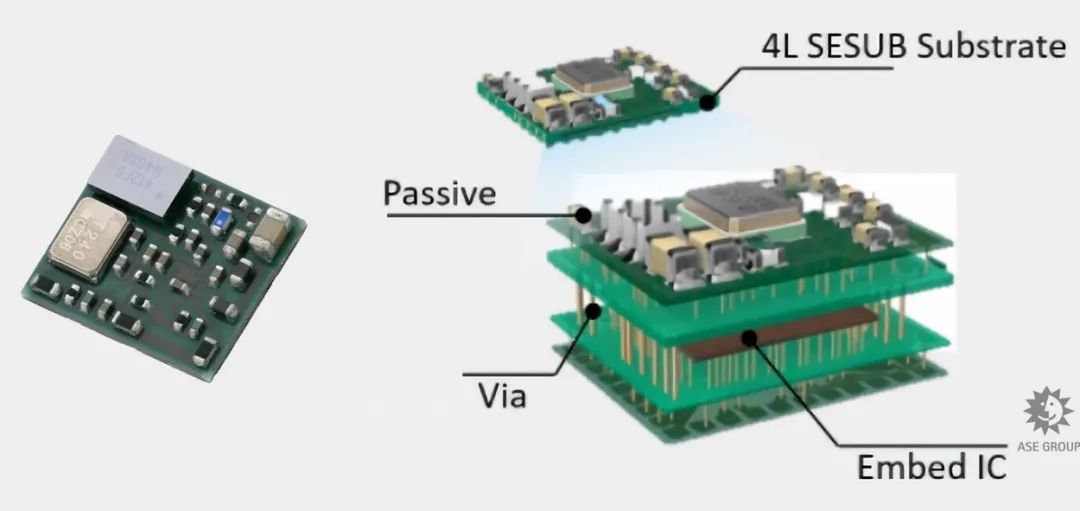

—基板型嵌入式封裝(SESUB)—

基板型嵌入式封裝(SESUB)是將集成電路嵌入層壓基板的技術(shù),嵌入的基板可以安裝各種電子元件,形成高度集成的多功能封裝。SESUB支持功能性電路的微模塊化,例如智能手機(jī)的高性能PMUs以及藍(lán)牙模塊等,同時(shí)通過(guò)減小模塊的嵌入高度和底面積實(shí)現(xiàn)縮小模塊尺寸的功能,可使電源管理單元模塊縮小60%,音頻模塊縮小32%,藍(lán)牙低能量模塊縮小65%及DC/DC變頻器模塊縮小36%等。

日月光的嵌入式技術(shù)被認(rèn)為是實(shí)現(xiàn)更高級(jí)別集成的替代解決方案,提供SMT集成和靈活的布線解決方案以減小PCB尺寸,同時(shí)采用金屬引線框架進(jìn)行模具布局,具有高散熱性和電磁干擾效益。

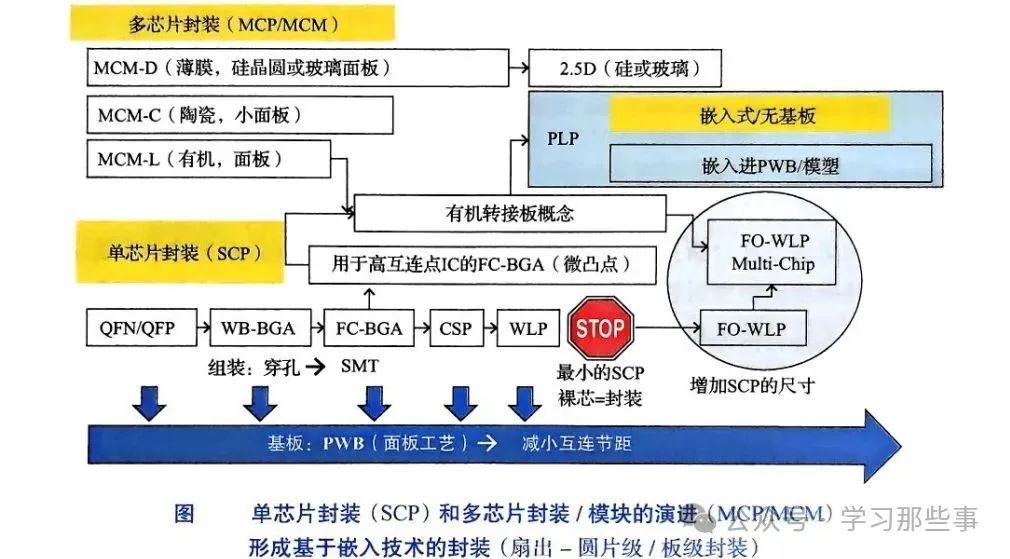

洪博士還舉例說(shuō)明MEMS基于引線框架、BGA封裝、倒裝芯片封裝(Flip Chip)、晶圓級(jí)封裝(Wafer LevelCSP)、扇出型封裝(Fan Out)以及硅通孔(TSV)的系統(tǒng)級(jí)封裝SiP技術(shù)可根據(jù)不同目的做相應(yīng)的調(diào)整。例如可以用引線框架和BGA封裝技術(shù)實(shí)現(xiàn)經(jīng)濟(jì)高效的封裝解決方案,而如果要進(jìn)一步加強(qiáng)壓力控制,可以對(duì)結(jié)構(gòu)進(jìn)行重新計(jì)算,采用不同的基板以及引線鍵合(Wire Bond)技術(shù)予以實(shí)現(xiàn)。

未來(lái)a-EASI 、SESUB、引線框架、BGA封裝、倒裝芯片封裝(Flip Chip)以及晶圓級(jí)TSV技術(shù)等都可以滿(mǎn)足包括5G、AI、智能汽車(chē)以及邊緣計(jì)算等所有應(yīng)用的需求,可根據(jù)要求整合多項(xiàng)封裝技術(shù),從而成功實(shí)現(xiàn)系統(tǒng)級(jí)封裝SiP異質(zhì)整合能力。日月光將持續(xù)強(qiáng)化在先進(jìn)封裝、測(cè)試技術(shù)及基板設(shè)計(jì)等方面的競(jìng)爭(zhēng)力,為客戶(hù)提供嵌入式芯片基板的全方位解決方案。

編輯:jq

-

BGA封裝

+關(guān)注

關(guān)注

4文章

125瀏覽量

19091 -

倒裝芯片

+關(guān)注

關(guān)注

1文章

119瀏覽量

16843 -

SESUB

+關(guān)注

關(guān)注

0文章

2瀏覽量

6535 -

晶圓級(jí)封裝

+關(guān)注

關(guān)注

5文章

46瀏覽量

11801

原文標(biāo)題:全面性系統(tǒng)級(jí)封裝SiP 推動(dòng)新系統(tǒng)集成

文章出處:【微信號(hào):ASE_GROUP,微信公眾號(hào):ASE日月光】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

中科億海微SiP微系統(tǒng):以“重構(gòu)”之力,賦能行業(yè)解決方案國(guó)產(chǎn)集成化之路

Telechips推出系統(tǒng)級(jí)封裝模塊產(chǎn)品

系統(tǒng)級(jí)立體封裝技術(shù)的發(fā)展與應(yīng)用

系統(tǒng)級(jí)封裝技術(shù)解析

EtherCAT轉(zhuǎn)Profinet網(wǎng)關(guān)與匯川伺服系統(tǒng)集成及輪廓模式應(yīng)用解析

基于板級(jí)封裝的異構(gòu)集成詳解

SiP 封裝與錫膏等焊料協(xié)同進(jìn)化之路?

RP2040的工業(yè)級(jí)封裝系統(tǒng)!

系統(tǒng)級(jí)封裝電磁屏蔽技術(shù)介紹

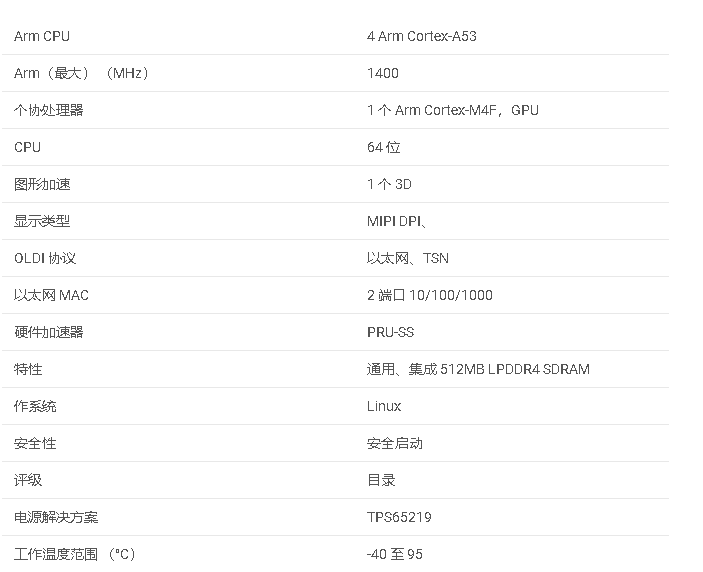

AM625SIP 通用系統(tǒng)級(jí)封裝,采用 Arm? Cortex-A53? 和集成 LPDDR4數(shù)據(jù)手冊(cè)

3D封裝與系統(tǒng)級(jí)封裝的背景體系解析介紹

全面解析系統(tǒng)級(jí)封裝SiP如何推動(dòng)新系統(tǒng)集成

全面解析系統(tǒng)級(jí)封裝SiP如何推動(dòng)新系統(tǒng)集成

評(píng)論