編者按過去幾年,因為廠商的推動,Chiplet這個概念已經(jīng)深入民心。在本文中,我們將首先討論什么是“Chiplet”、為什么需要“Chiplet”?而且會參考上文提到的西尾先生的演講內(nèi)容(已經(jīng)得到西尾先生的許可)。此外,本文還會介紹TSMC、三星電子、英特爾在此次的IEDM上發(fā)布了何種尖端封裝技術(shù)。最后,展望未來,論述含有“Chiplet”的尖端封裝技術(shù)能否牽引摩爾定律繼續(xù)前進。

什么是“Chiplet”

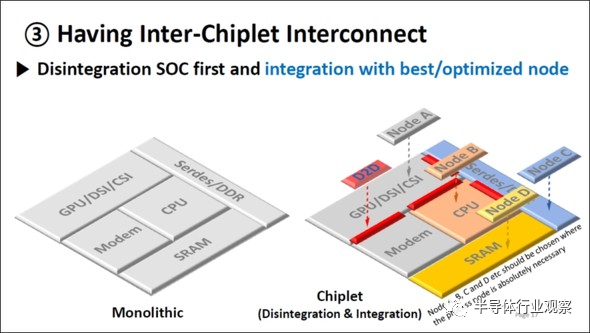

在此次的IEDM的短課程(Short Cause)上,三星電子的SE-Ho You先生做了題目為“From Package-Level to Wafer-Level Integration”的演講,且展示了“Chiplet”的未來形象。(如下圖1)

圖1:“Chiplet”是什么?出自:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1。

之前,用一個科技節(jié)點(Technology Node)可以制造出含CPU、GPU、調(diào)制解調(diào)器、SRAM、Serdes/DDR等功能的SoC(System on Chip)。

按照功能的不同,分別利用最合適的技術(shù)節(jié)點來制造。如圖1的右側(cè)所示,用Node A生產(chǎn)GPU、用Node B生產(chǎn)CPU、用Node C生產(chǎn)Serdes/DDR、用Node C生產(chǎn)SRAM,即分別在不同的晶圓上生產(chǎn),集合(Integration)以上這些功能,并匯集在一顆芯片上。

即將以上這些功能集合在一顆芯片上。

如上所述,通過連接由單獨的晶圓制造的芯片,形成具有某一功能的SoC技術(shù)就是“Chiplet”的概念。

那么,為什么“Chiplet”越來越重要呢?其原因在于尖端半導(dǎo)體需要處理的數(shù)據(jù)量成指數(shù)級增長。

不斷增長的數(shù)據(jù)量和AI半導(dǎo)體市場

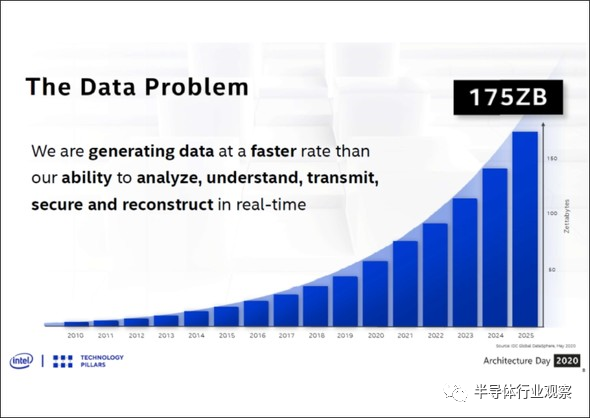

下圖2出自2020年8月13日在線舉行的“Intel Architecture Day 2020”的資料,顯示了人類創(chuàng)造的數(shù)據(jù)量的推移。從圖2可以看出,2020年的數(shù)據(jù)量超過50ZB(Zettabyte,十萬億億字節(jié),1021),預(yù)計2025年將會擴大至175ZB。

圖2:人類創(chuàng)造的數(shù)據(jù)量。(圖片出自:Intel Architecture Day 2020的資料)

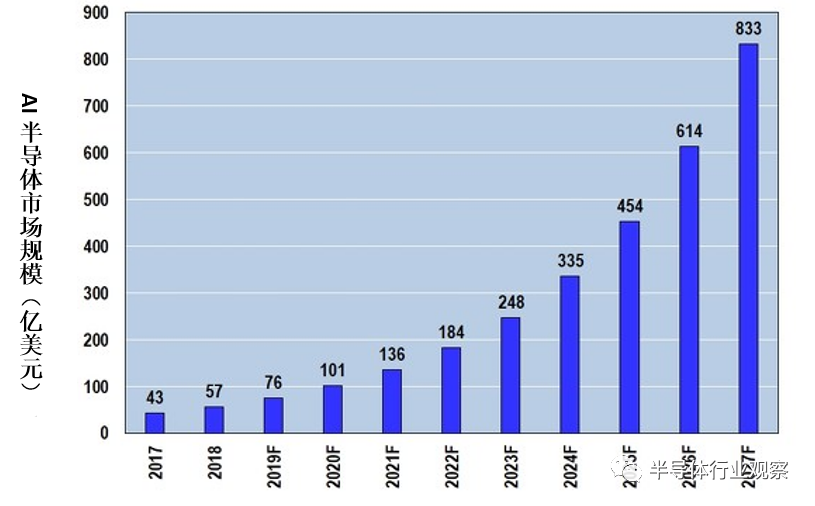

為了處理這樣龐大的數(shù)據(jù)量,所以人工智能(AI)半導(dǎo)體市場急劇擴大(如下圖3)。據(jù)預(yù)測,2020年的市場規(guī)模將超過100億美元(約人民幣646.48億元),2027年將會達到833億美元(約人民幣5,381.18億元)。

圖3:AI半導(dǎo)體市場規(guī)模推移(2019年以后為預(yù)測值)。(圖片出自:Artificial Intelligence Chip Market)

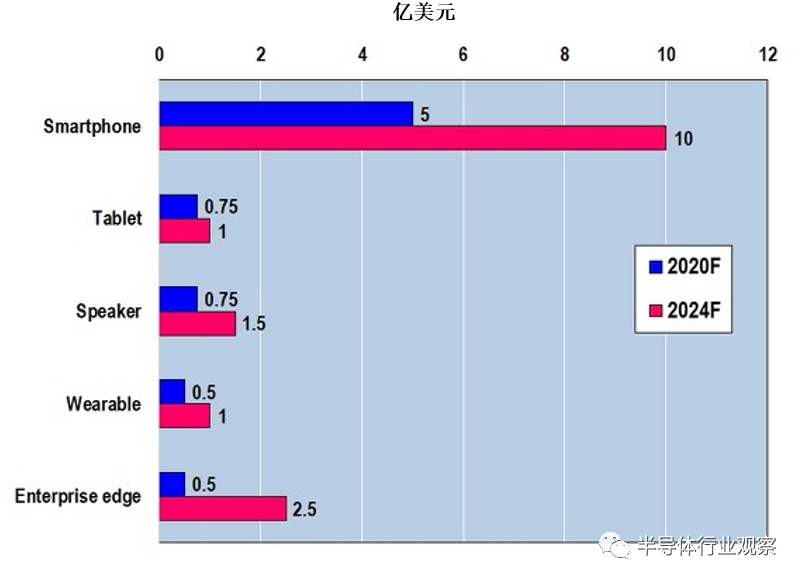

AI半導(dǎo)體的用途主要有以下:智能手機、平板電腦、音響、可穿戴設(shè)備、企業(yè)邊緣(Enterprise Edge)等(如下圖4)。AI的最大用途方向在于智能手機,據(jù)預(yù)測,2020年的規(guī)模為5億美元(約人民幣32.3億元),2024年翻至2020年的兩倍,達到10億美元(約人民幣64.6億元)。另一方面,企業(yè)邊緣的市場規(guī)模雖然不及智能手機,但2024年的市場規(guī)模為2020年(市場規(guī)模為0.5億美元,約人民幣3.23億元)的5倍,增至2.5億美元(約人民幣16.15億元)。

圖4:各種方向的AI半導(dǎo)體市場(預(yù)測值)。(圖片出自:MarketsandMarkets)

如今的4G智能手機已經(jīng)搭載了NPU(Neural Processing Unit)這一AI應(yīng)用處理器(AP,Application Processor),未來,隨著5G手機的普及,占據(jù)NPU性能、AP的空間會越來越大。因此,智能手機方向的AI市場也會出現(xiàn)增長。

此外,隨著5G的普及,云計算市場就像金字塔一樣,AI市場定會迅速擴大。即,在各種5G通信設(shè)備附近都設(shè)有搭載了AI的邊緣計算(Edge Computing,此處包含“企業(yè)邊緣”)進行高速運算處理,其上面一層為“霧計算(Fog Computing)”、再上一層為“云計算(Cloud Computing)”。

AI:從GPU到ASIC

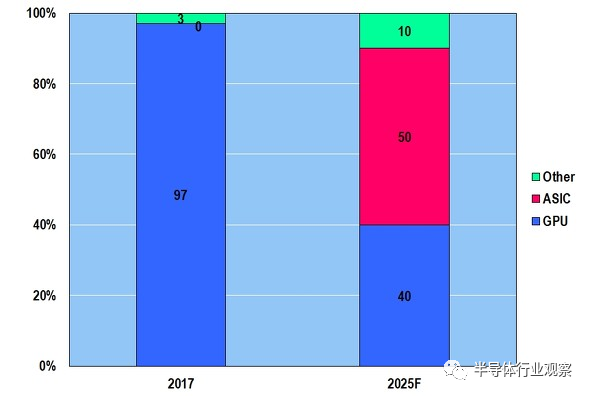

如上所述,由于大數(shù)據(jù)規(guī)模的擴大,帶動處理大數(shù)據(jù)的AI半導(dǎo)體市場增長,到底什么樣的AI半導(dǎo)體會成為主流呢---這是經(jīng)常變化的(下圖5)。在2017年,NVIDIA的GPU席卷全球,市場份額達到97%,據(jù)預(yù)測,到2025年GPU市占率會下滑至40%甚至更低,而ASIC的市占率會達到50%。

圖5:AI半導(dǎo)體種類的變化(預(yù)測)。(圖片出自:McKinsey)

換句話說,由于普通GPU(GPGPU:General-purpose computing on graphics processing units)的處理性能不足,因此出現(xiàn)了諸多專用AI半導(dǎo)體(如智能手機專用、無人駕駛汽車專用、邊緣計算機專用),且占一半以上份額。

但是,即使是ASIC AI,要處理逐年不斷增長的大數(shù)據(jù)也是十分困難的。據(jù)預(yù)測,僅靠提高芯片本身的性能已經(jīng)無法同時滿足AI半導(dǎo)體的高速處理、節(jié)能、成本優(yōu)勢等目標(biāo)。

大數(shù)據(jù)和AI半導(dǎo)體的處理能力

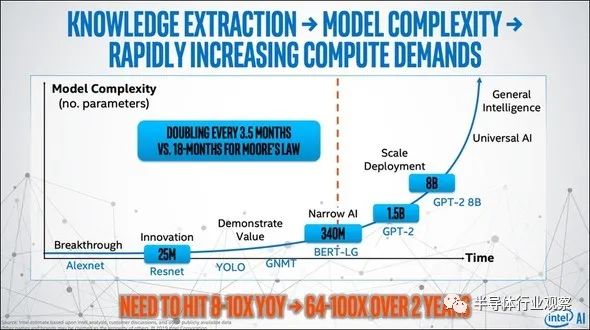

在2020年9月17日-18日召開的The Second AI HW Summit上,英特爾指出,AI半導(dǎo)體處理的數(shù)據(jù)量每3.5個月擴大兩倍、每年擴大約10倍、每兩年擴大64-100倍。(如下圖6)

圖6:AI處理的數(shù)據(jù)量每3.5個月擴大兩倍,每兩年擴大64-100倍。(圖片出自:MOOR Insights and Strategy, AI Hardware: Harder Than It Looks)

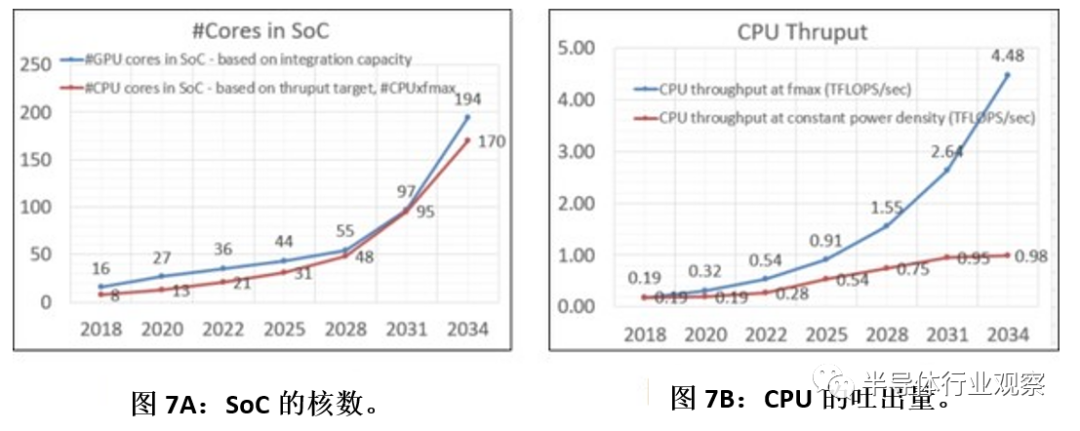

作為ASIC(或者SoC)的AI半導(dǎo)體能否處理以上這些成指數(shù)級增長的數(shù)據(jù)量?下圖7是2018年版的IRDS(International Roadmap for Devices and systems)登載的SoC的CPU、GPU核數(shù)、CPU吐出量(處理能力)。

圖7:SoC的核數(shù)、CPU的吐出量。(圖片出自:IRDS2018)

2020年SoC中的CPU核數(shù)為13,GPU為27個,到2031年,CPU增至95個(7.3倍)、GPU增至97個(3.6倍)。其中,CPU的吐出量在2020年為0.32 TFLOPS/sec、2031年將會增為2.64 TFLOPS/sec,增長了8.25倍。但是,這是不考慮因發(fā)熱問題而產(chǎn)生的速度下降問題,如果因發(fā)熱而導(dǎo)致速度下降,2031年的吐出量僅為0.95 TFLOPS/sec,增長約3倍。

所謂的“TFLOPS/sec”指的是“tera floating-point operations per second”的縮略,是表示計算機處理能力的單位,tera為1萬億,F(xiàn)LOPS為每秒浮點計算次數(shù)。因此,1 TFLOPS為浮點每秒計算一萬億次。

那么,從2020年到2031年,SoC中的CPU核數(shù)將增長7.3倍,增至95個,如果不考慮因發(fā)熱引起的速度低下問題,CPU的預(yù)測速度將提高8.25倍,提高至2.64 TFLOPS/sec。因此,預(yù)計在2031年登場的SoC AI半導(dǎo)體與2020年相比,其計算能力將會提高60倍=7.3*8.25。

但是,AI半導(dǎo)體處理的數(shù)據(jù)量如上圖6英特爾所展示的一樣,在兩年內(nèi)增長64-100倍,即使是最小值64倍,在2031年將會達到10億倍(2020年的64的五次方),僅靠增加核數(shù)、提高各核的吐出量,處理能力還是不足。

隨著核數(shù)的增加、SoC成本也增加

與持續(xù)增長的數(shù)據(jù)量形成對比,SoC AI半導(dǎo)體的處理能力完全不足。但是,為了提高處理能力,只能增加SoC的核數(shù)、持續(xù)擴大各核的吐出量。因此需要進一步提高微縮化(Scaling)。但是,隨之而來的高昂的晶圓成本又是一大問題。

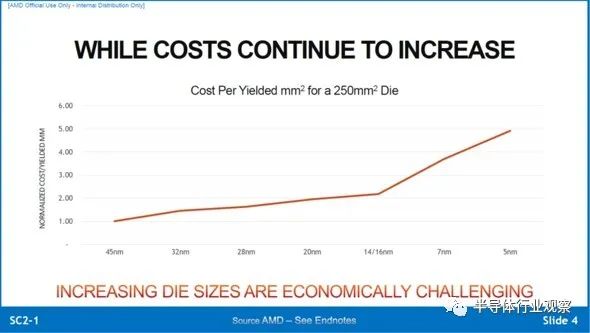

下圖8是2020年VLSI座談會上的演講內(nèi)容,AMD的Samuel Naffziger先生發(fā)表了名為“Chiplet Meets The Real World -- Benefits and Limits of Chiplet Designs”的演講,同時展示了微縮化與芯片成本的關(guān)系。

圖8:微縮化與芯片成本的增長。(圖片出自:Samuel Naffziger (AMD), “Chiplet Meets The Real World -- Benefits and Limits of Chiplet Designs ”, VLSI2020, Short Course 2-1.)

如果把利用45納米節(jié)點生產(chǎn)的芯片成本看做“1”,隨著微縮化發(fā)展,芯片成本也增長,5納米節(jié)點下的成本為45納米節(jié)點的五倍。從圖8可以看出,14納米/16納米節(jié)點以后,圖表呈現(xiàn)急劇增長趨勢,此處應(yīng)該是采用了EUV(極紫外光刻)技術(shù)。

微縮化照此發(fā)展下去,芯片成本勢必會增長,即便如此,為了提高AI半導(dǎo)體的處理能力,TSMC、三星電子都在發(fā)展微縮化。此外,雖然必須要增加核數(shù),但其成本的增長會遠遠超過微縮化花費的成本。然而,能解決以上問題的方案就是“Chiplet”。

Chiplet可以控制因核數(shù)增加帶來的高昂成本

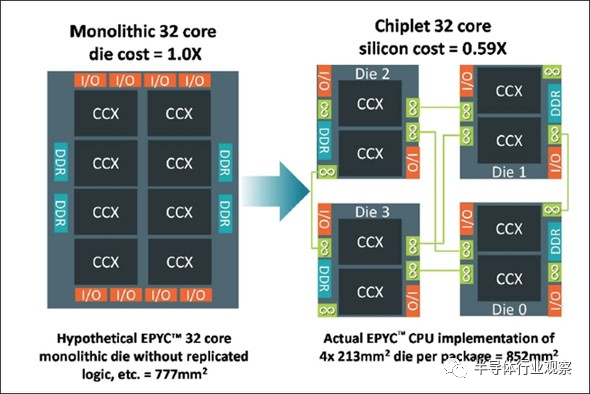

下圖9是用于AMD服務(wù)器的處理器“EPYC”。“EPYC”是擁有32核的CPU,如果用一顆芯片來做的話,就會像圖9左邊一樣,芯片面積達到777mm2。按照Chiplet的方法來處理這顆大型芯片的話,就會像圖9右側(cè)一樣生成四份,再連接。分成四份后各個芯片的面積為213mm2,213*4=852mm2,比分割之前更大,即使把多出的面積去掉也比分割前更有優(yōu)勢。(下圖10進行說明)

圖9:將32核的處理器分為四份的AMD的EPYC。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

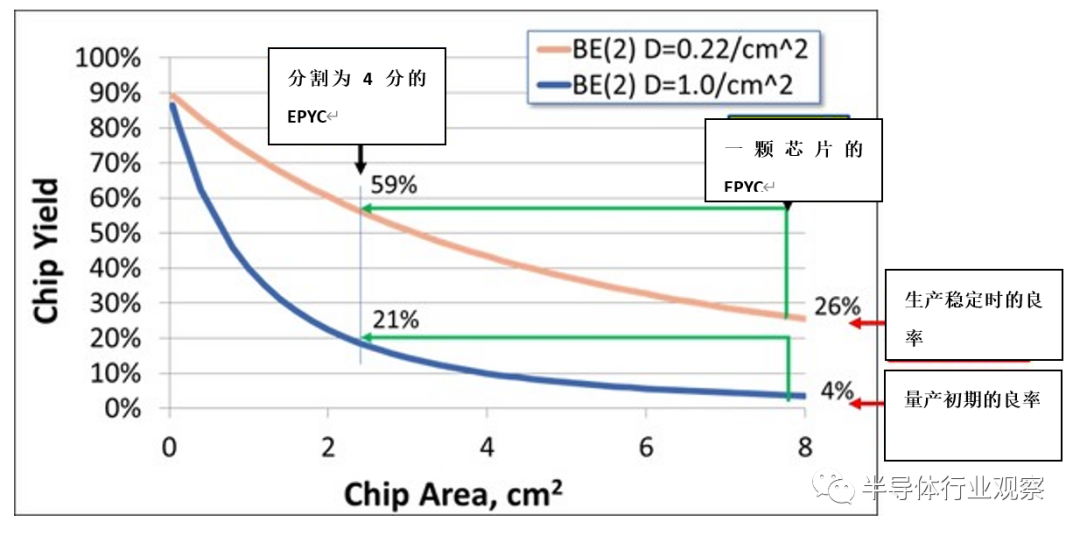

下圖10的橫軸為芯片面積,縱軸為良率,藍色線條可以看做是量產(chǎn)初期時的良率(缺陷密度為1個/cm2),另一方面,橙色線條可以看做是改善了量產(chǎn)工藝后穩(wěn)定生產(chǎn)時的良率(缺陷密度為0.22個/cm2)。

圖10:芯片面積和良率的關(guān)系。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

那么,用一顆芯片生產(chǎn)EPYC的情況下,量產(chǎn)初期的良率僅有4%,即使優(yōu)化工藝流程,良率也僅為26%。

而被分為四份的EPYC(213mm2)在量產(chǎn)初期的良率為21%,優(yōu)化工藝流程、生產(chǎn)穩(wěn)定時的良率達到了59%,即,分割后的芯片的量產(chǎn)初期良率是分割前的5.3倍,穩(wěn)定時的良率是分割前的2.3倍。

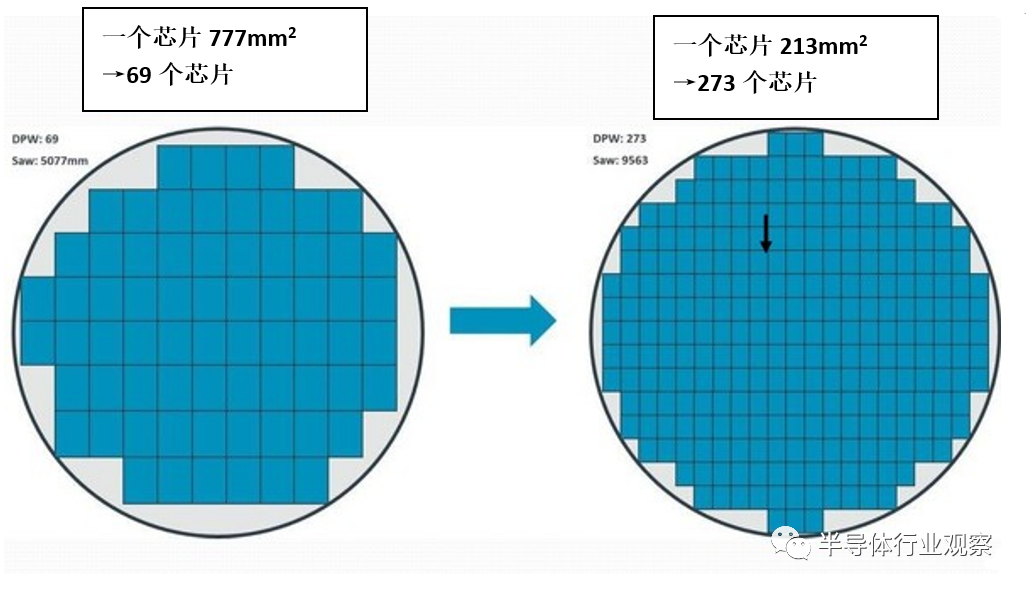

在這種條件下,1顆晶圓可以做出多少個EPYC呢,在下圖11中進行說明。用一顆面積為777mm2的芯片來生產(chǎn)EPYC的話,一顆晶圓可生產(chǎn)出約69顆芯片,由于生產(chǎn)穩(wěn)定時的良率為26%,因此實際可獲得的芯片數(shù)量為69*26%=17顆。

另一方面,分成四份后的芯片面積為213mm2,那么一顆晶圓可產(chǎn)出273個芯片,假如生產(chǎn)穩(wěn)定時的良率為59%,可獲得的芯片數(shù)量為273*59%=161個。由于四個組成一個芯片,因此實際可做出161/4=40個EPYC。

圖11:芯片面積與從晶圓上獲得的數(shù)量。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

綜上所述,用一個芯片(777mm2)來做的話,實際獲得的EPYC數(shù)量為17個,而分割為四份的話,可以多做出2.4倍的EPYC。反過來說,通過四分芯片,EPYC的成本也會降低1/2.4。

通過分割芯片來提高良率,結(jié)果降低了單顆芯片的成本。這是Chiplet的優(yōu)勢之一,不過Chiplet的優(yōu)勢不限于以上。

像樂高積木一樣的形成SoC

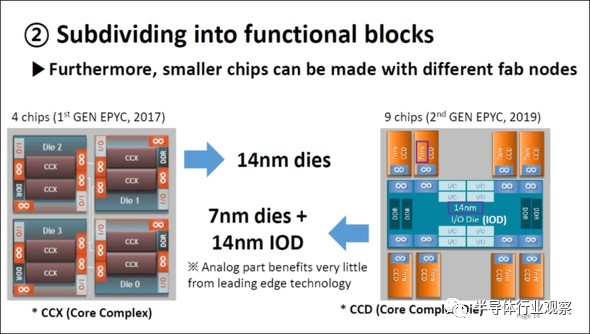

下圖12是AMD的第一代、第二代EPYC(用于服務(wù)器的處理器)的比較圖。第一代EPYC采用的是由4個14納米的芯片組成;在第二代中,橙色為用7納米制作的“處理器8芯”,藍色為用14納米制作的Input/Output(IO)芯片,將以上這些安裝在Interposer上,就制成了用于EPYC的處理器。

圖12:第一代EPYC和第二代EPYC的區(qū)別。(圖片出自:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1)

要求最高的處理器采用了2019年當(dāng)時最先進的7納米工藝,而I/O使用的不是那么尖端的14納米,即不同的芯片選擇使用不同的合適工藝節(jié)點。

而三星的厲害“絕技”在下圖1,不使用Chiplet的情況下,如圖1左側(cè)所示,整個芯片必須由同一個技術(shù)節(jié)點制造。就利害而言,芯片面積越大,良率越低,那么單顆芯片的成本也就越高(如上文所述)。除此之外,為了在同一個Mask上配置CPU、GPU、調(diào)制解調(diào)器、SRAM、Serdes/DDR,需要將精密的圖案與粗略的圖案混合,使制造工藝更復(fù)雜。

另一方面,在圖1的右側(cè),各個產(chǎn)品都是按照其自身的功能來選擇合適的節(jié)點生產(chǎn)的,如GPU采用A節(jié)點、CPU采用B節(jié)點、SRAM采用C節(jié)點、I/O采用D節(jié)點,然后將它們安裝在一個Interposer 上。各種半導(dǎo)體模組就像樂高積木一樣堆疊在一起。

Chiplet擁有以上優(yōu)勢。通過有序地配置CPU、GPU、DRAM等產(chǎn)品,從而進一步提高SoC AI的處理能力。

用HBM(High Bandwidth Memory)實現(xiàn)高速化

下圖13是搭載了GDDR5規(guī)格DRAM的傳統(tǒng)SoC和搭載了縱向壓層的HBM(High Bandwidth Memory,用TSV連接GDDR5)的SoC的比較圖。通過利用HBM,縱向縮短了1.6倍、橫向縮短了2倍、面積縮短了3倍。即,DRAM和SoC的合計占用面積為1/3。可以說這也是是靈活運用Chiplet的一個事例。

圖13:搭載了HBM(High Bandwidth Memory)的SoC。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

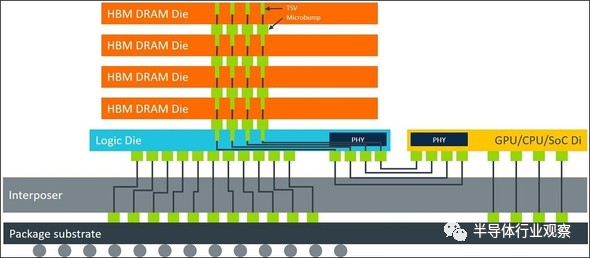

下圖14是搭載了HBM(High Bandwidth Memory)的SoC的斷面圖,用TSV連接的DRAM經(jīng)由邏輯芯片和Interposer,與SoC相連接。在需要高速處理的SoC的旁邊配有HBM,因此誕生了可以迅速傳輸數(shù)據(jù)的存儲半導(dǎo)體。

圖14:配置有HBM(High Bandwidth Memory)的SoC的斷面圖。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

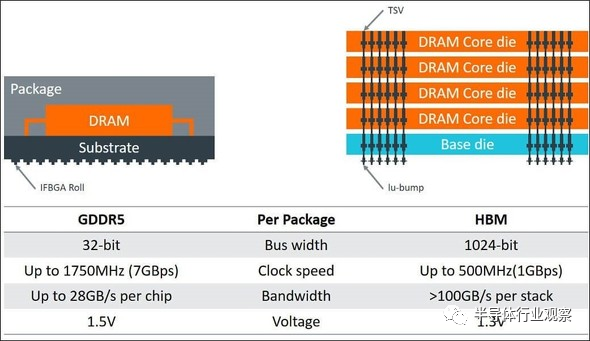

下圖15是GDDR5和HBM 的Bus Width、Clock Speed、Bandwidth、動作Voltage的比較圖。GDDR5的Bus Width為32比特,HBM是其32倍,為1,024比特。結(jié)果,GDDR5的時鐘頻率(Clock Rate)為1,750MHz,HBM為500MHz,GDDR5的一顆芯片的Bandwidth為25GB/s,HBM的一個Block為100GB/s,是前者的4倍。

圖15:HBM(High Bandwidth Memory)的帶寬大小。(圖片出自:Greg Yeric, arm community, “Three Dimensions in 3DIC - Part I”, April 2, 2018)

總之,一個GDDR5就相當(dāng)于在單行道上高速行駛的卡車,因此可傳輸?shù)臄?shù)據(jù)量是有限的,HBM的情況下,相當(dāng)于四輛行駛在四車道上的卡車,一次傳輸?shù)臄?shù)據(jù)量也是前者的四倍。

如果運用HBM可以較好地使用Chiplet的話,那么SoC AI也可以高速運行。終于解釋清楚了什么是Chiplet以及其存儲半導(dǎo)體。那么,在IEDM上,英特爾、三星、TSMC分別發(fā)布了什么呢?

在IEDM上,英特爾和三星發(fā)布了尖端封裝技術(shù)

英特爾的Ravi Mahajan先生在“Advanced Packaging Technologies for Heterogeneous Integration(HI)”上,對尖端封裝進行了說明(如下圖16)。就Embedded Multi-Die Interconnect Bridge(EMIB)而言,分割處理器核(Processor Core)并生產(chǎn)以后,經(jīng)由Interposer,再集成(Integration)、制成芯片。此外,就Foveros而言,經(jīng)由TSV壓層不同的芯片,制成一顆芯片。最后獲得由EMIB和Foveros組合的Co-EMIB。

圖16:英特爾的3D封裝(EMIB、Foveros、Co-EMIB)。(圖片出自:Ravi Mahajan (Intel), “Advanced Packaging Technologies for Heterogeneous Integration (HI)”, IEDM2020, Tutorial2.)

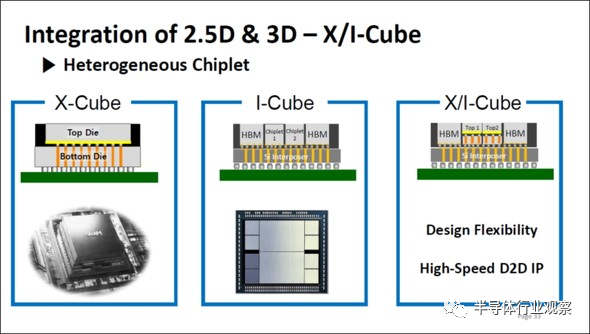

下圖17是三星電子的SE-Ho You先生在From Package-Level to Wafer-Level Integration上發(fā)布的資料。X-Cube指的是用TSV壓層不同的芯片,可以說相當(dāng)于英特爾的Foveros。此外,經(jīng)由Interposer連接了不同的芯片的I-Cube與英特爾的EMIB類似。此外,組合了X-Cube和I-Cube的X/I-Cube與英特爾的Co-EMIB非常類似。

筆者雖然不知道是三星電子還是英特爾率先研發(fā)了以上成果,但可以斷言二者是非常類似的。

圖17:三星的3D封裝(X-Cube、I-Cube、X/I-Cube)。(圖片出自:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1)

TSMC在IEDM上的發(fā)布內(nèi)容

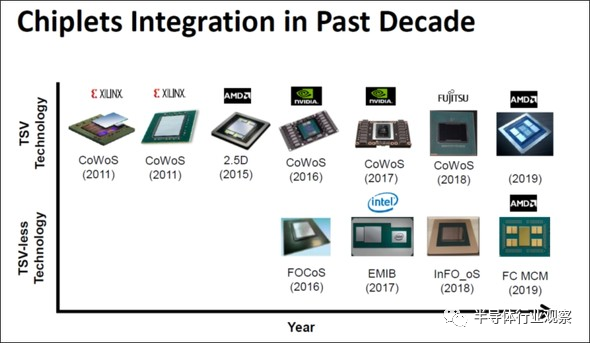

TSMC比三星、英特爾更早地采用了Chiplet的封裝方法。TSMC的KC Yee先生在IEDM的“Advanced 3D System Integration Technologies”上回顧了過去十年間Chiplet的歷史。(下圖18)

圖18:TSMC在IEDM上公布的Chiplet。(圖片出自:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1)

圖18的上半部分是被稱為CoWoS(Chip-on-Wafer-on-Substrate)的Chiplet技術(shù),2011年被應(yīng)用于Xilinx的FPGA。后來,又被應(yīng)用于NVIDIA的GPU、AMD的CPU。

此外,圖18的下半部分是一種不使用TSV、經(jīng)由Interposer連接芯片的Chiplet技術(shù),被稱為InFO(Integrated Fan-Out)。圖18上雖然沒有注明,蘋果手機的處理器中采用了InFO技術(shù)。(下圖19)

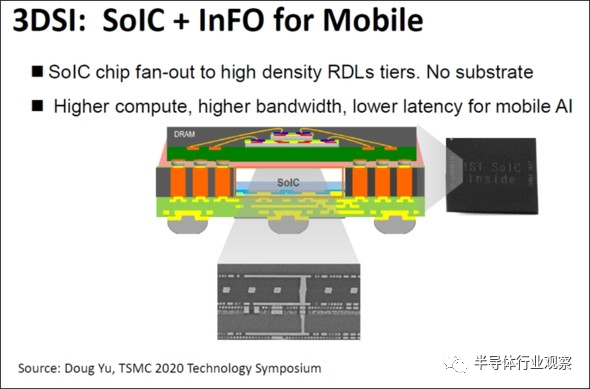

圖19:TSMC的用于智能手機的3DSI(3D System Integration)。(圖片出自:KC Yee (TSMC), “Advanced 3D System Integration Technologies”, IEDM2020, SC1)

TSMC將此項技術(shù)命名為“3DSI(3D System Integration)”,也適用于高性能計算(High Performance Computing)方向的CoWoS(下圖20)。即,圖19 和圖20中出現(xiàn)的SoIC是“System on Integrated Chips using frontend 3D stacking process”的略稱,是以3D方式來堆疊芯片的技術(shù)。

從以上可得知,TSMC在Chiplet尖端封裝技術(shù)領(lǐng)域有十年的經(jīng)驗,領(lǐng)先于英特爾和三星。

采用Chiplet的尖端封裝方式的未來展望

采用ASML制造的最尖端的EUV曝光設(shè)備,TSMC和三星才得以按照5納米、4納米、3納米、1納米的進程發(fā)展微縮化,但是,要提高AI半導(dǎo)體(用以解決成指數(shù)級增長的大數(shù)據(jù))的處理能力,進靠增加核數(shù)、微縮化來提高核的吐出量還遠遠不夠。此外,提高微縮化、增加核數(shù)都會產(chǎn)生高昂成本。

為解決以上問題,必須要研發(fā)采用了Chiplet的尖端封裝技術(shù),因此,TSMC、英特爾、三星都已經(jīng)開始研發(fā)尖端封裝技術(shù)。如今,TSMC的尖端封裝技術(shù)領(lǐng)先于其他公司,半導(dǎo)體行業(yè)沒有固定的標(biāo)準(zhǔn),可謂是百花齊放、百家爭鳴。

基于以上情況,采用的Chiplet的尖端封裝技術(shù)也許沒有像IRDS那樣的技術(shù)藍圖。因此,我們很難預(yù)測未來會出現(xiàn)什么技術(shù)。

比方說,在此次的IEDM上,在TSMC的發(fā)布結(jié)束后,CEA Leti的C.Fenouillet-Beranger先生在“3D sequential integration: Opportunities, Breakthrough and Challenge”上提出了一項非常有意思的尖端封裝技術(shù)的概念。(如下圖21)

圖21:3D 3D System Integration的未來。(圖片出自:C.Fenouillet-Beranger (CEA Leti), “3D sequential integration: Opportunities, Breakthrough and Challenges”, IEDM2020, SC1)

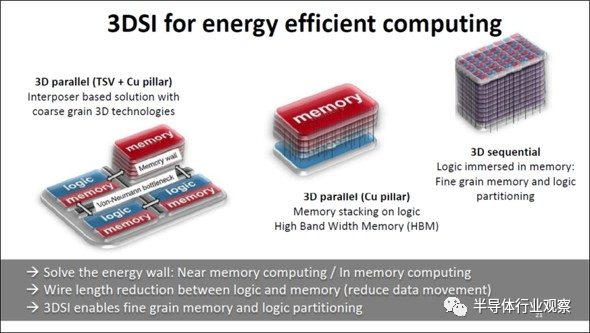

當(dāng)下,如圖21的左邊所示,融合存儲半導(dǎo)體(HBM)、各種邏輯半導(dǎo)體并安裝在一顆Interposer上,構(gòu)筑SoC。下一個階段是利用TSV將存儲半導(dǎo)體和多個邏輯半導(dǎo)體縱向堆疊,合成一顆芯片。而且,在最后階段,會在存儲半導(dǎo)體內(nèi)部連續(xù)嵌入多個邏輯半導(dǎo)體,即所謂的堆疊式“3D sequential”。

因此,牽引未來摩爾定律的不是微縮化(雖然微縮化已經(jīng)做出了很大的貢獻),而是采用了Chiplet的尖端封裝技術(shù)。

此外,2月9日TSMC公布說要在日本筑波市建設(shè)半導(dǎo)體后段工序的研發(fā)據(jù)點,期待能夠采用日本的材料、創(chuàng)造出先進的3D封裝技術(shù)。

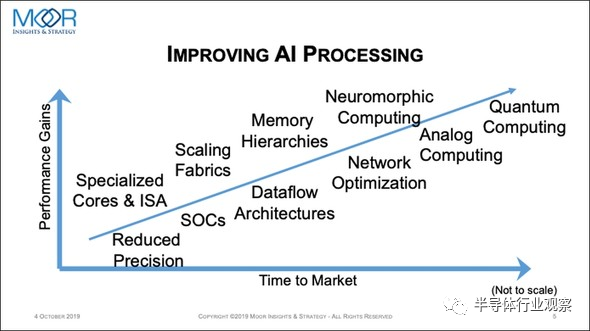

即使先進封裝方式繼續(xù)發(fā)展,如果當(dāng)下的數(shù)字存儲半導(dǎo)體、數(shù)字邏輯半導(dǎo)體無法適用的話,如下圖22所示,就需要轉(zhuǎn)為Neuromorphic Computing、Analog Computing、Quantum Computing等。

圖22:AI處理技術(shù)進步的趨勢。(圖片出自::MOOR Insights and Strategy, AI Hardware: Harder Than It Looks)

也許在五年后的2025年前后最新的智能手機會搭載Neuromorphic(作為大腦型計算機而被研發(fā)的),此外,在2030年前后,也許量子計算機會被搭載到最新型的PC上。

假設(shè)以上皆為可能,人類第一步要走的是消滅新冠肺炎,繼續(xù)勤洗手、勤漱口、佩戴口罩,期待疫苗發(fā)揮良效。

責(zé)任編輯:lq

-

三星電子

+關(guān)注

關(guān)注

34文章

15894瀏覽量

183138 -

晶圓制造

+關(guān)注

關(guān)注

7文章

310瀏覽量

25289 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13605

原文標(biāo)題:巨頭競逐Chiplet

文章出處:【微信號:半導(dǎo)體科技評論,微信公眾號:半導(dǎo)體科技評論】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

躍昉科技受邀出席第四屆HiPi Chiplet論壇

華大九天Argus 3D重塑3D IC全鏈路PV驗證新格局

Chiplet,改變了芯片

CMOS 2.0與Chiplet兩種創(chuàng)新技術(shù)的區(qū)別

淺談3D封裝與CoWoS封裝

Chiplet與3D封裝技術(shù):后摩爾時代的芯片革命與屹立芯創(chuàng)的良率保障

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

突破!華為先進封裝技術(shù)揭開神秘面紗

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應(yīng)用

淺談Chiplet與先進封裝

淺談MOS管封裝技術(shù)的演變

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導(dǎo)體新飛躍

Chiplet:芯片良率與可靠性的新保障!

含有“Chiplet”的尖端封裝技術(shù)能否牽引摩爾定律繼續(xù)前進

含有“Chiplet”的尖端封裝技術(shù)能否牽引摩爾定律繼續(xù)前進

評論