大俠好,許久不見。今天“寧夏李治廷”給各位大俠帶來基于FPGA VHDL 的 FSK調制與解調。 以后機會多多,慢慢分享一些項目開發以及深造學習方面的內容,歡迎各位大俠一起切磋交流,華山論劍,不論成敗,取其精華,去其糟粕,共同進步。話不多說,上貨。

一、VHDL語言

VHDL誕生于1982年。在1987年底,VHDL被IEEE和美國國防部確認為標準硬件描述語言。自IEEE公布了VHDL的標準版本,IEEE-1076(簡稱87版)之后,各EDA公司相繼推出了自己的VHDL設計環境,或宣布自己的設計工具可以和VHDL接口。此后VHDL在電子設計領域得到了廣泛的接受,并逐步取代了原有的非標準的硬件描述語言。而Verilog HDL是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首創的,最初只設計了一個仿真與驗證工具,之后又陸續開發了相關的故障模擬與時序分析工具。1985年Moorby推出它的第三個商用仿真器Verilog-XL,獲得了巨大的成功,從而使得Verilog HDL迅速得到推廣應用。1989年CADENCE公司收購了GDA公司,使得VerilogHDL成為了該公司的獨家專利。1990年CADENCE公司公開發表了Verilog HDL,并成立LVI組織以促進Verilog HDL成為IEEE標準,即IEEE Standard 1364-1995。VHDL的邏輯綜合就較之Verilog HDL要出色一些,強調于組合邏輯的綜合。

二、FSK

頻移鍵控(Frequency Shift Keying.FSK)是用不同頻率的載波來傳遞數字信號,并用數字基帶信號控制載波信號的頻率,具有抗噪聲性能好、傳輸距離遠、誤碼率低等優點。在中低速數據傳輸中,特別是在衰落信道和頻帶較寬的信道中傳輸數據時,有著廣泛的應用。

三、實現

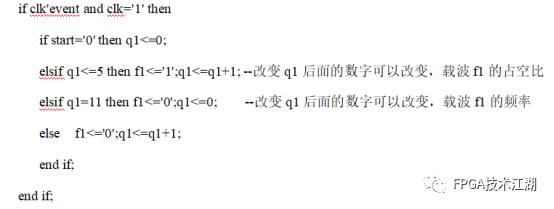

1.FSK調制VHDL主要程序

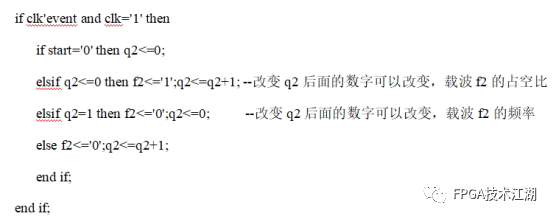

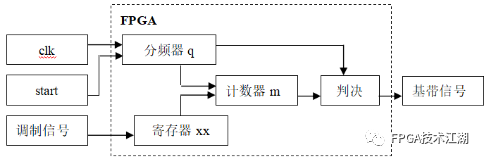

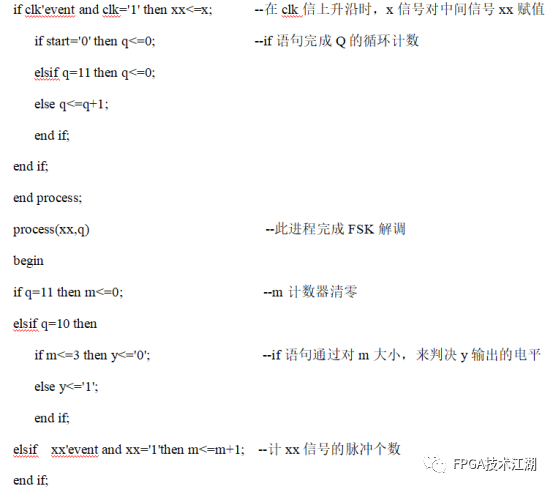

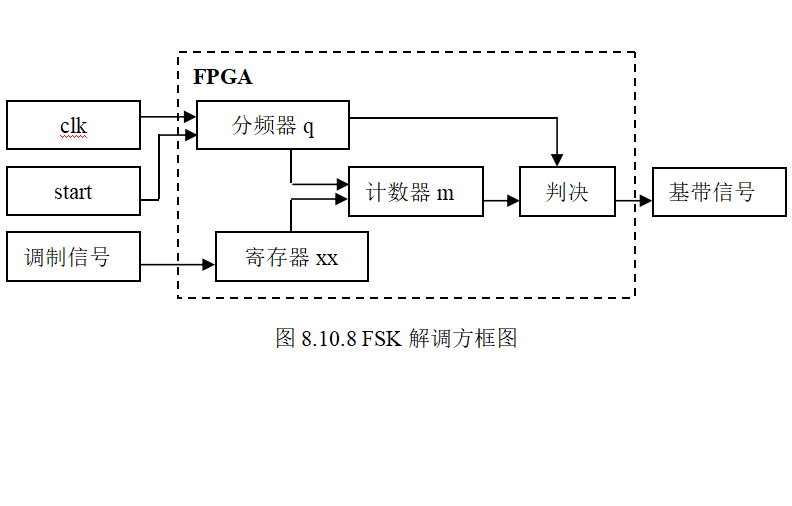

2.FSK解調VHDL主要程序

四、仿真

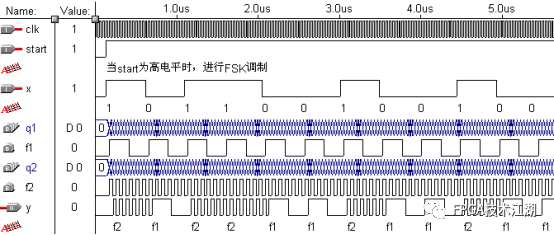

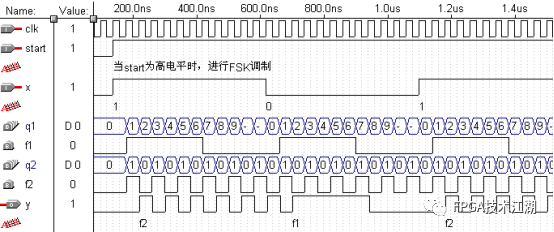

1.FSK調制VHDL程序仿真圖

a. 載波f1、f2分別是通過對clk的12分頻和2分頻得到的。

b. 基帶碼長為載波f1的2個周期,為載波f2的6個周期。

c. 輸出的調制信號y在時間上滯后于載波信號一個clk,滯后于系統時鐘2個clk。

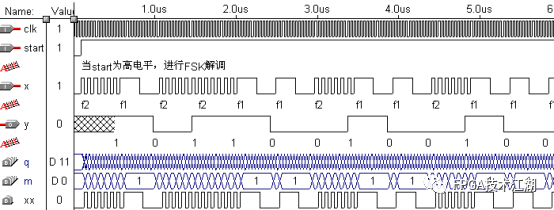

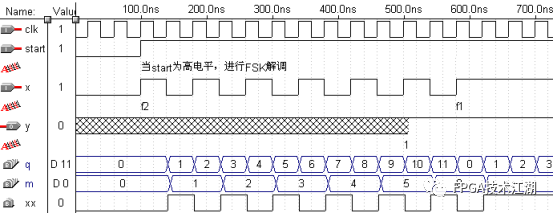

2. FSK解調VHDL程序仿真圖

a. 在q=11時,m清零。

b. 在q=10時,根據m的大小,進行對輸出基帶信號y的電平的判決。

c. 在q為其它值時,計數器m計下xx(寄存x信號)的脈沖數。

d. 輸出信號y滯后輸入信號x 10個clk。

本次分享到此結束,各位大俠,有緣再見,告辭。

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638501 -

仿真器

+關注

關注

14文章

1052瀏覽量

88133 -

vhdl

+關注

關注

30文章

822瀏覽量

131834 -

FSK調制

+關注

關注

0文章

9瀏覽量

8067

原文標題:往期精選:基于FPGA VHDL 的 FSK調制與解調設計

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于MSP430的FSK調制解調器

【資料分享】基于FPGA的FSK調制解器器設計

基于FPGA的MSK調制解調器設計與應用

Quartus II平臺下實現全數字FSK調制解調器

基于VHDL的QPSK調制解調系統設計與仿真

基于FPGA VHDL的FSK調制與解調設計

基于FPGA VHDL的FSK調制與解調設計

評論