晶振被譽(yù)為“電子設(shè)備的心臟”,它是電子產(chǎn)品中最常用的不可或缺的組件,小到手機(jī)、電腦,大到導(dǎo)彈、衛(wèi)星都需要晶體振蕩器。作為PCB設(shè)計(jì)工程師,關(guān)于晶振的知識(shí)你一定得搞明白噢~

晶振

晶體振蕩器是指從一塊石英晶體上按一定方位角切下薄片(簡(jiǎn)稱為晶片),石英晶體諧振器,簡(jiǎn)稱為石英晶體或晶體、晶振;而在封裝內(nèi)部添加 IC 組成振蕩電路的晶體元件稱為晶體振蕩器。其產(chǎn)品一般用金屬外殼封裝,也有用玻璃殼、陶瓷或塑料封裝的。

晶振的作用

晶振是時(shí)鐘電路中最重要的部件,它的主要作用是向顯卡、網(wǎng)卡、主板等配件的各部分提供基準(zhǔn)頻率,它就像個(gè)標(biāo)尺,工作頻率不穩(wěn)定會(huì)造成相關(guān)設(shè)備工作頻率不穩(wěn)定,自然容易出現(xiàn)問(wèn)題。在通常工作條件下,普通的晶振頻率絕對(duì)精度可達(dá)百萬(wàn)分之五十,高級(jí)的精度更高。

晶振的另一個(gè)作用是為系統(tǒng)提供基本的時(shí)鐘信號(hào)。通常一個(gè)系統(tǒng)共用一個(gè)晶振,便于各部分保持同步。有些通訊系統(tǒng)的基頻和射頻使用不同的晶振,而通過(guò)電子調(diào)整頻率的方法保持同步。

晶振電路的PCB設(shè)計(jì)

位置要選對(duì):晶振內(nèi)部是石英晶體,如果不慎掉落或受不明撞擊,石英晶體易斷裂破損,所以晶振的放置遠(yuǎn)離板邊,靠近MCU的位置布局。

兩靠近:耦合電容應(yīng)盡量靠近晶振的電源管腳,如果多個(gè)耦合電容,按照電源流入方向,依次容值從大到小擺放;晶振則要盡量的靠近MCU。

走線短:所有連接晶振輸入/輸出端的導(dǎo)線盡量短,以減少噪聲干擾及分布電容對(duì)晶振的影響。

高獨(dú)立:盡可能保證晶振周圍的沒(méi)有其他元件。防止器件之間的互相干擾,影響時(shí)鐘和其他信號(hào)的質(zhì)量。晶振周圍 1mm 禁布器件,0.5mm 禁布過(guò)孔走線,所有晶振下不打過(guò)孔(包括地過(guò)孔)。

外殼要接地:晶振的外殼必須要接地,除了防止晶振向外輻射,也可以屏蔽外來(lái)的干擾。

01

晶體振蕩單元(無(wú)源晶振)的布線規(guī)則

1、振蕩電路(振蕩單元、振蕩電容)應(yīng)配置在振蕩IC附近;

2、晶振電路下面的各層都需要鋪地,不能放置器件和走線,尤其是高頻信號(hào)線路;

3、晶振電路做包地處理時(shí)需要打大量地孔,否則包地?zé)o意義;

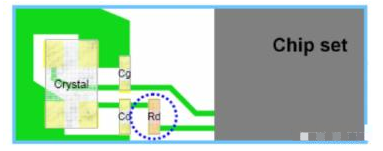

4、四腳晶振,建議晶振走線從內(nèi)部走,減小晶振的環(huán)路,如下圖所示。

02

石英晶體振蕩器(有源晶振)的布線規(guī)則

1、振蕩電路(振蕩單元、振蕩電容)應(yīng)配置在振蕩IC附近;

2、晶振電路下面的各層都需要鋪地,不能放置器件和走線,尤其是高頻信號(hào)線路;

3、晶振電路做包地處理時(shí)需要打大量地孔,否則包地?zé)o意義;

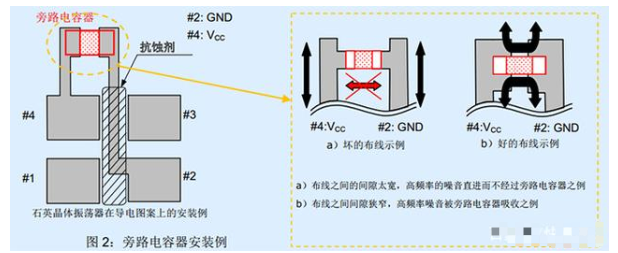

4、電源先經(jīng)過(guò)旁路電容,然后再進(jìn)入晶振,如下圖所示(高頻噪聲通常直線前進(jìn))。

晶振起振的可靠性

單片機(jī)晶振不起振是常見(jiàn)現(xiàn)象,那么引起晶振不起振的原因有哪些呢?如何解決?

01

晶振不起振的原因

1、PCB布線錯(cuò)誤,現(xiàn)在的PCB不再是單一功能電路(數(shù)字或模擬電路),而是由數(shù)字電路和模擬電路混合組成的。因此,PCB布線的時(shí)候可能出現(xiàn)問(wèn)題導(dǎo)致晶振不起振;

2、單片機(jī)或晶振的質(zhì)量問(wèn)題;

3、負(fù)載二極管或匹配電容與晶振不匹配或者電容質(zhì)量有問(wèn)題;

4、PCB板受潮,導(dǎo)致阻抗失配而不能起振;

5、晶振電路的走線過(guò)長(zhǎng)或兩腳之間有走線導(dǎo)致晶振不起振,通常我們?cè)赑CB布線時(shí)晶振電路的走線應(yīng)盡量短且盡可能靠近振蕩器,嚴(yán)禁在晶振兩腳間走線;

6、晶振受外圍電路的影響而不起振。

02

晶振不起振的解決方案

1、排除電路錯(cuò)誤的可能性,因此你可以用相應(yīng)型號(hào)單片機(jī)的推薦電路進(jìn)行比較。

2、排除外圍元件不良的可能性,因?yàn)橥鈬慵o(wú)非為電阻,電容,你很容易鑒別是否為良品。

3、排除晶振為停振品的可能性,因?yàn)槟悴粫?huì)只試了一二個(gè)晶振。

4、試著改換晶體兩端的電容,也許晶振就能起振了,電容的大小請(qǐng)參考晶振的使用說(shuō)明。

5、在 PCB 布線時(shí)晶振電路的走線應(yīng)盡量短且盡可能靠近 IC,杜絕在晶振兩腳間走線。

責(zé)任編輯:lq6

-

電容

+關(guān)注

關(guān)注

100文章

6487瀏覽量

159405 -

晶振

+關(guān)注

關(guān)注

35文章

3564瀏覽量

73465 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

247瀏覽量

53773

發(fā)布評(píng)論請(qǐng)先 登錄

什么是BSP工程師

硬件工程師:這才是真正的大學(xué)生就業(yè)指導(dǎo) #電子 #硬件工程師 #電子愛(ài)好者 #晶振 #揚(yáng)興科技

淺談晶振在PCB設(shè)計(jì)中的要點(diǎn)

晶振電路的PCB設(shè)計(jì)

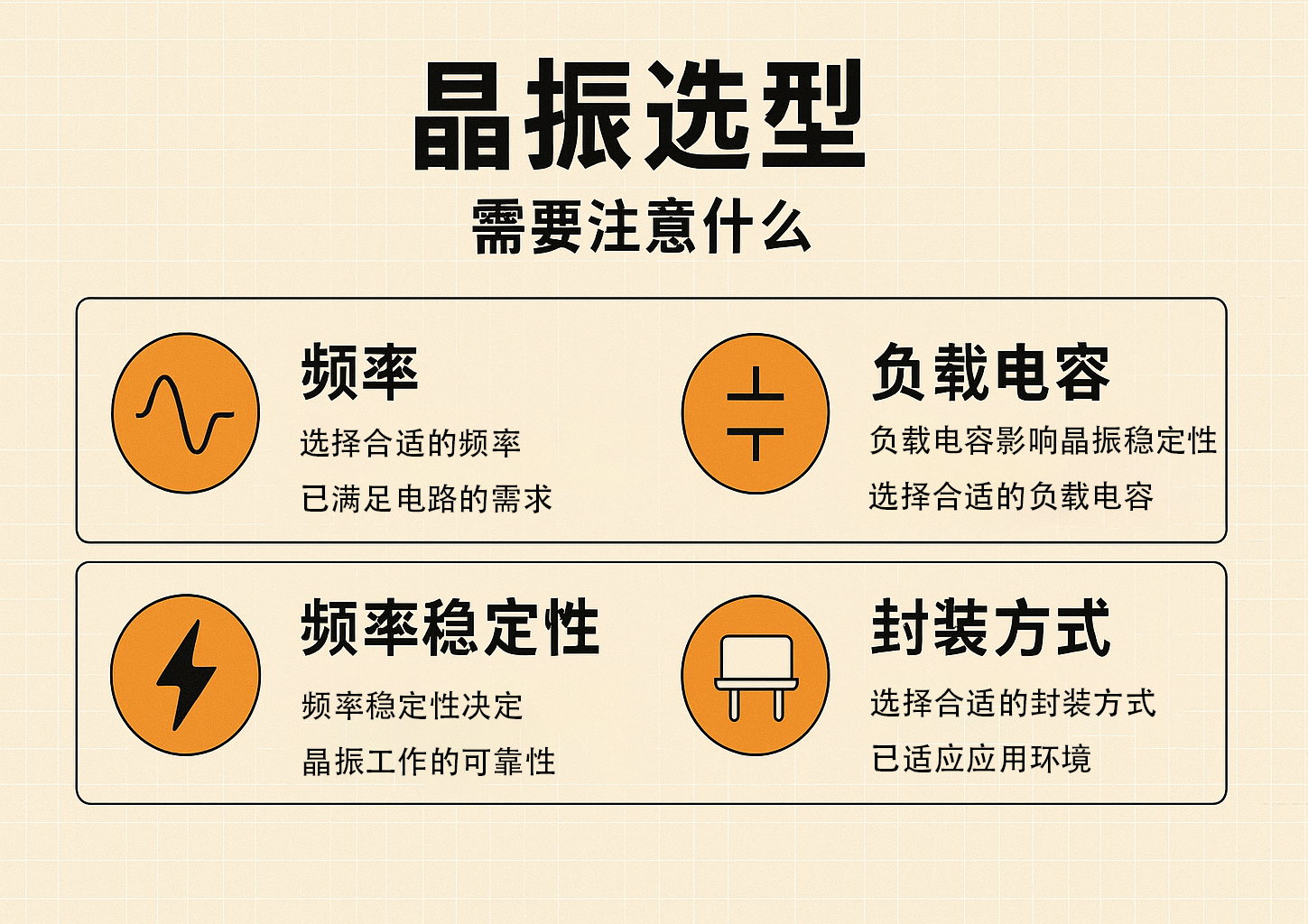

電子工程師必看:晶振選型的 5 大關(guān)鍵點(diǎn)

技術(shù)資訊 I 面向初級(jí)工程師的 PCB 設(shè)計(jì)規(guī)范

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計(jì)“好搭子”來(lái)了!

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計(jì)“好搭子”來(lái)了!

從“設(shè)計(jì)到生產(chǎn)”的蛻變:華秋DFM如何讓工程師們“輕松上陣”?

作為PCB設(shè)計(jì)工程師,晶振的知識(shí)你都搞明白了嗎?

作為PCB設(shè)計(jì)工程師,晶振的知識(shí)你都搞明白了嗎?

評(píng)論