摘 要: 傳統的8PSK頻偏估計方法通常需要上百個符號完成,其優點在于能夠實現較大的載波頻偏補償,但是同步時間較長,不適用于短時突發通信條件下的快速載波頻偏估計。特別是在低信噪比下,更是很難達到快速鎖定的目的。基于在低信噪比條件下,數據包長度有限的短時突發通信,提出了一種8PSK快速載波同步的方法,并在FPGA上得到實現。經驗證,該方法實現簡潔有效,硬件開銷小,同步時間短。

0 引言

8PSK在衛星通信、數據鏈電臺等領域有廣泛應用。而未預差分編碼的8PSK只適合相干解調,接收機通常需要對發送載波的初始相位以及收發端之間的載波頻偏進行估計,然后通過跟蹤環路將殘余頻偏補償回去,從而達到正確解調的目的。傳統方法的初相和頻偏估計以及跟蹤過程往往通過上百個符號完成,其優點在于能夠對較大的載波頻偏進行補償,但是跟蹤時間長,不適用于短包突發通信,而且在通常情況下硬件開銷較大[1-2]。

突發數據包結構中(如圖1所示),每包中用于信號捕獲以及載波初值估計與跟蹤的引導數據長度一般只有幾十個符號。每個突發數據包都需要完成載波同步與跟蹤,且由于引導數據很短,需要快速完成同步。通過實際仿真發現,在低信噪比下快速同步極易出現載波失鎖或鎖相環帶入過調量而造成相位誤差,從而人為地增加了信號的相位噪聲。因此,在短包突發通信中,較難解決快速同步與信號跟蹤穩定的矛盾。

本文在數據包長度有限的突發通信[3]模式下,為了實現信號的快速捕獲、載波快速同步、載波平穩跟蹤以及在極低信噪比條件下正確解調,提出了一款8PSK的載波同步新方法。該方法設計簡潔,實現模塊化設計。下文分別從同步模型、同步新方法、MATLAB仿真比較和FPGA實現對其做說明。

1 載波同步模型

用于載波頻偏估計的8PSK[4]接收信號可以表示為:

式中,k=0,1,2,。。.,7;Ak為幅度;fc為待估計的載波頻率偏差;missing image file為調制相位;θ0為未知的載波相位;wk為加性高斯白噪聲。

基于傳統載波同步的接收端[5]模型如圖2所示。

在低信噪比時,由于I、Q[6]兩路相位噪聲較大,使用單一的載波同步環路會導致在有限的引導數據長度下鎖定慢,或載波環路系數調整后即便能較為快速鎖定,也會極易再次失鎖。既要載波同步鎖定時間不能過慢,又不能在鎖定后過調而導致失鎖,僅使用一個載波同步環路無法滿足數據鏈突發通信包的要求。

2 載波同步新方法

根據數據鏈突發通信包的特點,本文提出一種分時段控制載波同步方法,如圖3所示。其基本思想是:分時段給出控制信號,首先選擇載波快速同步方法,實現較大頻偏的快速糾偏;其次,選擇載波慢同步[7]方法,利用FIFO中存儲的引導數據和快速同步方法中獲得的初步頻偏預估計值,完成載波慢同步,實現載波的精確同步;最后,通過載波跟蹤方法,實現載波的平穩跟蹤,以達到在低信噪比條件下不易因相位噪聲過大引起過調而同步失鎖,同時也減小環路[8]濾波的鎖定抖動造成不必要的誤碼。

2.1 載波快同步方法

下變頻后得到I、Q兩路基帶信號,相乘后,得到鑒相信號為:

將此鑒相信號送入快同步環路進行同步鎖定,快同步環路采用常規的Costas環設計,得到的頻偏累加值產生頻率控制字控制NCO,實現頻率補償,利用經過初步頻率補償后的本地載波,完成本地接收信號的下變頻。載波快同步會很快實現較大頻偏的糾偏,在低信噪比的條件下,為了得到更加準確的頻偏估計值,往往需要通過計算快速鎖定以后較長平穩時間內的平均值才能提供給載波慢同步使用,否則會造成慢同步的環路壓力過大,不利于實現低信噪比下的可靠同步。鑒于此,在載波同步快速鎖定后的平穩過程中,對快速同步8個符號長度的頻率控制字求平均(總共1 024點),得到初步頻偏預估計值missing image file。

2.2 載波慢同步方法

當信號完成初步的載波同步后,頻偏已糾偏到極小的范圍內,但是依然沒有實現載波同步,特別是在極低信噪比的條件下,載波快同步往往更加不準確,且載波快同步的方法并不適用于8PSK信號[9],因此需要通過載波的慢同步繼續完成載波的準確同步。

信號表示為極坐標形式:

對8PSK信號做M-th非線性變換消除調制,信號變為單頻信號:

上式表示的信號處理方式實際上是對相位誤差進行歸一化處理。

在實現過程中,下變頻I、Q兩路信號通過CORDIC算法計算出當前相位值φ(k),將φ(k)進行式(4)處理后,得到歸一化的相位誤差值,將該值送入慢同步環路進行同步鎖定,慢同步環路采用常規的Costas環設計,得到的頻偏累加值產生頻率控制字,并結合初步頻偏預估計值missing image file,實現對NCO的控制,達到慢速鎖定的目的。

短包突發通信要求載波的快速鎖定,載波慢同步環路濾波器系數設置時,環路收斂的速度比載波快同步快一倍,能夠實現較快鎖定,但是同時造成的相位收斂后相位的震蕩要稍微劇烈一些;與此同時,載波慢同步算法的殘余頻偏調整速率約為載波快同步算法的1/8,所以最終的效果是,載波慢同步相位的收斂速度要比載波快同步慢,而且收斂后相位的震蕩更加劇烈,因此需要載波跟蹤同步過程。

2.3 載波跟蹤同步方法

在載波慢同步過程中,載波頻偏值已經被完全消除掉,但是由于信號處于低信噪比的條件時,噪聲對相位和環路濾波器的影響較大,如果之后不進行載波跟蹤,極易造成信號的再次失鎖,因此最后進入到載波跟蹤狀態,保證整包信號都能夠實現在低信噪比的條件下鎖定。

載波跟蹤同步方法與載波慢同步的方法一致,不同之處是,載波跟蹤狀態下不再需要過快調整相位收斂,僅僅需要慢速跟蹤即可,因此,需要調整環路濾波器的系數,使得載波跟蹤過程中相位的擺動變小,減小對信號本身造成的影響。該處理在信噪比極低的情況下可盡可能地提高碼元同步的準確度,即改善整個系統的誤碼率。

通過上述3個步驟的處理,能夠實現低信噪比下8PSK的快速載波同步,從而實現短包突發通信的實時接收。

3 仿真結果

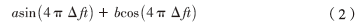

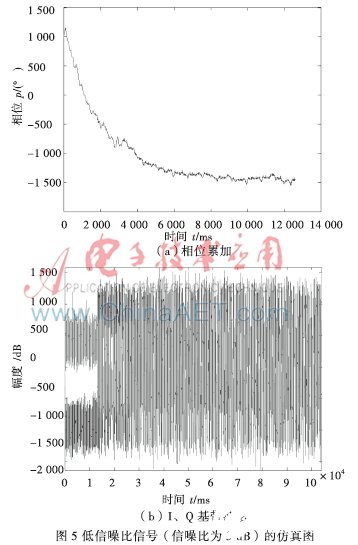

對產生1 kHz頻偏的8PSK調制信號進行Matlab載波同步仿真。分別對理想信號和低信噪比信號(信噪比為5 dB)進行仿真,仿真結果如圖4、圖5所示。

仿真驗證可得,在低信噪比條件下8PSK信號能實現快速同步及平穩跟蹤。

4 載波同步FPGA實現

本方法采用以XC5VSX95T為核心的FPGA硬件系統[10]實現。模數芯片選用AD公司的AD9246BCPZ芯片,14位精度。研究和實驗表明,系統運行良好。

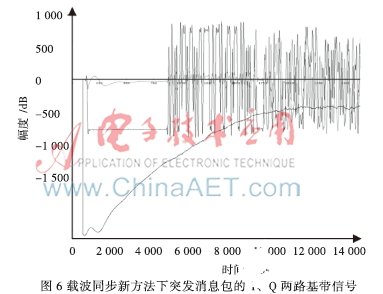

設定信號載波中心頻率為24 MHz,采樣速率為 32 MHz,短包突發通信的一包信號長度為400個符號,鎖定后I、Q兩路基帶信號和調整值如圖6所示。與圖4比較,FPGA實現的結果與仿真結果一致。

5 結論

通過對該方法的仿真及硬件實現,并將該方法應用于實際工程中,充分驗證了該載波同步新方法在低信噪比下收斂速度快、硬件資源耗用較少。

參考文獻

[1] 李利,羅偉雄。軟件接收機中DSB-SC信號載波同步的一種算法[J]。 電訊技術, 2002, 42(1): 143-150.

[2] 盧屹,張新軍,張嘉俊,等。數字鎖相環的參數設計及其應用[J]。 通信技術, 2001, 23(9):233-238.

[3] 彭岑,趙民建,鄭雅敏.TCM-8PSK短包高速跳頻接收機的快速載波同步[J]。 浙江大學學報(工學版), 2010,44(4):434-441.

[4] 朱彤。一種新的8DPSK調制解調方案[J]。 南京郵電學院學報, 1997,10(4):237-243.

[5] 付文君,王栓榮,呂孌,等。數字中頻采樣接收機的設計[C]。 中國空間科學學會空間探測專業委員會第十七次學術會議,2004. (下轉第63頁)

(上接第60頁)

[6] 張雙雄,周俊。 一種適用于寬帶數據鏈的TCM編碼新方法[J]。 電訊技術, 2011, 51(9): 356-362.

[7] 王靜。 8PSK+TCM編碼調制解調技術[D]。 南京:南京理工大學,2012.

[8] 蘇偉,杜志秀。 8PSK-TCM在數據中繼衛星通信信道上的應用研究[J]。 指揮技術學院學報, 1999, 10(4): 15-18.

[9] 朱彤。 一種新的8DPSK調制解調方案[J]。 南京郵電學院學報, 1997, 17(4): 49-53.

[10] 李濱滔,李春泉,戈志華。 基于FPGA的網格編碼的設計與實現[J]。 科技廣場, 2007, 18(3):144-151.

編輯:jq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636374 -

衛星通信

+關注

關注

12文章

833瀏覽量

40188 -

載波

+關注

關注

2文章

123瀏覽量

29195

發布評論請先 登錄

基于載波優化的云臺馬達驅動板控制策略

XZ2614高頻、同步、整流、降壓、開關模式的轉換器提供了一種非常緊湊的解決方案

瑞盟新品推薦MS51224 /16位、雙通道、低延時、同步采樣SAR ADC

空載與帶載測量信噪比的區別

解決效率 電壓尖峰問題!薩瑞微推出“低內阻+低Crss;Coss”同步優化方案

提高信噪比的操作

如何使用FPGA實現SRIO通信協議

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

AMD FPGA異步模式與同步模式的對比

如何基于Altera Agilex 7 SoC FPGA實現高精度時間同步

寬調速范圍低轉矩脈動的一種新型內置式永磁同步電機的設計與分析

基于FPGA的DVP接口實現

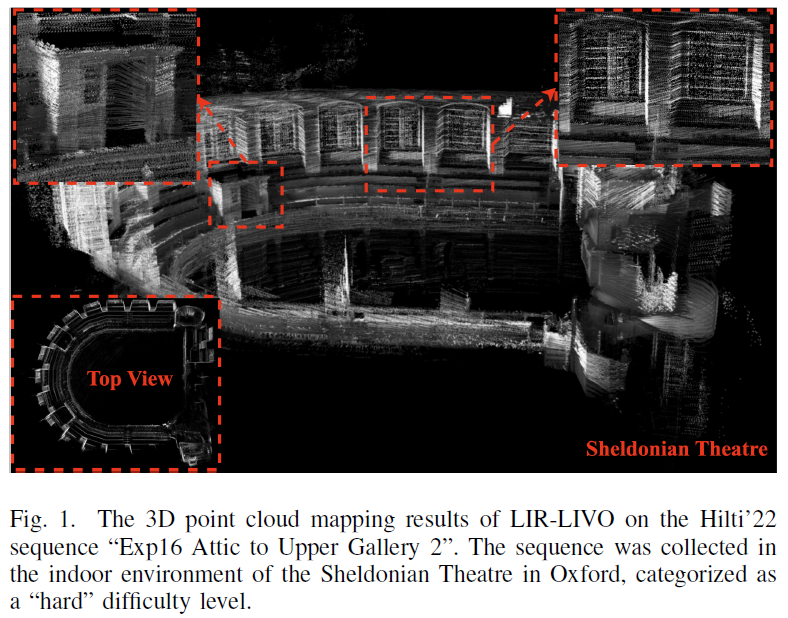

一種新型激光雷達慣性視覺里程計系統介紹

普源MSO8000示波器8通道同步采樣實現原理揭秘

基于一種低信噪比下8PSK的快速載波同步及FPGA實現

基于一種低信噪比下8PSK的快速載波同步及FPGA實現

評論