《 簡單狀態機 》設計

設計背景:

狀態機是描述各種復雜時序的時序行為,是使用 HDL 進行數學邏輯設計中非常重要的方法之一,狀態機分為摩爾機和米粒機,當輸出只和狀態有關系的話稱為摩爾機,當輸出不僅和狀態有關系也和輸入信號有關系的時候稱為米粒機,米粒機和摩爾機的電路原型我就不在這里給大家介紹了。

狀態機是由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設計的狀態進行狀態的轉移,是協調相關信號的動作,完成特定操作的控制中心。比如我們生活中遇到的問題,健康---感冒---健康,這個就是一個狀態的轉移圖,從健康狀態到感冒狀態在到健康狀態。

設計原理:

我認為對于我們初學者來說我們只要只要狀態機就是當這個狀態也就是當這個時鐘來的時候發生這件事情,當下各時鐘來的時候發生另一件事,也就是說發生這件事后,跳轉下一個時鐘發生另一件事情,兩個事情發生沒有關系。我們理解初學者理解這個就行了,不用理解高深的二段式,三段式。

我們會在下面的設計中用到簡單的狀態機讓大家明白簡單的狀態機。

我們的設計也是一個流水燈,我們的設計是在復位的時候讓 4 個等全熄滅,第一個上升沿點亮一個,第二個點亮下一個,依次類推。我們的寫法可以這樣想,當第一個狀態也就是一個上升沿點亮第一個燈,然后跳轉下一個狀態點亮第二個燈,第三個點亮下一個。。。。

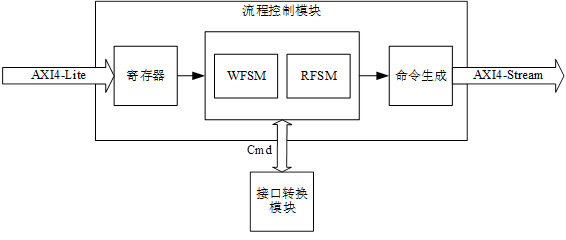

設計架構圖:

設計代碼:

仿真圖:

在仿真圖中我們可以看到,當 0 狀態的時候點亮第一個燈,當 1狀態點亮第二個燈,2 狀態第三個燈,3 狀態第四個燈,然后又到了0 狀態第一個燈,這樣就實現了流水。

責任編輯:lq6

-

寄存器

+關注

關注

31文章

5608瀏覽量

129987 -

HDL

+關注

關注

8文章

332瀏覽量

48977 -

狀態機

+關注

關注

2文章

499瀏覽量

29145

原文標題:至芯入門課程-簡單狀態機設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RDMA設計21:連接管理模塊設計

RDMA設計14:連接管理模塊設計

【團購】獨家全套珍藏!龍哥LabVIEW視覺深度學習實戰課程(11大系列課程,共5000+分鐘)

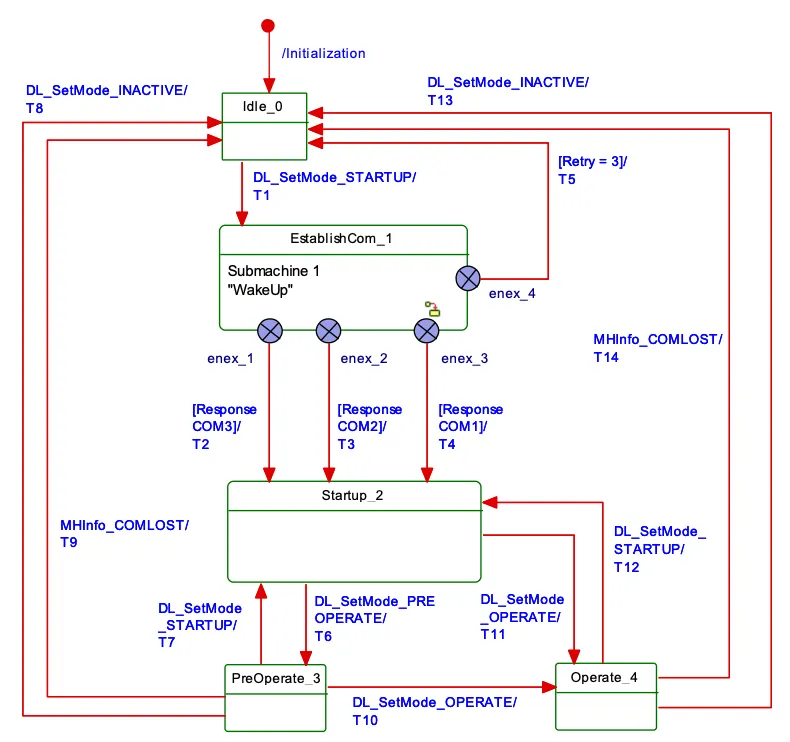

睿遠研究院丨IO-Link規范解讀(十一):ISDU狀態機與EVENT事件

什么是狀態機?

嵌入式開發為何經常用到狀態機架構

【課程升級】鴻蒙星閃WS63開發板新增《LVGL應用開發指南》課程,帶屏開發讓你的畢設項目更出彩!

睿遠研究院丨IO-Link規范解讀(六):主從站狀態機解析

入門課程之簡單狀態機設計流程

入門課程之簡單狀態機設計流程

評論