因為偶數分頻器過于簡單,所以我們從奇數分頻器開始說起8

01 奇數分頻器

假設我們要實現一個2N+1分頻的分頻器,就需要高電平占N+0.5個周期,低電平占N+0.5個周期,這樣進行處理的最小時間段就變成了0.5個周期,就不能通過clk的計數直接實現了。

然而,時鐘信號的上升沿和下降沿之間正好相差0.5個周期,利用這個就可以實現奇數分頻啦

第一步:分別使用原時鐘上升沿和下降沿產生兩個計數器(基于上升沿計數的cnt1和基于下降沿計數的cnt2),計數器在計數到2N時,計數器歸零重新從零開始計數,依次循環

第二步:cnt1計數到0和N時,clk1翻轉,從而得到占空比為N:2N+1的clk1;

第三步:cnt2計數到0和N時,clk2翻轉,從而得到占空比為N:2N+1的clk2;

第四步:clk1和clk2時鐘進行或操作后,即可得到輸出時鐘clk_out;

下面為3分頻的實現

module DIVCLK(

input wire clk,

input wire rst_n,

output wire clk_out

);

reg clk1;

reg clk2;

reg [1:0] cnt1;

reg [1:0] cnt2;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt1 <= 2'd0;

clk1 <= 1'b0;

end

else if (cnt1==2'd2) begin

cnt1 <= 2'd0;

end

else if ((cnt1==2'd0)||(cnt1==2'd1))begin

clk1 <= ~clk1;

cnt1=cnt1+2'd1;

end

else

cnt1=cnt1+2'd1;

end

always @(negedge clk or negedge rst_n) begin

if (!rst_n) begin

cnt2 <= 2'd0;

clk2 <= 1'b0;

end

else if (cnt2==2'd2) begin

cnt2 <= 2'd0;

end

else if ((cnt2==2'd0)||(cnt2==2'd1))begin

clk2 <= ~clk2;

cnt2=cnt2+2'd1;

end

else

cnt2=cnt2+2'd1;

end

assign clk_out=clk1|clk2;

endmodule

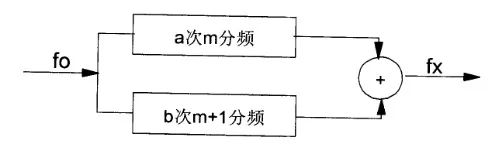

02 任意小數分頻

在實際設計中,可能會需要小數分頻的辦法的到時鐘,如在38.88M的SDH同步系統中,對應STM-1的開銷的提取,需要2.048M的時鐘,無法通過整數分頻得到,只能用小數分頻。

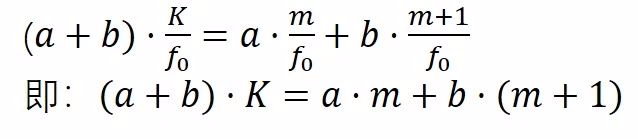

小數分頻原理如下:設輸入時鐘頻率f0,輸出頻率為fx,則

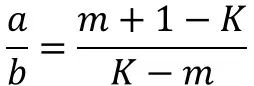

即m為整數部分,n為小數部分。為了實現K分頻,可以對f0進行a次m分頻和b次m+1分頻,則有

整理后得

由38.88M得到2.048M的時鐘,帶入上式可得到m=18,a=1,b=63,即對38.88M進行1次18分頻和63次19分頻后間插就得到2.048MHz啦

原文標題:關于分頻器~

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

分頻器

+關注

關注

43文章

537瀏覽量

53675

原文標題:關于分頻器~

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SN74LS292和SN74LS294可編程分頻器與數字定時器的技術解析

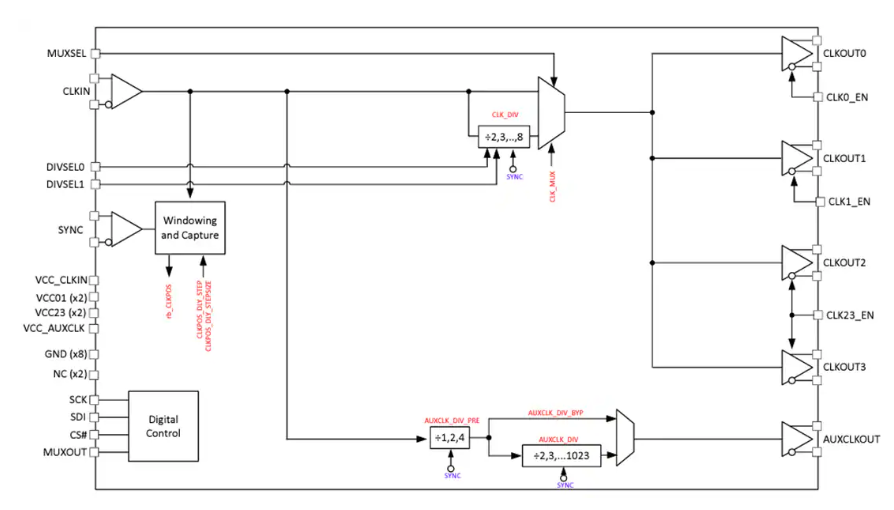

CDC5801A:低抖動時鐘倍頻器與分頻器的卓越之選

LMX1214:高性能低噪聲時鐘緩沖與分頻器的深度解析

?CDCLVD1213 1:4低附加抖動LVDS緩沖器帶分頻器 技術文檔摘要

德州儀器LMX1214射頻緩沖器與分頻器技術解析

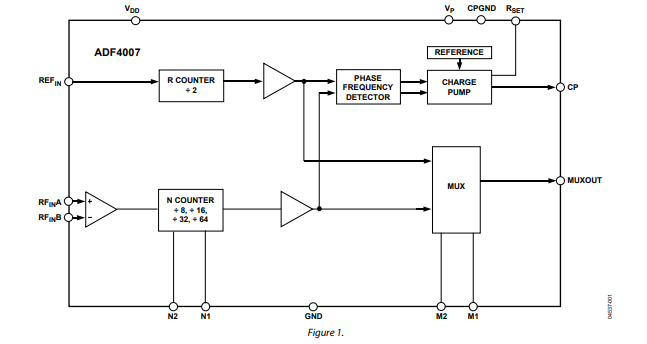

ADF4007高頻分頻器/PLL頻率合成器技術手冊

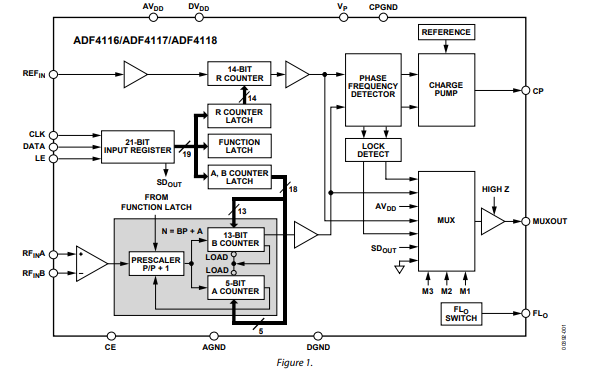

ADF4116/ADF4117/ADF4118單通道、整數N分頻550MHz PLL技術手冊

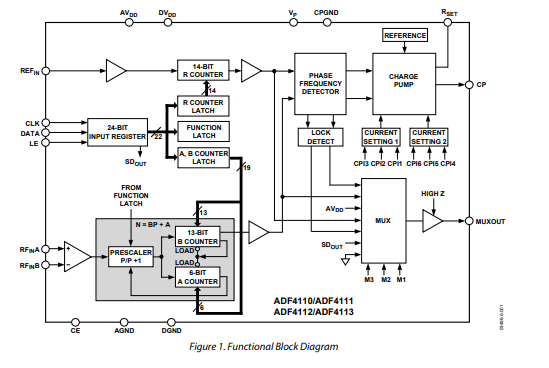

ADF4110/ADF4111/ADF4112/ADF4113單通道、整數N分頻、550 MHz PLL,內置可編程預分頻器和電荷泵技術手冊

ADF4206/ADF4208雙通道、整數N分頻1.1GHz/2.0 GHz PLL技術手冊

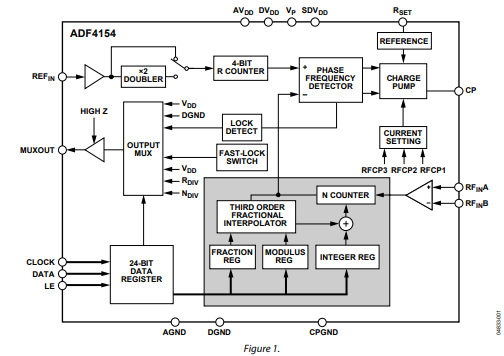

ADF4154小數N分頻頻率合成器技術手冊

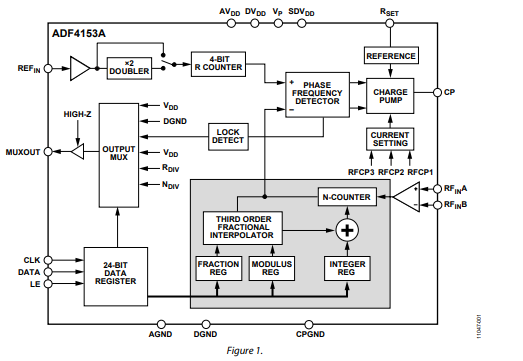

ADF4153A小數N分頻頻率合成器技術手冊

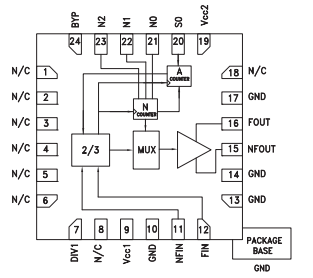

HMC705LP4/HMC705LP4E 6.5GHz可編程分頻器SMT技術手冊

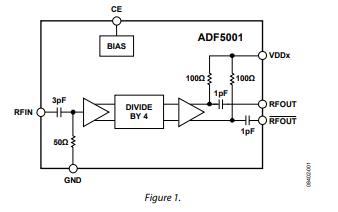

ADF5001 4GHz 至18GHz 4分頻預分頻器技術手冊

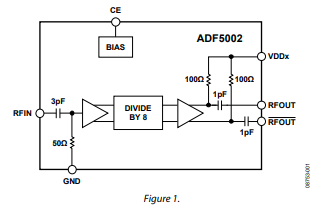

ADF5002 4GHz至18GHz 8分頻預分頻器技術手冊

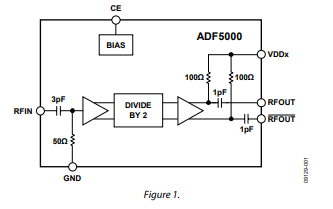

ADF5000 4GHz 至18GHz 2分頻預分頻器技術手冊

奇數分頻器的介紹和實現

奇數分頻器的介紹和實現

評論