JTAG是1980年代開發的用于解決電子板制造問題的IEEE標準(1149.1)。如今,它可以用作編程,調試和探測端口。但是首先,讓我們看看JTAG的最初用途,邊界測試。

邊界測試

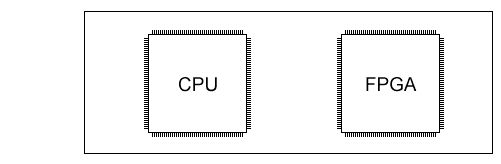

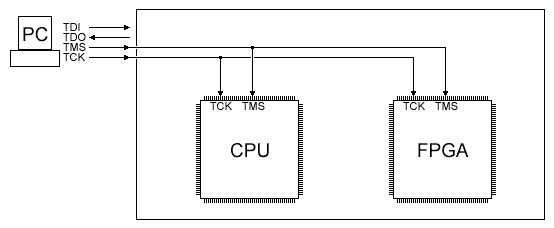

這是一個簡單的電子板(也稱為“印刷電路板”的“ PCB”),帶有兩個IC(“集成電路”),一個CPU和一個FPGA。典型的電路板可能具有更多的IC。

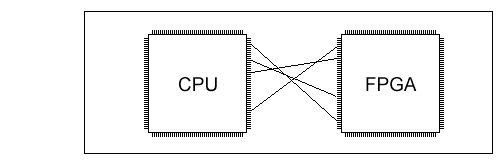

IC可以有很多引腳。因此,當然,IC通過大量連接(PCB traces)連接在一起。這里只顯示四個。但是可以輕松地在PCB上放置幾千個。

現在,如果您構建一千個板,每個板具有數千個連接,則不可避免地會有一些不良板。如何測試所有這些板?必須確保所有這些連接都正確。不能只手動測試所有這些連接。這樣就創建了JTAG。

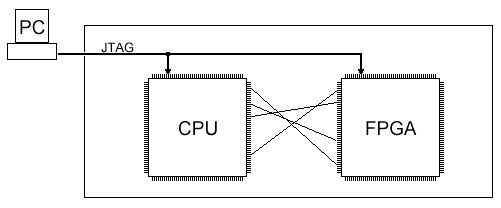

JTAG可以控制(or hijack)所有IC的引腳。在圖片上,也許JTAG將使所有CPU引腳輸出,以及所有FPGA引腳輸入。然后,通過從CPU引腳發送一些數據,并從FPGA引腳讀取值,JTAG可以確保電路板連接良好。

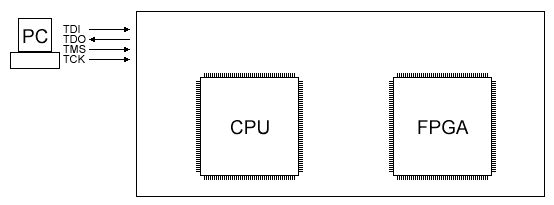

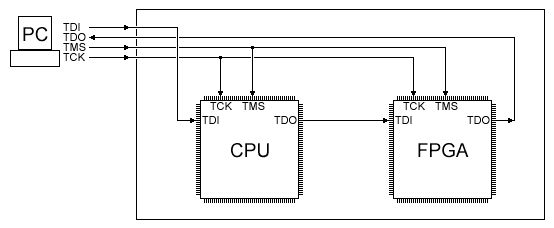

現在,JTAG實際上包含四個邏輯信號,分別為TDI,TDO,TMS和TCK。從PC的角度來看,這是三個輸出和一個輸入。

◇TCK:時鐘信號,為TAP的操作提供了一個獨立的、基本的時鐘信號。

◇TMS:模式選擇信號,用于控制TAP狀態機的轉換。

◇TDI:數據輸入信號。

◇TDO:數據輸出信號。

這四個信號需要以特定方式進行布線。首先,TMS和TCK與所有JTAG IC并聯。

然后將TDI和TDO并連接起來,形成一條鏈。用JTAG術語,您經常會聽到“ JTAG-chain”一詞的來歷。

如您所見,每個符合JTAG的IC都有四個用于JTAG的引腳(三個輸入和一個輸出)。名為TRST的第五個引腳是可選的(JTAG復位)。JTAG引腳通常是專用的(不共享用于其他目的)。

所有大型IC都使用通過JTAG進行的邊界測試-邊界測試是創建JTAG的最初原因。如今,JTAG的使用已得到擴展,以允許進行諸如配置FPGA之類的操作,然后在FPGA內核內部使用JTAG進行調試。

責任編輯:lq

-

JTAG

+關注

關注

6文章

415瀏覽量

74973 -

引腳

+關注

關注

16文章

2111瀏覽量

55694 -

電子板

+關注

關注

0文章

9瀏覽量

1847

原文標題:什么是JTAG?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】+可測試性設計章節閱讀與自己的一些感想

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

深入解析 SN54ABT8543 與 SN74ABT8543 掃描測試設備

SCANSTA101:低電壓IEEE 1149.1系統測試訪問主設備的深度剖析

深入解析 SCANSTA111:增強型掃描橋多分支可尋址 IEEE 1149.1(JTAG)端口芯片

探索SCANSTA112:多端口JTAG復用器的技術奧秘與應用

SN74LVT8980A-EP嵌入式測試總線控制器:JTAG測試的理想之選

十年測試工程師復盤:CP與FT的邊界究竟在哪?

探索SN54ABT8245和SN74ABT8245掃描測試設備:邊界掃描技術的卓越之選

單相繼電保護測試儀用途是什么?

測試計劃與測試策略的工程化邊界

FPGA的Jtag接口燒了,怎么辦?

看看JTAG的最初用途,邊界測試

看看JTAG的最初用途,邊界測試

評論