電子微組裝可靠性設計的挑戰,來自兩個方面:一是高密度組裝的失效與控制;二是微組裝可靠性的系統性設計。

一、高密度組裝的失效與控制

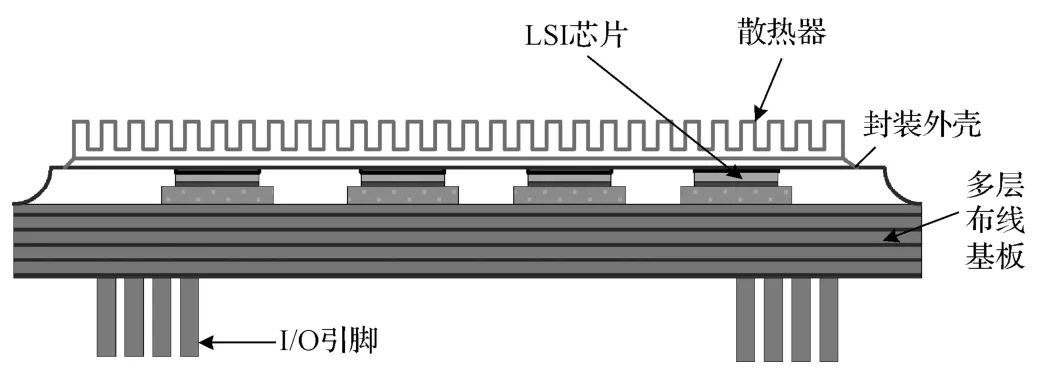

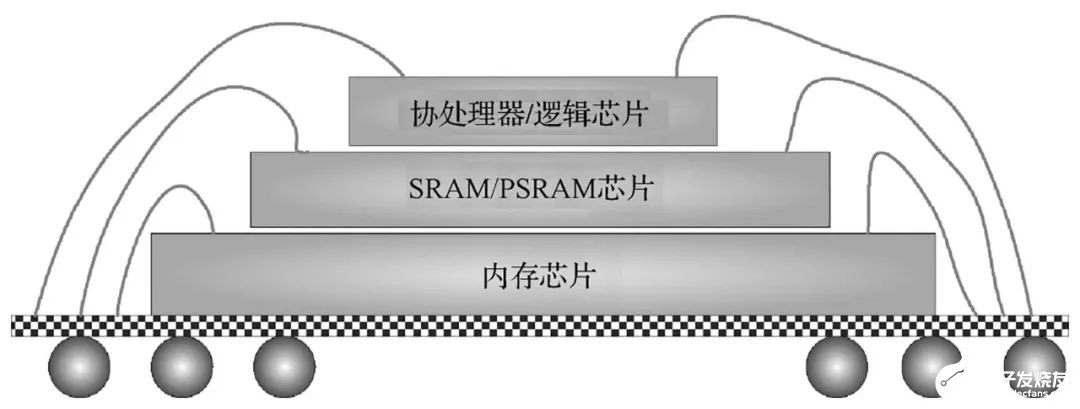

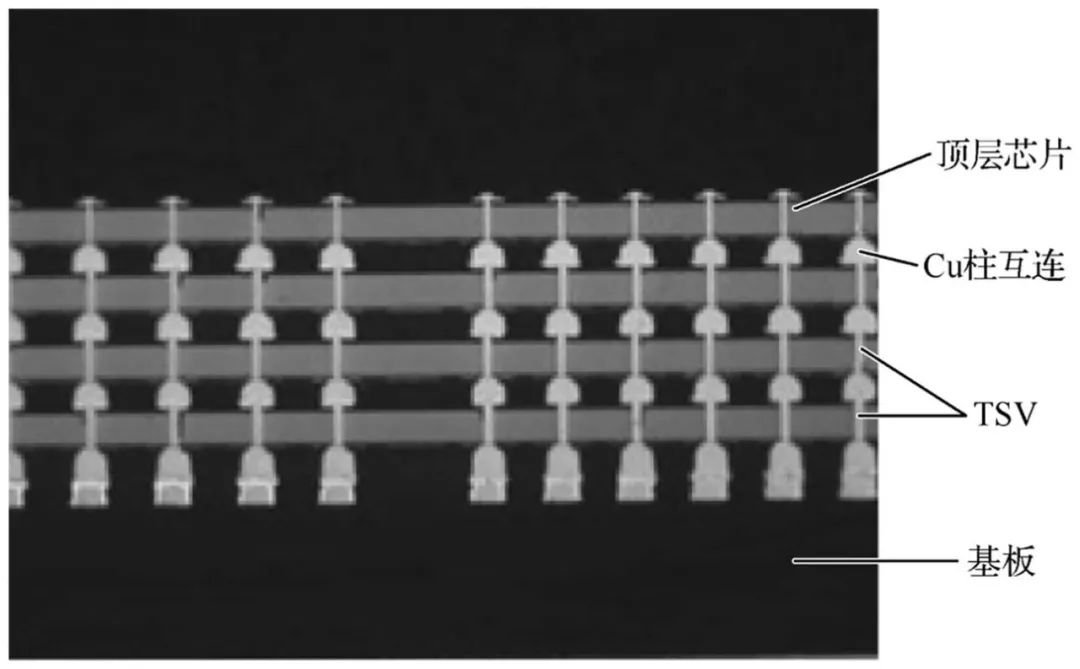

高密度組裝的代表性互連模式有兩類,一類是元器件高密度組裝,有兩種典型的芯片組裝方式,即芯片并列式組裝(2D)和3D-芯片堆疊組裝結構疊層式,如圖1和圖2所示;另一類是高密度微互連,例如,3D疊層芯片TSV硅通孔、高密度低拱形絲鍵合,如圖3和圖4所示。

圖1 芯片并列式組裝(2D)

圖2 3D-芯片堆疊組裝結構

圖3 3D疊層芯片TSV硅通孔

圖4 3D疊層芯片高密度低拱形絲鍵合

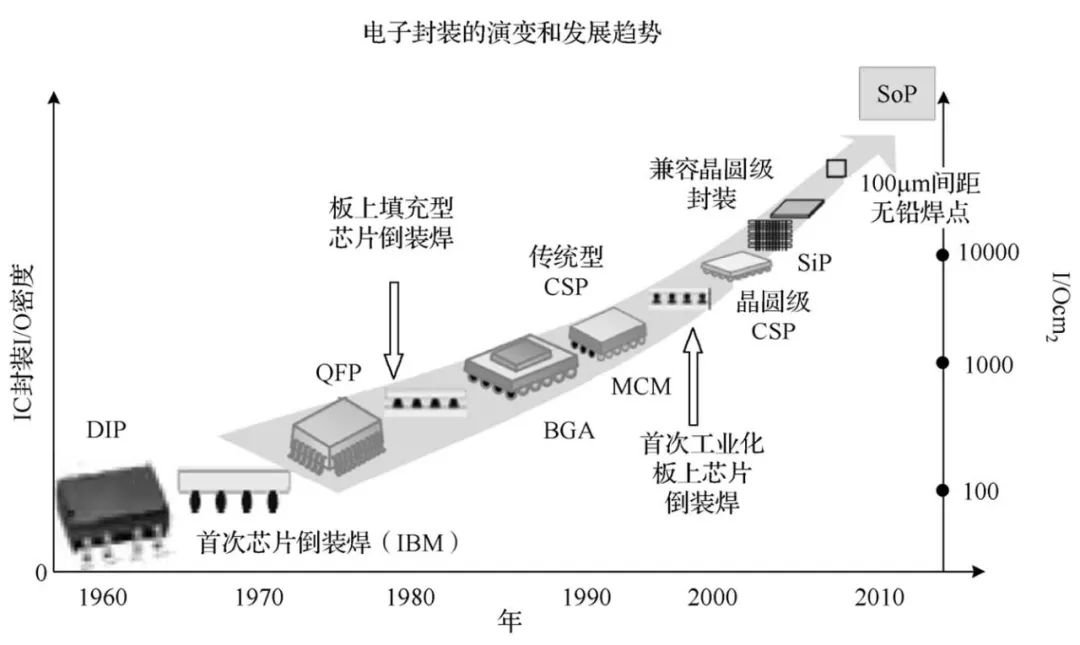

從電子微組裝的發展趨勢可以看出,微組裝技術的發展必然帶來產品的更高密度封裝,而高密度封裝的可靠性問題,主要是產品內部熱流密度增加導致的溫升、微互連間距減小導致的短路風險、封裝體內元器件電磁干擾及潛在傳播路徑等問題。

圖5 電子封裝50多年的演變和發展趨勢

1.2D和3D IC高密度組裝的熱問題

2D-IC或3D-IC的高密度組裝方式,面臨的嚴重問題是如何散熱,這一問題已成為限制高密度集成特別是三維集成技術發展的瓶頸。微組裝產品中的有源器件芯片,是微組裝產品的主要熱源,由于高密度組裝,產品熱功率密度(W/mm2)增大,芯片之間、芯片與元件之間熱耦合效應突出。這時,芯片PN結溫TJ或溝道溫度Tch,以及元件熱點溫度THS,不僅僅取決于器件自身功耗大小,還取決于鄰近元器件的功耗以及相互間的熱耦合效應,內裝元器件組裝密度越高,芯片間的熱耦合效應就越明顯,引起芯片額外的溫升就越高,使得元器件溫度余量減少、有機材料加快老化。

盡管針對高密度封裝穩態、瞬態熱管理問題,人們開展了大量研究,提出了各種熱分析方法和散熱設計方法。例如,2009年ITRS組裝封裝技術工作組,在SiP組裝封裝技術報告中,對于SiP疊層芯片熱設計和熱管理,提出了針對系統熱點和功耗控制的熱設計基本原則,在考慮最壞情況和典型使用條件下,建議將最大功耗芯片疊層在底部的主要散熱面,最小功率芯片疊層在頂部,并設計基板埋置熱沉和系統壓電散熱器,以保證頂部芯片熱點溫度控制和系統級散熱管理。但是,組裝密度不斷提升和產品體積不斷縮小的市場需求,不斷給更高封裝密度的熱設計帶來新的挑戰。

2.TSV高深寬比(h/d)的互連可靠性問題

TSV通孔技術是實現芯片3D疊層組裝的關鍵技術。作為多芯片層間互連的TSV通孔,由于有較高的深寬比,以及通孔工藝和結構特性,與基板通孔結構相比,TSV通孔結構面臨更嚴重的熱應力、機械應力帶來的可靠性問題。例如,銅填充的TSV在溫度變化應力作用下,銅硅熱膨脹失配可能導致TSV的硅基板開裂;TSV與倒裝芯片凸點互連的金屬間化合物(IMC)在溫變剪切應力作用下可能斷裂。

針對3D封裝中,TSV通孔的可靠性和失效問題,人們開展了大量研究。例如,對3D封裝TSV結構熱膨脹行為進行了研究,分析了Si/Cu結構的CTE失配結果,認為在溫度變化過程中,TSV鄰近Si的最大應力是張應力,但同時由于疊片結構中TSV通孔的存在,可以降低芯片分層的風險;對超薄芯片堆疊的3D集成組裝技術和失效問題進行了研究,認為芯片減薄過程的機械損傷給芯片疊層組裝帶來潛在問題,當芯片堆疊厚度和TSV數量增加時熱膨脹失配更為嚴重,溫變應力下頂層芯片互連點將面臨更嚴酷的可靠性問題,需要設計合適的TSV尺寸并優選材料,以提高溫變環境的適應性;對基于TSV的片上網絡芯片(3D NoC)可靠性問題的研究,認為3D NoC中TSV的主要失效問題,有TSV硅片翹曲、TSV層間垂直連接、CTE失配引起的熱應力問題;對三維芯片堆疊高深寬比(h/d)的Cu通孔互連研究,認為Cu電鍍工藝優化是獲得良好導電通道的關鍵;對基于TSV的2.5D和3D堆疊IC模塊的測試研究,提出了包含TSV通孔信息的測試流程、測試內容、測試端口的解決方案。

標準JEP 158(2009)3DChip Stack with Through-Silicon Vias(TSVS): Identifying,Evaluating and Understanding Reliability Interactions,針對3D芯片堆疊的TSV硅通孔可靠性問題描述,歸納起來有以下觀點:

● TSV硅片尺度因素、Cu與Si之間CTE差異因素,引起TSV通孔界面應力集中;

● 場效應管(FET)對應力敏感,FET電性能變化與其和TSV的距離有關,影響FET耗損;

● TSV硅(Si)片非常薄(《100μm),遠比傳統器件芯片薄,更易碎或開裂;

● 帶有TSV的芯片堆疊結構,內部高溫熱點問題突出;

● 薄型TSV硅片(《100μm),在溫循中易翹曲,可能導致與芯片互連的開路,或芯片堆疊工藝中使溶化的芯片倒裝凸點焊球在側面短路;

● TSV通孔側壁的硅氧化絕緣層,可能存在缺陷,導致Cu通路與硅片存在潛在漏電通路。

從產品層面來看,為提升TSV互連的可靠性,人們關注的熱點問題仍是滿足可靠性要求的TSV尺寸、材料的設計,目前商業化SiP產品的TSV解決方案,設計了針對2.5D和3D封裝的TSV結構和線上/線下測試方法(MEOL)。不過,盡管TSV技術在高密度集成方面具有絕對優勢,但TSV技術的高成本和可靠性潛在問題,仍是目前其拓展應用過程中最具挑戰的問題。

3.電子微組裝其他失效問題

電子微組裝的其他失效問題,還包括絲鍵合界面退化、芯片黏結強度退化、黏結膠老化等互連問題,內裝元器件高密度組裝和布線布局帶來的電磁干擾和潛在傳播路徑問題,以及封裝蓋板開裂、玻璃絕緣子泄漏、水汽滲入等封裝問題。

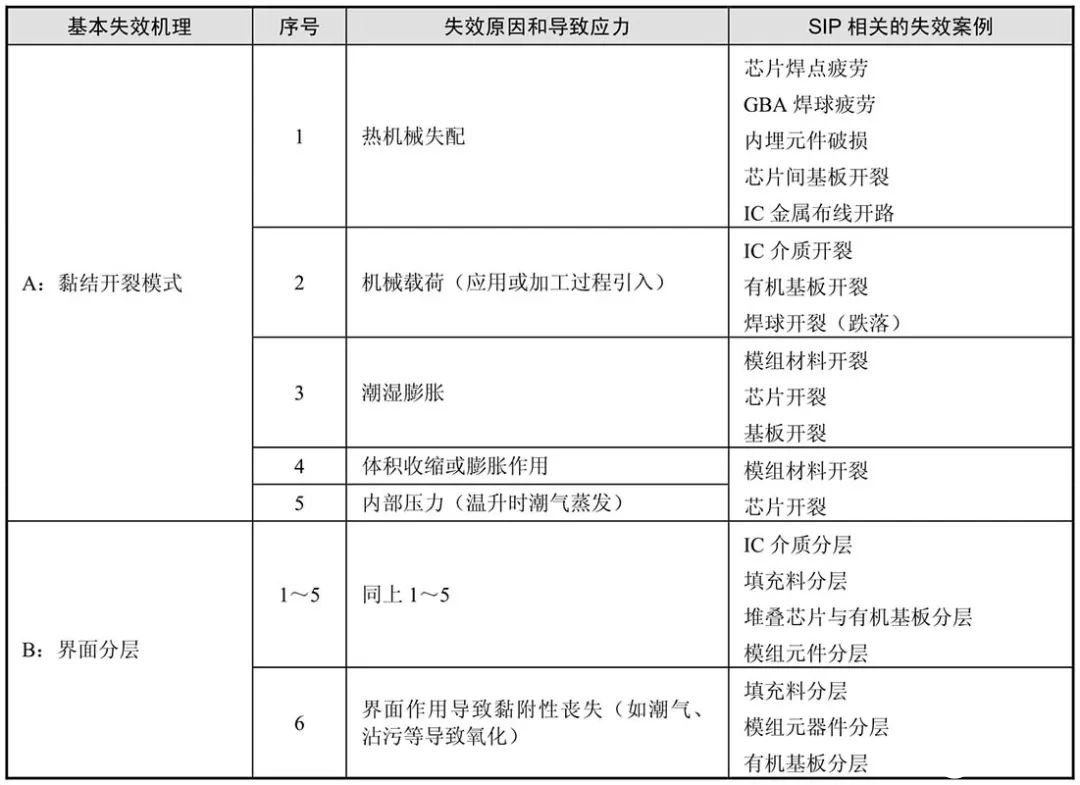

需要強調的是,微組裝失效模式和失效機理,與其承受的載荷應力類型及應力大小直接相關,系統性梳理這些失效模式、失效機理及相關載荷應力,形成失效模式機理庫,是微組裝可靠性設計的重要基礎支撐。ITRS組裝封裝技術工作組,在2009年的報告中,對系統級封裝(SiP)的4類典型失效機理、相關失效的應力和失效部位進行了歸納和分類。SiP失效機理分類及失效原因見表1。

表1 SiP失效機理分類及失效原因

二、微組裝可靠性的系統性設計

針對微組裝可靠性要求的系統性設計,關鍵要解決三方面問題:針對高密度組裝封裝失效的系統性控制設計、微組裝可靠性與性能及制造的協同設計、微組裝產品多機理失效的可靠性建模。

1.針對高密度組裝封裝失效的系統性控制設計

面對高密度組裝封裝帶來的各種失效問題,如何系統性分析和設計,全面有效地控制失效,是解決微組裝可靠性設計問題需要面臨的挑戰之一。

從大量的分立器件、HIC、MCM、微波組件、電真空器件失效分析案例和使用背景可以看出,產品封裝失效與其使用環境或直接載荷應力有關。例如,氣密封裝HIC,內裝裸芯片鍵合盤(pad)鋁膜腐蝕導致內引線鍵合點開路失效,與HIC內部水汽含量、pad沾污、環境溫度有關,一旦pad表面達到三個水分子層厚度的水膜,表面腐蝕即發生,水汽含量、環境溫度、沾污,這三類應力是導致鋁pad失效的直接應力因素;再如,微波功率管,燒毀失效模式,與管子的溫度載荷應力和電載荷應力有關,基板與底座焊接空洞的出現是溫度過高的原因,輸出匹配電容擊穿是電載荷過應力的原因。通過應力類別及應力來源分析,可以有效發現設計或工藝控制中存在的問題。各類載荷應力下的典型微組裝失效模式如下。

● 溫度應力類失效:高溫導致的有機材料、內裝元器件退化,溫變導致的焊點疲勞等;

● 機械應力類失效:機械振動導致封裝蓋板疲勞開裂,機械沖擊導致內裝元器件黏結脫落等;

● 潮濕應力類失效:水汽引起的芯片腐蝕、外殼腐蝕、露點失效等;

● 電磁應力類失效:內裝元器件及導線之間的電磁干擾等;

● 鹽霧應力類失效:鹽霧導致外殼、引腳腐蝕和斷裂等;

● 輻射應力類失效:總劑量、單離子效應導致半導體器件失效等;

● 耦合應力類失效:溫變/振動致焊點低/高周加速疲勞,低電壓/溫度/濕度致電化學遷移等。

因此,以載荷應力類型為主線,對各類微組裝進行可靠性設計的方法,是貫穿可靠性物理思想、系統實施失效控制的一種設計思路,在方法層面,能夠覆蓋現有的和今后新型的微組裝可靠性設計。從可靠性的基本概念來理解,如果可靠性定義中,用“可靠度”來度量微組裝的可靠性,把“規定的條件和規定的時間”視為可靠性的應力約束條件,則從數學、物理的角度進一步解讀可靠性定義,可以認為可靠性在數學上強調產品完成規定功能的概率即可靠度R(t),在物理上強調產品達到預期可靠度的應力約束條件[Fr(i,j)](m+1)×n。所以,以載荷應力為主線的可靠性設計思想和方法,具有更強的基礎性、系統性和清晰的物理意義,強化了基于失效物理(PoF)的可靠性設計理念,這也正是本書的核心思想。但是,基于失效物理并以載荷應力為主線的可靠性設計方法,難點是載荷應力分析和量化提取,不僅要解決一般環境單一應力下的可靠性設計,還要面對復雜環境多應力耦合下的可靠性設計,這也是目前微組裝可靠性技術領域關注的熱點問題。

2.微組裝可靠性與性能及制造的協同設計

針對微組裝失效控制實施的可靠性設計,前提是不影響產品既定的設計性能,同時適應現有的制造工藝能力,所以考慮微組裝可靠性與性能及制造之間的協同設計,是系統性解決微組裝可靠性設計所面臨的挑戰之二。

微組裝的這種協同設計,實際上是產品設計過程中的可靠性與性能和制造能力之間的權衡。在協同設計中,應綜合考慮產品的可靠性、電性能、熱性能、機械性能、防潮性、抗電磁干擾性能、抗輻照性能和可測試性等要求,特別是熱性能、機械性能,既要考慮高密度組裝帶來的應力耦合問題,還要考慮微組裝結構和材料隨時間的退化問題;既要考慮短期工作期間的熱、機械極限性能,也要考慮長期工作期間與熱、機械應力相關的可靠性問題;既要考慮制造工藝技術能力,也要考慮制造工藝技術的穩定性和離散性問題。可以通過可靠性設計指標的分解,綜合考慮各類性能之間的協同設計,量化制訂設計指標;通過容差分析和從產品結構到制造工藝的健壯設計,解決參數漂移和性能退化帶來的產品可靠性問題。

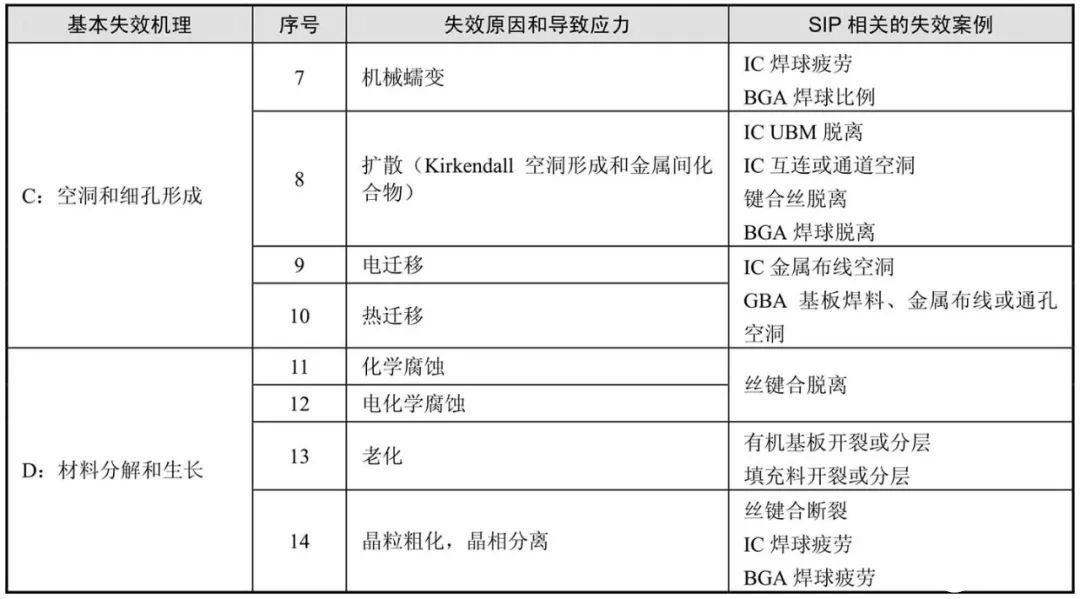

例如,ITRS組裝封裝技術工作組,在2009年的SiP組裝封裝技術報告中,分析了可靠性設計對SiP的影響,提出了針對SiP的有效協同設計概念,認為應該考慮物理尺寸、熱問題、機械問題、電氣設計和可靠性問題之間的相互影響,通過各種性能要求與可靠性要求之間的權衡,實現SiP可靠性與性能之間的協同設計,比如在進行高密度布線間距設計時,需要在布線間距和沾污橋連短路風險之間進行權衡;需要同時在多個方面評估SiP可靠性,以獲得最佳的協同設計,比如鍵合完整性、電遷移、潛在失效部位、板級可靠性、溫度循環適應性、基板彎曲、熱阻抗、元器件可靠性等,SiP協同設計程序,如圖6所示。同時,該報告還針對SiP的芯片-封裝-系統協同設計需求,重點從三個方面分析了SiP協同設計所面臨的挑戰:

● 芯片-封裝-系統的電氣模擬和設計挑戰:高密度布線耦合問題,EMC問題,3D鍵合絲問題;

● 芯片-封裝-系統的熱模擬和設計挑戰:80%~90%的熱量傳導至PCB,堆疊封裝熱問題突出;

● 芯片-封裝-系統的機械/應力模擬和設計挑戰:板級彎曲、界面應力模擬,分層、開裂問題。

圖6 SiP協同設計程序

3.微組裝多機理失效的可靠性建模

可靠性模型的作用是評估產品的可靠性,包括失效率、壽命或可靠度的評估,可采用數理統計方法建模,也可采用基于失效物理的壽命-應力方法建模,通過可靠性模型的分析計算,可以評估微組裝產品可靠性設計是否達到預期設計指標。微組裝產品可靠性建模,考慮兩個階段:隨機失效階段的失效率模型、耗損失效階段的可靠壽命模型,前者針對相互獨立的隨機失效事件,后者針對相互獨立和相互關聯的退化性事件。

微組裝產品在電路功能上沒有考慮冗余設計,所以隨機失效階段的失效率建模,無須考慮可靠性并聯模型,只需要考慮串聯模型;耗損失效階段的壽命建模,重點考慮多個退化機理對產品耗損壽命的影響,采用多機理競爭失效模式判定產品的失效時間。分析多機理退化參量的相關性及其可靠性建模問題,是系統性解決微組裝可靠性設計所面臨的挑戰之一。

1)隨機失效階段的失效率模型

對于微組裝產品在隨機失效階段的可靠性建模,采用數理統計方法,雖然這一階段的可靠性模型是最簡單和最保守的串聯模型,但各串聯單元的應力響應提取是建模后可靠性評價的難點。

在隨機失效階段,產品可能發生各種隨機性失效,由于這些失效是受到隨機質量因素或外界過應力沖擊所導致的,對于微組裝產品,隨機失效階段的各種隨機失效模式相互獨立,產品可靠性模型采用串聯模型,其中微組裝互連結構可以作為獨立的串聯單元考慮。

因為,內裝元器件的高密度集成,元器件之間的微組裝互連和多層布線基板發生隨機失效的問題更加突出;此外,從微組裝可靠性設計分析的需要,單獨考慮微組裝互連對失效率的貢獻,便于設計分析和問題的剝離,則,微組裝產品失效率λ∑是內裝元器件失效率λi與微組裝失效率λj之和。

2)耗損失效階段的可靠壽命模型

對于產品在耗損失效階段的可靠性建模,用失效物理和可靠性統計的方法,建立基于多機理或多模式競爭失效的產品壽命模型,并考慮多機理相互獨立或相互關聯的退化過程。

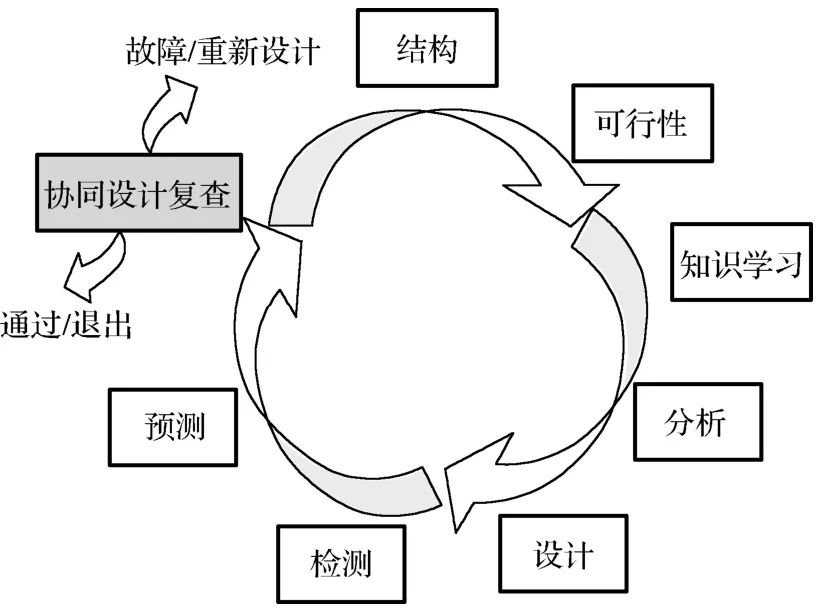

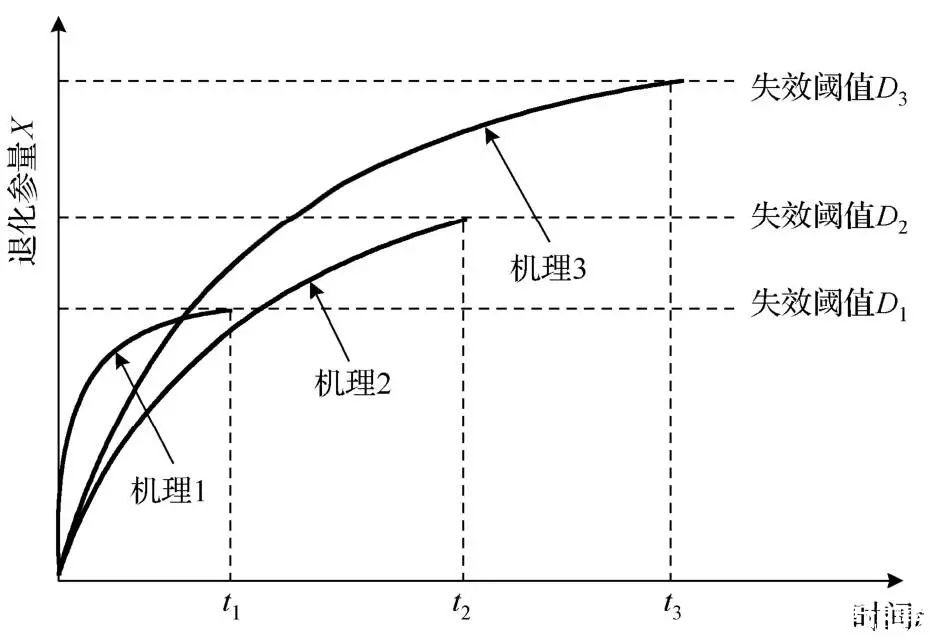

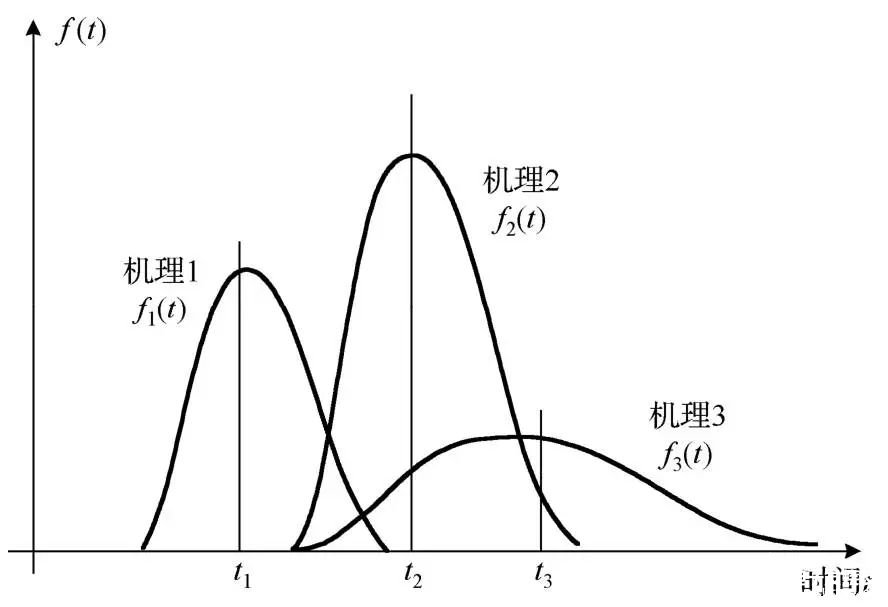

在耗損失效階段,產品耗損壽命終了的原因是性能退化,產品性能退化的發生,往往伴隨著多個退化機理或多個退化通道(退化模式),多個機理可以發生在某個互連點上,如元器件焊點,亦可以發生在電路中不同的元器件上,產品最終失效是不同退化機理之間或不同退化模式之間的競爭結果,三個退化機理競爭失效示意圖如圖7所示,產品退化壽命決定于退化參量中最早達到失效閾值的退化機理,如果考慮每個退化機理的失效概率分布問題,產品退化壽命決定于壽命時間內累積失效概率(T

圖7 三個退化機理競爭失效示意圖

圖8 三個競爭失效機理的失效概率分布

(1)多個退化機理的相關性分析

產品中多個退化機理或退化模式之間的相關性與相互影響,決定了產品可靠壽命的評估結果,這種關聯性是由產品電路和結構設計特性、產品不同部位同類工藝和材料、高密度組裝多應力耦合因素以及退化物理過程的相互影響所引起的。采用協方差、相關系數分析方法,可以確定多個退化機理或退化模式間是否相關,以及相關的程度。若多個退化機理或退化模式不相關,則產品的可靠度由串聯系統決定;若多個退化機理或退化模式相關,則產品可靠度由相關機理的多維聯合概率密度計算獲得,其分析的難點在于如何利用失效物理方法或試驗統計方法,建立各相關退化機理的退化參量概率密度函數。

① 導致多機理相互關聯的因素

微組裝產品退化過程中,多個退化機理或退化模式之間,在退化進程中往往存在某種聯系,確定退化機理之間的相關性和導致這種相關性的因素,目的是準確評估產品的可靠性,有針對性地優化設計產品。

影響產品多個退化機理相互關聯的因素,包括電路設計、結構設計、工藝設計和使用環境應力等因素,其核心是退化過程帶來的應力變化和性能參數的相互影響。大量的失效分析案例和退化機理分析表明,這些退化機理之間的相關性,是一種典型的從屬退化關系。

從屬退化,是指產品中由于某個元器件退化而引發其他元器件的加速退化或減速退化,或者由產品中互連焊點的某種退化機理引發另一種退化機理加速或減速退化。在從屬退化因素的作用下,多個元器件或互連焊點的退化機理不再相互獨立。比如,功能模塊中,電路上某個器件性能退化,引起電路中另一個器件性能加速退化,它們之間存在因果關系的從屬關系。

② 基于協方差的相關性分析

協方差分析是建立在方差分析和回歸分析基礎上的一種統計分析方法,用于衡量兩個隨機變量的總體誤差。期望值分別為E(X)與E(Y)的兩個隨機變量X與Y的協方差Cov(X,Y)定義為:

Cov(X,Y)=E{[X-E(X)][Y-E(Y)]}

通過退化參量之間的協方差統計分析,可以確定多個退化機理或退化模式是否相關,以及相關性的強弱。無論是共因退化機理還是從屬退化機理,都可以在協方差中得到體現。

③ 基于相關系數的相關程度分析

相關系數是用于反映隨機變量之間相關性密切程度的統計指標,用于度量多個退化參量的相關程度,以及它們之間是正相關還是負相關,可以用相關系數來描述。通過相關系數分析,可以進一步明確產品退化機理之間的相互影響和作用效果,確定產品退化的本質因素。

(2)多個退化機理相互獨立的可靠壽命模型

產品在規定應力下,所有退化參量x1(t),x2(t),…,xn(t)之間均相對獨立,相應的退化機理亦相互獨立。

這時,產品的可靠性模型可以等效為多個退化參量組成的串聯系統,而產品的退化壽命是多個機理競爭的結果,以最早達到失效閾值的“短板機理”來表征產品的耗損壽命。

(3)多個退化機理相互關聯的可靠壽命模型。

產品在規定應力下,協方差元素所代表的退化參量之間存在關聯,退化機理亦相互關聯;若協方差矩陣的非對角線所有元素均不為0,則表示所有退化參量均存在關聯,退化機理亦關聯。

這時,產品的可靠性模型不能完全等效為多個退化參量組成的串聯系統,但產品的退化壽命仍是多個退化機理競爭的結果,以最早達到失效閾值的“短板機理”來表征產品的耗損壽命,產品此時的可靠度評估,需要通過建立多維隨機變量的聯合概率密度函數來獲得。

(4)多機理可靠壽命評估的難點問題

第一個問題是多個退化機理相互關聯的可靠性建模。上述介紹已經知道,對于多個退化機理,當多個退化參量不相關時,產品可靠性建模采用串聯模型;當多個退化機理相關時,如果相關性和退化參量的協方差可獲得,產品可靠性建模可以通過數理統計的協方差矩陣,得到產品的聯合概率密度分布函數[插圖],難點是要解決每個單一退化參量的概率密度分布函數[插圖];多個退化機理相關,但其相關性和相關程度未知,已知每個單退化量的邊緣密度分布時,產品可靠性建模可以采用Copula函數融合多退化量的邊緣密度分布[68],得到產品的聯合概率密度分布函數,同樣,難點是要建立每個單一退化參量的概率密度分布函數,并要考慮非線性退化帶來的影響。

通過串聯可靠度模型計算結果,以及多退化參量的聯合概率密度函數仿真結果表明,當忽略退化參量間的相關性時,得到的可靠度評估結果將比考慮相關性時得到的結果要小,或者說,假設退化參量具有獨立性,將會低估產品的可靠性。因此,如果多機理可靠性評估的目的是支撐產品的可靠性設計,采用串聯模型處理,不考慮多個退化參量之間的相關性,將得到一個比考慮相關性時更保守的可靠性設計方案,在產品可靠性設計時,亦可以按單機理退化控制來設計,其代價可能是犧牲一定的幾何空間、產品重量和成本。

第二個問題是多應力耦合的識別和提取。建立主要單一退化參量概率密度函數,是多機理微組裝產品可靠性建模的核心基礎,由于產品是通過微組裝技術實現其高密度集成的,當產品在復雜環境下工作時,各元器件之間、微組裝互連之間存在明顯的多應力耦合,使各退化機理應力水平發生變化,如何有效識別退化部位微觀區域的多應力耦合機制,量化提取耦合應力,對基于加速應力試驗的模型的建立和耗損壽命外推至關重要,也是難點。

責任編輯:gt

-

芯片

+關注

關注

463文章

54007瀏覽量

465953 -

元器件

+關注

關注

113文章

5004瀏覽量

99639 -

電磁干擾

+關注

關注

36文章

2482瀏覽量

107927

發布評論請先 登錄

嵌入式軟件單元測試必要性與專業工具重要性的系統性專業研究報告

電子產品EMC整改:助力從定位到優化的系統性解決方案

如何做好電子制造工廠的ESD防護—從設計到售后失效分析的全流程策略

電子微組裝的其他失效問題及系統性設計研究

電子微組裝的其他失效問題及系統性設計研究

評論