你知道如何借助Cyclone 10 GX ATX PLL refclk切換實施功能模擬嗎?嵌入式流轉換器實施ATX PLL重配置和通道重配置以及實施ATX PLL和通道再校準呢?想學啊?我(視頻)教你啊。

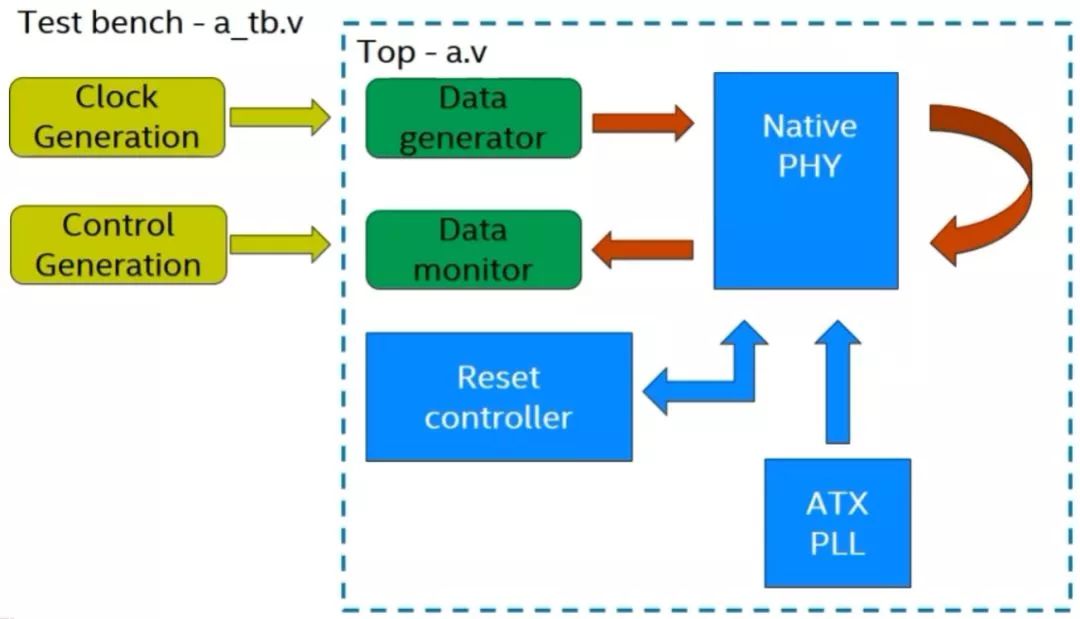

設計中的實例包括:Native PHY、TX PLL、重置控制器,數據和時鐘生成邏輯等。兩個refclk用于支持,無法通過TX本地除法器實現的兩個不同數據速率。125MHz用于2Gbps,150MHz用于1.2Gbps。

在模擬開始時,收發器以2Gbps的數據速率運行,然后使用ATX PLL refclk切換動態重配置,重新配置為1.2Gbps。ATX PLL refclk切換通過寄存器寫操作實施,接著使用嵌入式流轉換器進行ATX PLL重配置和再校準,然后就可以實施CDR refclk切換、通道重配置和再校準了。

溫馨提示

在上面的視頻中有實施ATX PLL refclk切換的高級步驟,詳情見視頻。

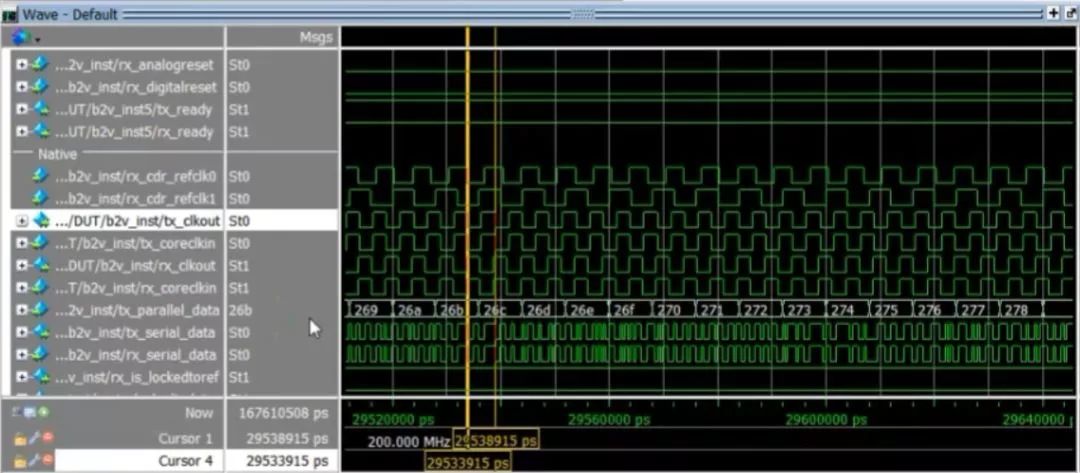

在最后的運行模擬示例中,我們可以看到增量數據從TX發送至RX。在啟動過程中,收發器通道的運行速率為2Gbps。PCS內核寬度為10比特時,tx_clkout頻率為200MHz。在實施ATX PLL refclk切換和通道重配置后,收發器通道的運行速率變為1.2Gbps。Tx_clkout頻率將變為120MHz。這顯示ATX PLL refclk切換和通道重配置已成功完成。

責任編輯:xj

原文標題:參考時鐘切換動態重配置不會玩兒?我教你啊

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

時鐘

+關注

關注

11文章

1971瀏覽量

134990 -

Cyclone

+關注

關注

0文章

55瀏覽量

30953

原文標題:?參考時鐘切換動態重配置不會玩兒?我教你啊

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

探索MAX4597單通道10Ω SPST模擬開關:特性、應用與設計要點

SysClk系統時鐘的切換

CW32 SysClk系統時鐘的應用場景與切換規則

如何驗證電能質量在線監測裝置硬件層實時監測冗余切換功能的有效性?

FX10、FX20 FlagA 時間延遲是固定的嘛?

PLL技術在FPGA中的動態調頻與展頻功能應用

【干貨分享】RP2040 + Cyclone 10 FPGA PCB 設計

PLL用法

模擬開關切換電流時遇到的問題

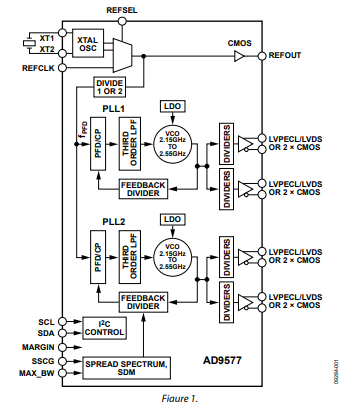

AD9577帶雙路PLL、擴頻和余量微調功能的時鐘發生器技術手冊

如何借助Cyclone 10 GX ATX PLL refclk切換實施功能模擬

如何借助Cyclone 10 GX ATX PLL refclk切換實施功能模擬

評論