如今幾乎所有數(shù)字元件背后的邏輯電路都依賴于兩種成對的晶體管– NMOS 和PMOS。相同的電壓信號會將其中一個晶體管打開,而將另一個關(guān)閉。將它們放在一起意味著只有發(fā)生些微變化時電流才會流通,進而大大降低了功耗。這些成對的晶體管已經(jīng)彼此櫛次鱗比在一起好幾十年,但是如果電路要繼續(xù)縮小,它們就必須靠得更近。 英特爾(Intel)在本周的IEEE 國際電子元件大會(IEEE International Electron Devices Meeting, IEDM)上展示全然不同的排列方式:把一對晶體管堆疊在另一對上面。該方案有效地將一個簡單的CMOS 電路所占面積減半,這意味著未來IC 集成電路芯片上的晶體管密度可能會增加一倍。 該方案首先使用了被廣泛認可的下一代晶體管結(jié)構(gòu),該結(jié)構(gòu)有不同的稱呼,包括納米片(Nanosheet)、納米帶(Nanoribbon)、納米線(Nanowire)或環(huán)繞式結(jié)構(gòu)(Gate- All-Around, GAA)元件。和當前晶體管主要部分是由垂直硅鰭片組成之常見做法不同的是,英特爾納米片的通道區(qū)是由多個相互堆疊之水平納米級薄片組成。

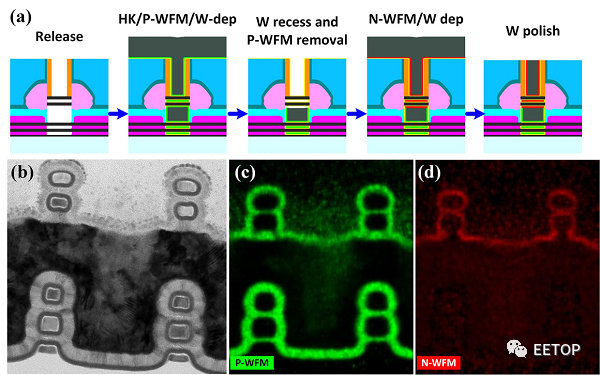

采用自我對準制程配方,修改制造步驟成為制程重點英特爾工程師使用這些元件來打造極簡的CMOS 邏輯電路,亦即所謂反向器(Inverter)。它需要兩個晶體管,兩個電源接線,一個輸入連線和一個輸出連線。即使晶體管也采取像當前并排的放置方式,但排列得非常緊湊。透過堆疊晶體管并調(diào)整互連,反向器面積得以減半。 英特爾用于打造堆疊式納米片的配方被稱為「自我對準」(Self-Aligned)制程,因為其實質(zhì)上可透過相同的步驟中構(gòu)建兩種元件。這很重要,因為多加第二步驟(比如,在個別的晶圓上構(gòu)建他們,然后再將晶圓接合在一起)可能會導(dǎo)致晶圓定位偏移,進而造成任何潛在電路的破壞。 該制程的核心重點是對納米片晶體管的制造步驟進行修改。它首先從重復(fù)的硅層和硅鍺層開始。然后將其蝕刻成一個又高又窄的鰭片,然后再將硅鍺蝕刻掉,留下一組懸浮的硅納米片。通常,所有的納米片都會形成單一的晶體管。但在此,最上面兩個納米片會連接到摻磷硅(Phosphorous-Doped Silicon)上,其目的為了形成一個NMOS 元件,而底部兩個納米片則連接到了摻硼硅鍺(boron- doped silicon germanium)上,以產(chǎn)生PMOS。

簡化整合流程,將應(yīng)變引進自家元件中這整個「整合流程」當然要復(fù)雜得多,但是英特爾研究人員一直在努力使其盡可能地簡單,英特爾資深研究員暨元件研究總監(jiān)Robert Chau 表示。「整合流程不能太過復(fù)雜,因為這將影響到以堆疊式CMOS 制造芯片的可行性。結(jié)果證明這是一個非常實用的流程,并取得了可觀的成果。」 他表示:「一旦掌握了這個訣竅,下一步就可以開始追求效能表現(xiàn)了。」這可能包括PMOS 元件的改進作業(yè),目前它們在驅(qū)動電流方面落后NMOS。Chau 進一步指出,該問題的答案可能是要在晶體管通道中引進「應(yīng)變」(Strain)。此一構(gòu)想是透過快速通過載流子(Charge Carrier,在這種情況下為電洞)的這種方式來扭曲硅晶體晶格。英特爾早在2002年就將應(yīng)變引進至自家元件中。

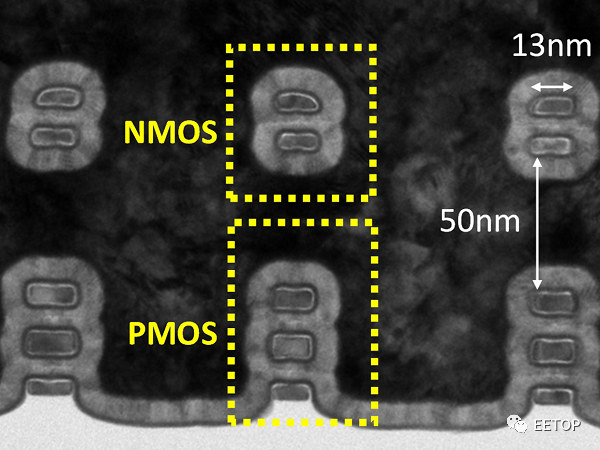

在IEDM 大會的另一項研究中,英特爾展示了一種能在納米帶晶體管中同時產(chǎn)生壓縮應(yīng)變(Compressive Strain)和拉伸應(yīng)變(Tensile Strain)的方法。 其他研究組織也正展開堆疊式納米片的設(shè)計研究,盡管有時將它們稱為互補式場效晶體管(Complementary FET, CFET)。比利時研究組織Imec 率先提出了CFET 概念,并于去年6 月的IEEE超大型集成電路技術(shù)研討會(VLSI Symposia)上發(fā)表了實作CFET 的研究報告。但是,Imec 元件并非完全由納米片晶體管制作而成。其底層反而是由鰭式場效晶體管(FinFET)組成,頂層則為單一納米片。中國臺灣研究人員曾發(fā)表一篇有關(guān)CFET實作的研究報告,該結(jié)構(gòu)上的PMOS 和NMOS 各有一片納米片。相比之下,英特爾的電路在3 納米之納米片PMOS 上面有一個2 納米之納米片NMOS,這更接近當堆疊有必要時元件該有的樣子。

原文標題:關(guān)注 | 讓芯片密度再翻翻,摩爾定律再延續(xù)!英特爾展示堆疊式納米片晶體管技術(shù)

文章出處:【微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責任編輯:haq

-

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466175 -

英特爾

+關(guān)注

關(guān)注

61文章

10301瀏覽量

180475 -

晶體管

+關(guān)注

關(guān)注

78文章

10396瀏覽量

147778

原文標題:關(guān)注 | 讓芯片密度再翻翻,摩爾定律再延續(xù)!英特爾展示堆疊式納米片晶體管技術(shù)

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

不同于HBM垂直堆疊,英特爾新型內(nèi)存ZAM技術(shù)采用交錯互連拓撲結(jié)構(gòu)

Analog Devices MAT02:低噪聲匹配雙單片晶體管的太空級之選

突破供電瓶頸,英特爾代工實現(xiàn)功率傳輸?shù)目绱H飛躍

智銳通科技亮相“英特爾技術(shù)創(chuàng)新與產(chǎn)業(yè)生態(tài)大會”,展示AI醫(yī)療內(nèi)窺解決方案

吉方工控亮相2025英特爾技術(shù)創(chuàng)新與產(chǎn)業(yè)生態(tài)大會

英特爾舉辦行業(yè)解決方案大會,共同打造機器人“芯”動脈

18A工藝大單!英特爾將代工微軟AI芯片Maia 2

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

英特爾銳炫Pro B系列,邊緣AI的“智能引擎”

英特爾先進封裝,新突破

LP395 系列 36V 功率晶體管數(shù)據(jù)手冊

英特爾持續(xù)推進核心制程和先進封裝技術(shù)創(chuàng)新,分享最新進展

英特爾展示堆疊式納米片晶體管技術(shù)

英特爾展示堆疊式納米片晶體管技術(shù)

評論