隨著信息化產業的不斷推動,數字信號傳輸的速度越來越快,頻率越來越高,傳統設計的PCB板已經不能滿足這種高頻電路的需要。信號的完整性傳輸研究成為越來越關鍵的重要核心技術。當電路信號的頻率增加到一定高度后,PCB中的導通孔PTH中無用的孔銅部分,其多余的鍍銅就相當于天線一樣,產生信號輻射對周圍的其他信號造成干擾,嚴重時將影響到線路系統的正常工作,Backdrill的作用就是將多余的鍍銅用背鉆的方式鉆掉,從而消除此類EMI問題。在降低成本的同時,滿足高頻、高速的性能。

背鉆其實就是一種特殊的控制鉆孔深度的鉆孔技術,在多層板的制作中,例如8層板的制作,我們需要將第1層連到第6層。通常首先鉆出通孔(一次鉆),然后鍍銅。這樣第1層直接連到第8層。實際我們只需要第1層連到第6層,第7到第8層由于沒有線路相連,像一個多余的鍍銅柱子。這個柱子在高頻高速電路設計中,會導致信號傳輸的反射、散射、延遲等,給信號帶來完整性方面的問題。所以將這個多余的柱子(業內叫STUB)從反面鉆掉(二次鉆)。因此叫背鉆。

鍍銅短線柱(STUB)如何影響高速信號?

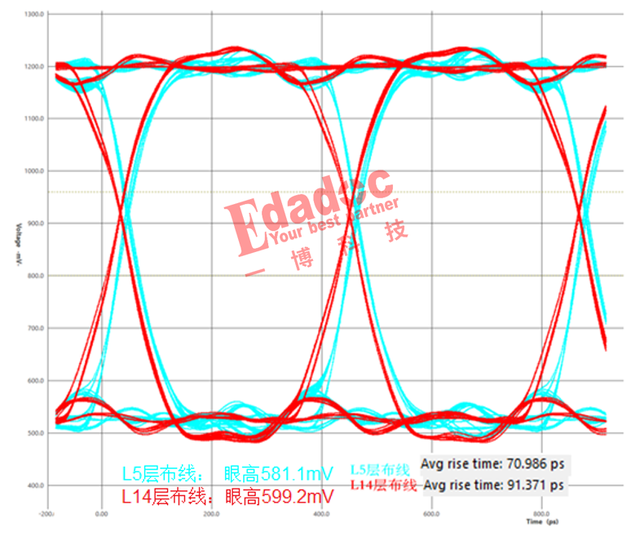

Stub即鍍銅短線柱,如上圖所示。沒有連接信號線的通孔鍍銅部分。下圖所示為兩種通孔結構的信號傳輸時電平轉換眼圖。左邊是具有完整的Stub鍍銅短線柱,右邊的是Stubless沒有鍍銅短線柱的情況。可以看出,通孔鍍銅短線柱在Pedestal Width這段區域其Pedestal Height消隱脈沖高度處于邏輯0到1和邏輯1到0轉換中的不確定狀態。這些不確定電平翻轉區域,使得數字接收更難以確定接收的信號到底是邏輯1還是邏輯0。不確定邏輯狀態的電平值與Stub鍍銅短線柱的等效阻抗成比例。較高的通孔短線柱阻抗使得邏輯電平更接近于期望的低電平0和高電平1。因此邏輯電平翻轉狀態更為明確。如右圖所示,類似于眼圖的眼睛張開的范圍更大。增加短線柱阻抗的有效方法是通過去除非功能焊盤來減小并聯電容。雖然這些技術有所幫助,但它們通常不足以將失真減少到可接受的水平。

不確定電平翻轉的區域寬度與短線柱的長度成比例。越短的短線柱Stub產生的不確定區域寬度越窄。減小不確定電平翻轉區域寬度的簡單方法是通過背鉆來減小通孔鍍銅柱的總長度。下圖所示為進行了適當背鉆的通孔PTH的眼圖。可以容易地看出,在背鉆操作之后剩余的鍍銅短線柱長度(在眼睛的左上角和左下角的不確定區域減小),類似于張開的眼睛范圍更大,確定電平轉換正常工作區間更大。

應當注意的是,采用構造技術(例如激光鉆孔和改變板層堆棧順序)使得導線被移動到更靠近過孔短線柱端部的層,也可以用于減小短線柱長度。但在許多高密度PCB板和背板/中間板中,從制造和成本核算的角度來看,這些方式并不總是可行的。在這種情況下,唯一的選擇是通過backdrilling背鉆刪除via stub。當然,短線柱Stub去除不是唯一可以應用于通孔的信號完整性改進技術。使用例如正在申請的專利技術,Sanmina-SCI的Opti-Via TM“通孔調諧”算法來優化未經背鉆的通孔的剩余部分也可以進一步減少通孔引起的信號失真。

背鉆孔有什么樣優點和作用?

影響信號系統信號完整性的主要因素除設計、材料、傳輸線、連接器、芯片封裝等因素外,導通孔對信號完整性有較大影響。而背鉆通過鉆掉沒有起到任何連接或者傳輸作用的通孔段,避免了多余Stub對信號完整性的影響。除此之外,背鉆技術還有如下諸多優點。

減小雜訊干擾;

提高信號完整性;

局部板厚變小;

減少埋盲孔的使用,降低PCB制作難度。

背鉆制作工藝流程

根據提供PCB,對PCB進行一鉆定位并進行一鉆鉆孔;背鉆的一鉆孔偏會加大背鉆孔與一鉆孔對準度差異,對背鉆精度造成較大影響,此處必須嚴格控制一鉆孔位精度。

對一鉆鉆孔后的PCB進行電鍍。此處孔銅不夠的話,會嚴重影響要求。需采用低電流,長時間,一次性鍍夠。電鍍后切片監控銅厚。電鍍參數:15ASF×(48min+48min)。

采用鉆刀對需要進行背鉆的電鍍孔進行背鉆,二鉆鉆孔。背鉆是利用鉆機的深度控制功能實現盲孔的加工,以去除部分孔銅。其公差主要受到背鉆設備精度和介質厚度公差的影響。

對整孔進行數值塞孔。背鉆孔有一頭大、一頭小且有拐角的特點,理論上更容易產生氣泡空洞,需要進行有效塞孔。

對塞孔處理后的板面進行處理。消除殘留。由于銅面和樹脂硬度有很大差異,需要保證磨板后板面平整。

背鉆孔板技術特征有哪些?

背鉆技術使用的情況比較特殊。要求也很復雜。通常應用與信號通信設備,大型伺服器,醫療電子,軍事,航空航天等重要領域。這里領域有專業和深厚的技術儲備和研發力量,需要進行高端技術和產品設計。通常來說,背鉆孔板有如下技術特征。

多數背板是硬板

層數一般為8至50層

板厚:2.5mm以上

厚徑比較大

板尺寸較大

外層線路較少,多為壓接孔方陣設計

背鉆孔板設計需要遵循的規則

一般首鉆最小孔徑>=0.3mm

一次鉆的鉆孔孔徑推薦要求不低于0.3mm。如下圖所示,首鉆鉆孔孔徑用A表示。

背鉆孔通常比需要鉆掉的孔大0.4mm

背鉆鉆孔孔徑一般推薦比一次鉆孔徑大0.25mm~0.4mm。保險起見推薦大0.4mm。如下圖所示,背鉆孔徑用B表示。

背鉆深度控制冗余0.2mm

背鉆是利用鉆機的深度控制功能實現的。由于背鉆的鉆刀是尖狀的,鉆到相應的層時由于鉆刀的傾斜角總會保留有一小段余量。該背鉆深度控制建議至少保留8mil即0.2mm。而且,在層疊設置的時候需要考慮介質厚度,避免出現走線被鉆斷的情況。如下圖所示,背鉆深度冗余用S表示。

如果背鉆要求鉆到M層,那么與M層相鄰未被鉆掉的層之間介質厚度最小0.3mm

背鉆與走線間距

背鉆孔的stub鉆掉層走線與背鉆的距離推薦不小于10mil(0.25mm)。如下圖所示,虛線框圓圈距離背鉆孔外沿的距離為10mil,在虛線框外都是安全的走線區域。

Altium Designer中如何設置背鉆參數?

前面介紹了背鉆技術以及背鉆設計時需要考慮的參數。那么在Altium designer中該如何進行背鉆設計中各參數的設置呢?下面用一具體案例來展示Altium Designer中進行背鉆設計的方法。

步驟1:設置鉆孔層對

首先打孔走線。比如一個8層板,從頂層Toplayer打孔,然后切換到Midlayer1上來走線。剩下的Midlayer2 到底層bottomlayer需要背鉆Backdrilling。此處第一步就是在Design- Layer Stack Manager - Drill Pair 中設置。如下圖所示,起始層Midlayer2,終止層Bottomlayer。切記要勾選Back drill pair選項框表示它是做背鉆用的。

步驟2:確保信號層Midlayer1與背鉆起始層Midlayer2之間層間距不小于0.3mm。

此處在層厚Thickness欄目,經檢查滿足要求。

步驟3:確定背鉆孔需要鉆掉的鍍銅柱長度。

通過Layer Stack Manager中從Midlayer2到Bottomlayer之間的層厚加起來大概1mm左右。由于考慮到背鉆深度控制冗余8mil(0.2mm),在層棧管理器頁面Midlayer1與Midlayer2之間的層厚正好0.254mm介質厚度。因此可以設置需要鉆掉的鍍銅柱為1mm左右。當然這個數值需要根據工程師具體設計中根據要求可適當增減。

步驟4:設置背鉆大小,深度以及網絡。

如下圖所示,在設置Max Stub Length及需要鉆掉的鍍銅柱深度為1,mm。設置背鉆孔大小為比原通孔大小半徑大0.2mm。使得背鉆孔與原通孔孔徑大0.4mm。再設置需要背鉆的過孔網絡即可完成背鉆相關的規則設置。

最終的效果在Altium Designer中3D顯示如下圖。

責任編輯:lq

-

PCB板

+關注

關注

27文章

1496瀏覽量

55248 -

PCB設計

+關注

關注

396文章

4921瀏覽量

95284 -

高頻電路

+關注

關注

12文章

254瀏覽量

36928

原文標題:規則設置如何應用于我的PCB設計?—Back Drill背鉆孔

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IDT信號完整性產品:解決高速信號傳輸難題

高速PCB諧振威力,不容小覷

高速信號切換利器:TMUXHS221LV詳解

Samtec Flyover QSFP系統:高速信號傳輸新方案

Samtec高速線纜深入解析:高速信號完整性的關鍵技術

高速PCB板DDR5數據信號的長STUB要背鉆嗎?

PCB過孔STUB對DDRX地址信號的影響

PCB為啥現在行業越來越流行“淺背鉆”了?

別讓孔偏毀了信號!PCB 背鉆的 XY 精準度如何做到分毫不差?

DPC陶瓷基板電鍍銅加厚工藝研究

焊柱陣列封裝引線拉力測試:設備與流程解析

鍍銅短線柱(STUB)如何影響高速信號?

鍍銅短線柱(STUB)如何影響高速信號?

評論