聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424227 -

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4920瀏覽量

95233 -

視覺

+關(guān)注

關(guān)注

1文章

179瀏覽量

24801

原文標題:PCB設(shè)計檢查12視覺檢查

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

芯片制造檢驗工藝中的全數(shù)檢查

在IC芯片制造的檢驗工藝中,全數(shù)檢查原則貫穿于關(guān)鍵工序的缺陷篩查,而老化測試作為可靠性驗證的核心手段,通過高溫高壓環(huán)境加速潛在缺陷的暴露,確保芯片在生命周期內(nèi)的穩(wěn)定運行。以邏輯芯片與存儲器芯片的測試

PCB設(shè)計師必看!這些‘反常識’操作正在毀掉你的電路板

原因及解決方法: PCB設(shè)計組裝失敗的原因及解決方法 一、設(shè)計階段問題 布局不合理 原因:元件間距過小導(dǎo)致信號干擾或散熱不良;高功率器件與精密元件混布引發(fā)熱應(yīng)力;電源/地線設(shè)計薄弱導(dǎo)致電壓波動。 解決: 使用DFM(可制造性設(shè)計)工具檢查間距和散熱

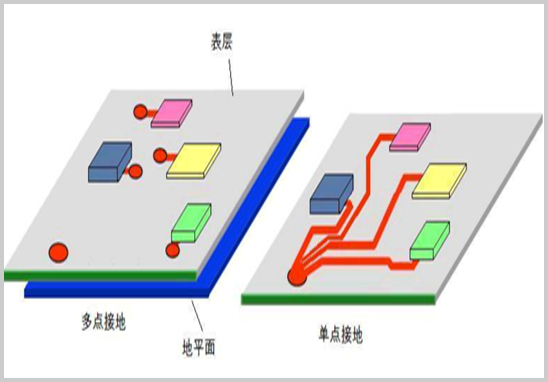

PCB設(shè)計中單點接地與多點接地的區(qū)別與設(shè)計要點

一站式PCBA加工廠家今天為大家講講PCB設(shè)計中的單點接地與多點接地有什么區(qū)別?單點接地與多點接地區(qū)別與設(shè)計要點。在PCB設(shè)計中,接地系統(tǒng)的設(shè)計是影響電路性能的關(guān)鍵因素之一。單點接地和

如何使用PetaLinux檢查RFDC IP狀態(tài)

本篇博客演示了在 ZCU208 評估板和 ZCU216 評估板中通過運行簡單的 RFDC 示例來快速檢查 RFDC IP 初始化的過程。它使用“rfdc-read-write”和“rfdc-seftest”,但不限制用戶實現(xiàn)自己的應(yīng)用程序。

電能質(zhì)量在線監(jiān)測裝置重啟前,安全防護方面的檢查和日常運行時的檢查有何不同?

損壞、數(shù)據(jù)丟失)”,需覆蓋 “硬件連接、操作流程、數(shù)據(jù)風險” 等與重啟強相關(guān)的安全點; 日常運行檢查是 “ 事中持續(xù)性監(jiān)控 ”,聚焦 “及時發(fā)現(xiàn)運行中潛在的安全隱患(如過熱、異常放電、通信中斷)”,需實時跟蹤 “裝置狀態(tài)、環(huán)

技術(shù)資訊 I PCB 設(shè)計完成后進行哪些檢查可以有效避免功虧一簣?

只有當PCB設(shè)計完整呈現(xiàn)了成功組裝所需的全部信息時,設(shè)計才算真正完成。即便電路板已完成布線,仍需進行檢查與復(fù)核,以確保PCB能夠正確組裝。針對PCB設(shè)計

凡億Allegro Skill布線功能-檢查跨分割

在進行高速PCB設(shè)計的過程中,高速信號線需要進行阻抗控制,那么參考平面的完整性對于高速信號的完整性和穩(wěn)定性至關(guān)重要。然而,如果僅僅依賴于肉眼去檢查參考平面的完整性,往往容易遺漏一些關(guān)鍵的細節(jié),這可

網(wǎng)絡(luò)配線架打線操作的質(zhì)量檢查措施有哪些

網(wǎng)絡(luò)配線架打線操作的質(zhì)量檢查是確保網(wǎng)絡(luò)布線系統(tǒng)穩(wěn)定性和可靠性的關(guān)鍵環(huán)節(jié)。以下從外觀檢查、電氣性能測試、功能驗證、標識與文檔檢查四個維度,系統(tǒng)闡述質(zhì)量檢查的核心措施及具體方法: 一、外觀

如何優(yōu)化您的PCB設(shè)計評審流程

印刷電路板(PCB)設(shè)計評審是在產(chǎn)品開發(fā)的各個階段檢查電路板設(shè)計中潛在錯誤和問題的重要環(huán)節(jié)。其形式既可以是需要正式簽字確認的清單式評審,也可以是對原理圖和 PCB 布局的自由式

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計“好搭子”來了!

作為深耕PCB設(shè)計檢查的專業(yè)工具,華秋DFM歷經(jīng)多年迭代,已從最初的基礎(chǔ)設(shè)計檢查工具發(fā)展為覆蓋全流程的智能制造解決方案。通過持續(xù)優(yōu)化1200+細項檢查規(guī)則,累計服務(wù)超40萬工程師用戶,

原理圖和PCB設(shè)計中的常見錯誤

在電子設(shè)計領(lǐng)域,原理圖和PCB設(shè)計是產(chǎn)品開發(fā)的基石,但設(shè)計過程中難免遇到各種問題,若不及時排查可能影響電路板的性能及可靠性,本文將列出原理圖和PCB設(shè)計中的常見錯誤,整理成一份實用的速

概倫電子先進電路檢查分析平臺工具NanoSpice CCK介紹

NanoSpiceCCK是一款先進的電路檢查可靠性分析工具,支持晶體管級全面的ERC、SOA電路檢查,適用于前后仿電路規(guī)則檢查功能,能夠快速提供準確、簡潔的測試結(jié)果,方便設(shè)計人員及時發(fā)現(xiàn)電路中

PCB設(shè)計中容易遇到的問題

印制電路板(PCB)設(shè)計是電子產(chǎn)品開發(fā)中的關(guān)鍵環(huán)節(jié),其質(zhì)量直接影響產(chǎn)品的性能和可靠性。下面將分享幾個PCB設(shè)計中容易遇到的問題,提供其解決方案,希望對小伙伴們有所幫助。

PCB設(shè)計檢查中的視覺檢查

PCB設(shè)計檢查中的視覺檢查

評論