自1985年賽靈思開發出第一個商業上可行的FPGA以來,FPGA領域的價值已增長至數十億美元。賽靈思本身的年收入超過30億美元,在汽車,5G,基礎設施和數據中心市場中占有重要地位。如今,它已經成為FPGA領域最大的公司,領先于英特爾(通過收購Xilinx的最大長期競爭對手Altera)。

Xilinx FPGA提供了性能和靈活性的結合以及低功耗。它的頂級器件之一Virtex UltraScale +提供了在14nm / 16nm工藝節點中制造的高端信號處理和I / O帶寬,使其成為業界功能最強大的FPGA系列。

設計FPGA的電源系統

對于設計工程師來說,FPGA不僅可以提供性能和靈活性還不夠,而且還必須易于使用它們進行設計,以使上市時間盡可能短。如果您的產品遲到了,那么產品的好壞通常無關緊要。

通過與工程師交談,我們知道功率級設計分析是可能會減慢使用FPGA的主要問題之一。許多設計工程師發現,可用軟件的功能可能會有所幫助,尤其是不正確的負載模擬可能會成為問題。

為了成功進行設計,您需要在過程的早期確定FPGA的電源規格,這甚至可能在FPGA內部邏輯設計之前就已經確定。FPGA的靈活性可能意味著在設計周期的后期做出的決定會嚴重影響電源要求。

因此,在此早期階段,您需要準確的最壞情況功率分析,以便可以適當地設計系統的功率部分。如果電源系統設計欠佳,則可能意味著FPGA工作超出規范,可能會降低其性能甚至影響可靠性。相反,過度設計的動力系統可以額外的大小,重量和復雜性,以您的解決方案添加-這一切都增加了不必要的成本。

對于復雜的FPGA,要考慮這些功耗問題并不是很簡單的,因為它們要考慮多個不同的電源軌。為了提供幫助,Xilinx提供了Xilinx功耗估算器(XPE),這是一種基于電子表格的免費工具,可以估算功耗。設計人員可以指定他們希望使用的FPGA以及其他參數,例如預期的環境溫度和散熱片供應。

XPE提供了詳細的功率和熱分析,但仍需要設計人員獲得更多幫助。假設XPE提供的數據可以在電源設計工具中使用。在這種情況下,優化工具可以幫助選擇正確的組件并運行“假設情況”方案以輕松查看不同的選項。

使用軟件工具優化電源設計

這種軟件工具的一個示例是Flex Power Designer(FPD)。該免費工具概述了完整的電源系統設計,并具有用于復雜的功率級分析,環路優化和熱建模的內置仿真,還包括其他功能,例如易于排序和相位擴展。除了推薦Flex Power Modules的最佳組件外,它還使設計人員可以包括其他供應商的電源設備,從而可以對整個電源解決方案進行建模。

為了優化基于Xilinx FPGA的設計,該軟件的最新4.0版本現在支持導入從Xilinx XPE工具導出的文件。最初,此功能支持Virtex Ultrascale +器件,并且隨著時間的推移,支持的系列列表將不斷增加。

通過直接導入XPE文件,產品設計人員現在可以利用有關Xilinx FPGA特定要求的準確得多的信息來模擬其電源系統。FPD軟件會自動檢測潛在問題,例如瞬態電源需求,并建議合適的電源組件。

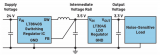

對于每條導軌,您都可以在FPD內優化設計,以最大程度地提高系統效率或最小化功耗和電流開銷,這通常是成本最低的解決方案。在這兩個極端之間拖動屏幕上的滑塊很簡單,FPD會生成一個模擬,顯示預測的效率,系統設計和所需的組件。中間總線電壓可以設置為用戶指定的參數,也可以允許FPD推薦最佳值。

您還可以研究和模擬FPD中的許多其他選項,例如PCB電阻對電壓降的影響。除XPE支持外,最新的4.0版本還包括一項新的系統優化功能,可根據配置的負載查找產品并優化總線電壓,并改進了負載瞬態仿真,并支持Flex的PMU(DC / DC點)。負載轉換器。

總體而言,與FPD之類的軟件工具一起使用可使設計人員優化其電源設計,以提高效率和成本。通過支持XPE文件,現在可以為包含Xilinx FPGA的設計獲得最準確,最可靠的仿真。這樣可以節省時間,降低錯誤風險,最大程度地降低組件成本,并確保最終產品具有合適的電源系統-意味著可以充分利用FPGA的性能和靈活性。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636312 -

pcb

+關注

關注

4404文章

23878瀏覽量

424271 -

電源設計

+關注

關注

31文章

1834瀏覽量

69691 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131137

發布評論請先 登錄

智多晶重磅發布HQPEP功耗評估工具

數字IC/FPGA設計中的時序優化方法

智多晶EDA工具HqFpga軟件的主要重大進展

SEGGER推出Flasher BitStreamer軟件工具

Analog Devices發布ADI Power Studio?和網頁端新工具 簡化電源管理設計和優化

嵌入式軟件測試與專業測試工具的必要性深度解析

電源控制器MCU硬件在環(HIL)測試方案

高集成度超低噪聲電源設計方案

關于FPGA的軟件工具電源優化設計方案

關于FPGA的軟件工具電源優化設計方案

評論