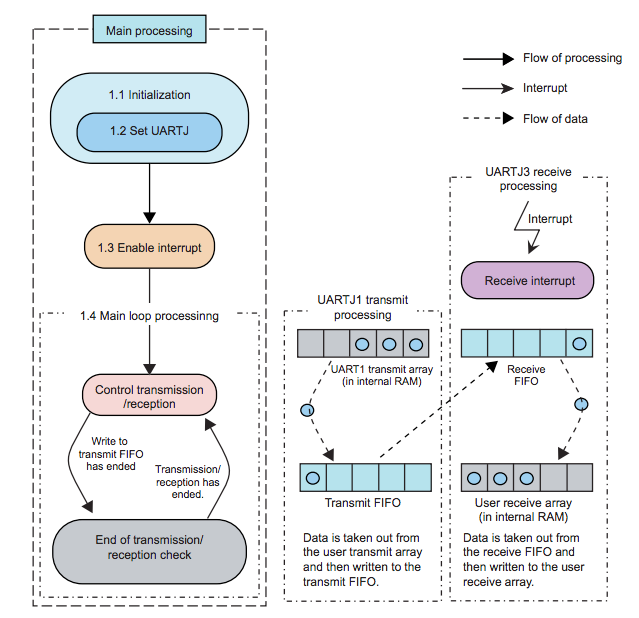

本應用筆記介紹了具有FIFO(先進先出)設置說明的UARTJ串行接口控制,以及使用示例的概述。該文檔還描述了使用環境,例如電路圖,開發環境,所使用的軟件以及帶有流程圖,主要處理,接收/發送中斷處理和寄存器設置的示例應用程序。

概述

本應用筆記舉例說明了UARTJ的用法示例。

該示例程序對V850E2 / MN4微控制器進行了基本的初始設置,例如時鐘頻率的選擇和端口I / O的設置。初始化結束后的主要處理將執行UARTJ1和UART3之間的串行通信。UARTJ1發送數據,而UARTJ3接收數據。

該軟件的要點如下所示。

UARTJ軟件處理

主循環處理

主循環處理主要分為兩個。它反復控制發送/接收,并等待發送/接收結束。如果在設置了UARTJ的操作之后將發送數據寫入URTJnFTX寄存器,則將數據寫入發送FIFO。存儲在發送FIFO中的數據被傳送到發送移位寄存器,然后通過TXDnF引腳開始串行發送。

在此示例程序中,發送UARTJ1發送16字節數據,接收UARTJ3從UARJ1接收16字節數據。內部RAM具有16字節(一個字節(一個塊數據)?16)的用戶發送陣列來存儲發送數據,而16字節的用戶接收陣列來存儲接收數據。

當在主循環處理期間發生發送/接收中斷或狀態中斷時,將執行相應的中斷處理。在此示例程序中,中斷在以下列出的時間發生。

發送中斷:當發送FIFO為空時

接收中斷:當接收FIFO滿時

狀態中斷:在接收或發送過程中發生錯誤時

發展

必須安裝下面列出的通行費才能運行示例程序。

CubeSuite +

瑞薩電子的集成開發環境CubeSuite +提供了用戶開發應用程序所需的各種軟件開發工具。用戶可以在各種開發階段無縫,輕松地使用這些工具,包括編碼,匯編,編譯,使用仿真器或模擬器進行調試以及Flash編程。

MINICUBE

MINICUBE是瑞薩電子的通用在線仿真器,它采用JTAG接口系統。它允許用戶調試板載真實處理器,并提供高度透明和穩定的仿真功能。需要適配器才能將TB板連接到MINICUBE。

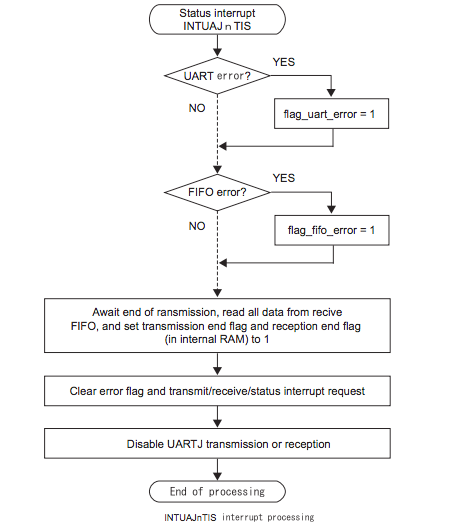

狀態中斷處理

在發送/接收過程中發生錯誤時,會發生狀態中斷請求。

數據一致性錯誤

超時錯誤

取景錯誤

奇偶校驗錯誤

溢出錯誤

溢出錯誤

狀態中斷處理

當在發送/接收期間檢測到錯誤時,URTJnSTR1和URTJnFSTR1寄存器中的相應錯誤標志將設置為1。然后,UARTJ狀態中斷處理將清除發送/接收FIFO。通過等待相當于傳輸16字節數據所需的時間來清除發送FIFO。通過從中讀取所有接收到的數據來清除接收FIFO。內部RAM中的發送標志和接收標志設置為1。通過URTJnSTC和URTJnFSTC寄存器清除SFR錯誤標志,并清除發送/接收中斷請求或狀態中斷請求。UARTJ1和UARTJ3暫時停止并返回主循環(在主循環處理中恢復發送/接收)。

編輯:hfy

-

微控制器

+關注

關注

48文章

8381瀏覽量

164619 -

寄存器

+關注

關注

31文章

5608瀏覽量

130003 -

串行通信

+關注

關注

4文章

608瀏覽量

37141 -

接口控制

+關注

關注

0文章

12瀏覽量

8901

發布評論請先 登錄

探索英飛凌BTS71220-4ESE:一款強大的串行接口電源控制器

DAC3174 產品核心信息總結

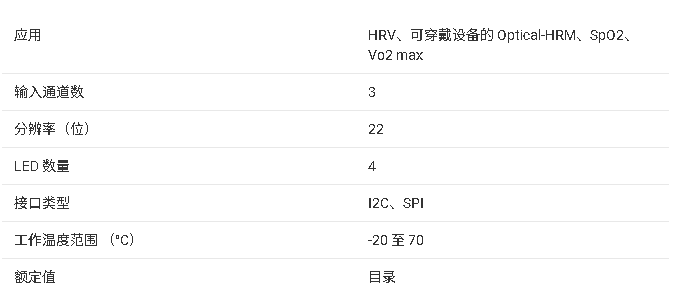

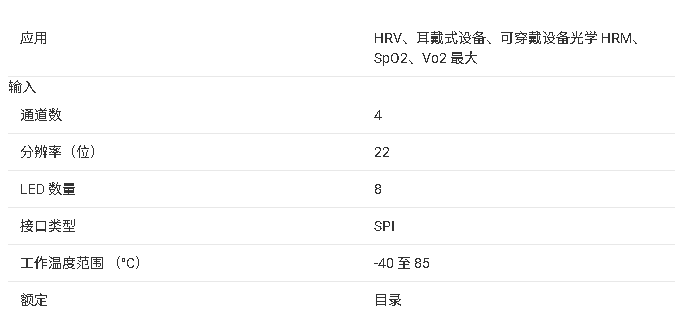

AFE4410 帶 FIFO 的低功耗集成 AFE技術手冊

UART接口數據線接收和發送數據

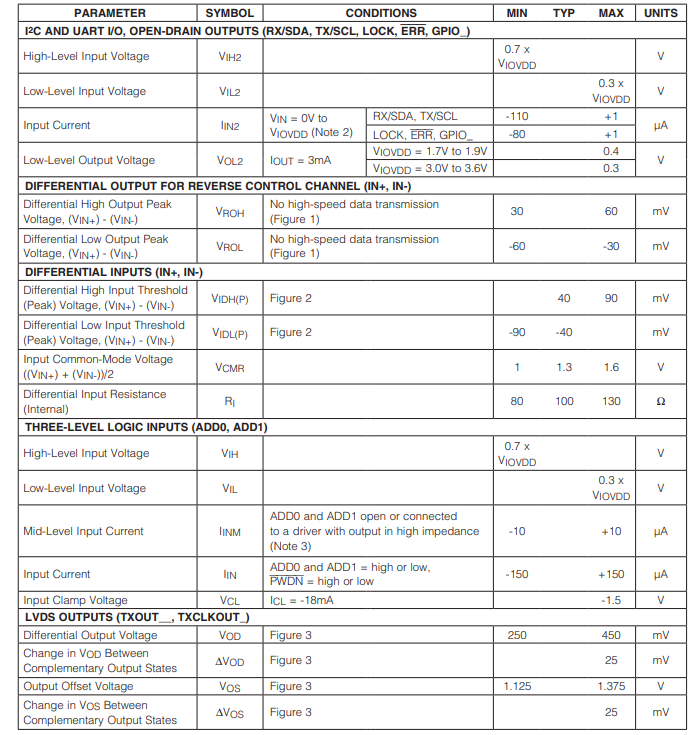

MAX9268多媒體串行鏈路解串器,具有LVDS系統接口技術手冊

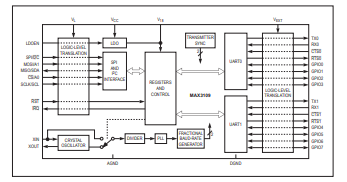

MAX3107SPI/I2C UART,具有128字FIFO技術手冊

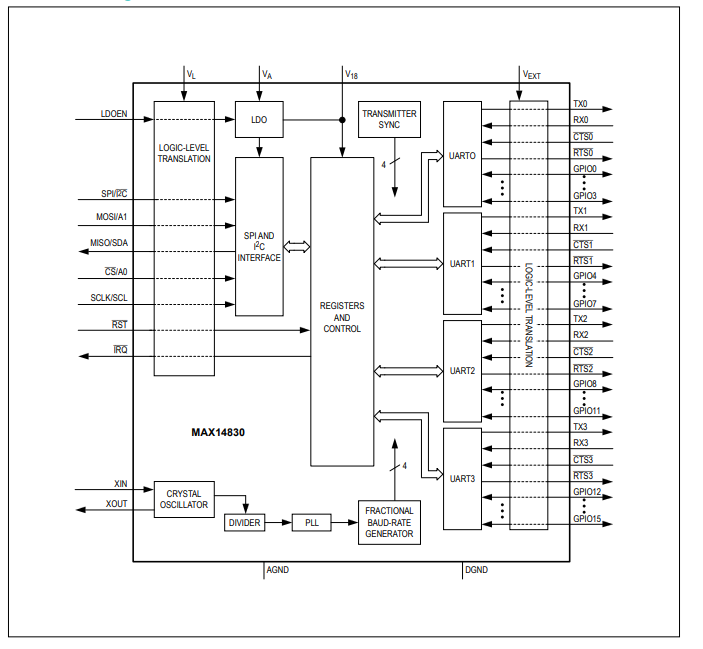

MAX14830四通道串行UART,具有128字FIFO技術手冊

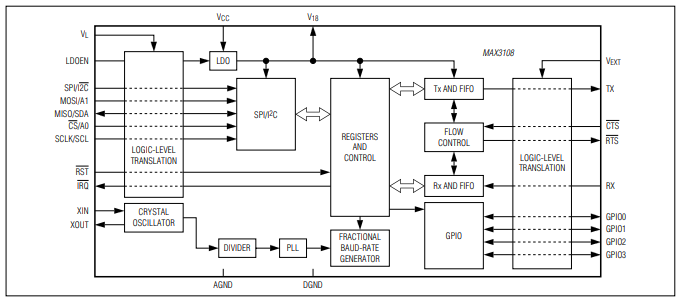

MAX3108 SPI/I2C UART,具有128字FIFO,WLP封裝技術手冊

基于FPGA的FIFO實現

具有FIFO(先進先出)設置的UARTJ串行接口控制

具有FIFO(先進先出)設置的UARTJ串行接口控制

評論