總線、接口和協(xié)議,這三個詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

總線是一組傳輸通道,是各種邏輯器件構成的傳輸數(shù)據(jù)的通道,一般由由數(shù)據(jù)線、地址線、控制線等構成。接口是一種連接標準,又常常被稱之為物理接口。

協(xié)議就是傳輸數(shù)據(jù)的規(guī)則。

我們通常說的PCIE,既可以是PCIE信號,也可以是PCIE接口、PCIE總線,還可以是PCIE協(xié)議。之所以這么復雜,主要原因就是每個人對概念認知的差異。再比如,只要百度一下串行和并行,就會出來很多類似“串行通信與并行通信”、“串行接口與并行接口”、“串行總線與并行總線”、“串行協(xié)議與并行協(xié)議”以及“串行傳輸與并行傳輸”等概念介紹,既有傳輸(通信)方式,又有接口類型,同時還有數(shù)據(jù)本身的協(xié)議特點,信號、協(xié)議、總線和接口,有時候看起來是一樣的,但細細思量卻還是有差別的,總之不是一兩句話就能說清楚的。舉個簡單的例子,PCI總線說的是一組傳輸通道,而PCI接口是一種連接標準,兩者之間的關系就是PCI接口的設備都要通過PCI總線來進行通信,而PCI總線上走的設備并不全是PCI接口的,像集成聲卡,走的就是PCI總線,但是沒有走PCI接口。在這里PCI總線提供了一種通道,這個通道上可以有不同的符合這種通道要求的接口設備或信號(PCI信號或Audio信號)。打個更進一步的比方:兩者關系就像馬車(接口設備)和馬路(總線)一樣,馬車必須在馬路上走,而馬路上不一定走馬車(牛車等)。

圖4?2馬路上的車水馬龍

車(接口、信號)有車(接口、信號)的標準(協(xié)議),如馬車、汽車、火車、貨車、自行車等(PCIE、SATA、SAS、USB等信號標準);路(通道、總線)有路的標準,如馬路、人行道、高速公路等(PCIE、SATA、SAS、USB等通道標準),所以協(xié)議里面又包含通道(總線)協(xié)議和信號(接口)協(xié)議。是不是感覺越講越復雜。

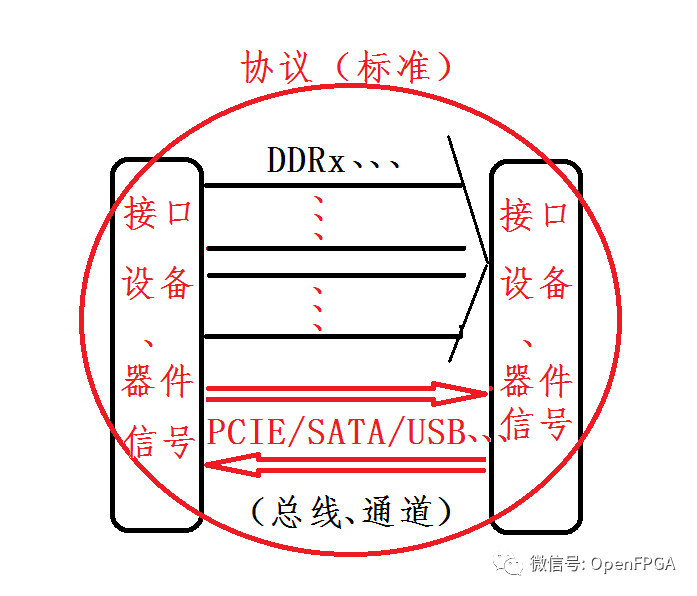

用下圖來簡單介紹下這幾個概念之間的關系。

圖4?3協(xié)議、接口、總線的關系

協(xié)議即總體框架,定義接口設備、器件及信號、總線及通道之間需要滿足的關系,即要實現(xiàn)信號的傳輸,所有這些組成成員必須通力合作,各自滿足協(xié)議要求的各種必要條件。

責任編輯:xj

原文標題:AXI總線詳解-總線、接口以及協(xié)議

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

AXI總線

+關注

關注

0文章

68瀏覽量

14757 -

AXI

+關注

關注

1文章

145瀏覽量

17940

原文標題:AXI總線詳解-總線、接口以及協(xié)議

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

利用開源uart2axi4實現(xiàn)串口訪問axi總線

如果想運用蜂鳥E203給的一個AXI接口,只需要自己寫一個AXI協(xié)議的從機就行嗎,蜂鳥的cpu核需要改動什么嗎?

將e203 例化AXI總線接口

AXI GPIO擴展e203 IO口簡介

像這種受電端/負載端的電壓誘騙芯片和電源端//負載端的協(xié)議芯片有什么區(qū)別,沒搞懂

RDMA簡介8之AXI 總線協(xié)議分析1

NVMe協(xié)議簡介之AXI總線

一文詳解AXI DMA技術

一文詳解Video In to AXI4-Stream IP核

一文搞懂AXI總線、接口和協(xié)議的區(qū)別

一文搞懂AXI總線、接口和協(xié)議的區(qū)別

評論