每次我們敷銅之后, 敷銅的形狀不滿意或者存在直角, 我們需要對其進行編輯, 編輯出自己想要的形狀。

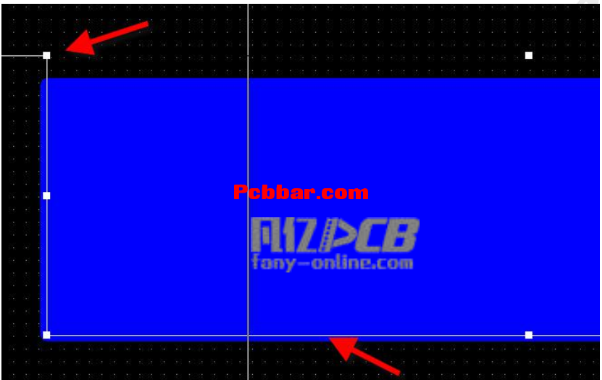

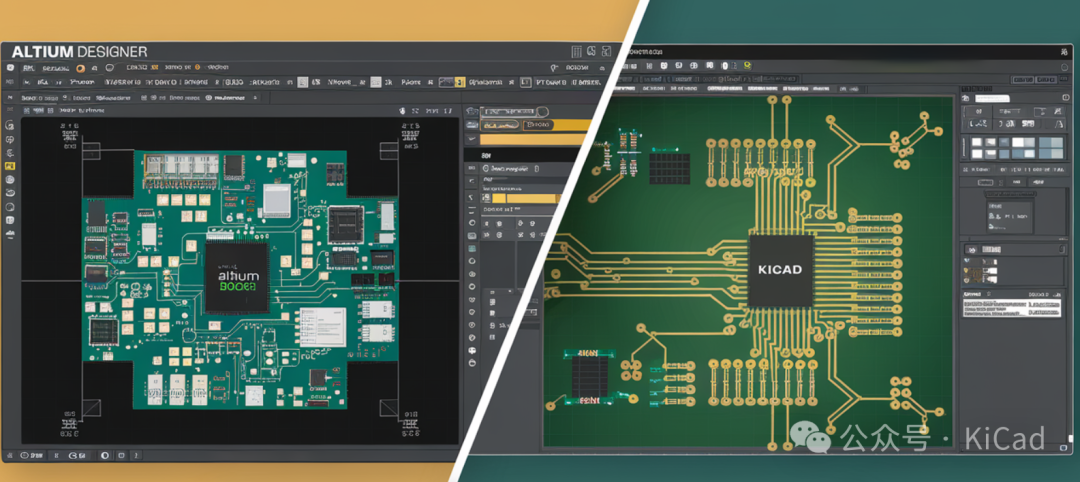

1、 Altium15 以下的版本, 直接執(zhí)行快捷鍵“MG” , 可以進入銅皮的編輯狀態(tài),15 版本以上的直接點擊進入, 如圖 36。 可以對其“白色的點狀” 進行拖動編輯器形狀, 也也可以點擊抓取邊緣線拉伸改變當前敷銅的形狀。

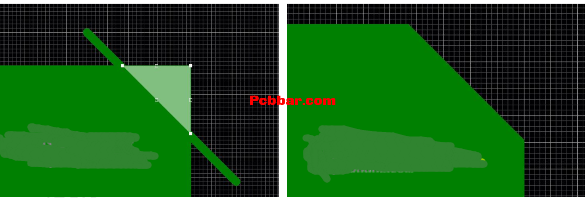

當我們需要把敷銅的直角修改成鈍角時, 我們怎么操作呢, 我們可以, 執(zhí)行菜單命令“Place-Slice Polygon Pour” , 在敷銅的直角繪制一根分割線, 會把敷銅分割成兩塊, 把直角這塊和分割線進行刪除就得到了鈍角

編輯:hfy

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424234 -

altium

+關(guān)注

關(guān)注

48文章

1006瀏覽量

122158 -

敷銅

+關(guān)注

關(guān)注

0文章

25瀏覽量

12561

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

【「Altium Designer 25 電路設(shè)計精進實踐」閱讀體驗】+設(shè)計實現(xiàn)之路

工具中,均提供了原理圖庫和PCB庫的元器件自行設(shè)計與添加功能,以適應(yīng)變化多端的實際應(yīng)用需求。這便是軟件Altium Designer進行設(shè)計與開發(fā)之路。

圖1 專業(yè)術(shù)語

圖2 原理圖設(shè)計

圖3 PCB版圖設(shè)計

圖4 覆銅

發(fā)表于 02-23 23:52

Linux中如何修改ddr的分配容量

在 U-Boot 中修改 DDR 容量通常涉及以下幾個步驟,尤其是在嵌入式系統(tǒng)中,當更換或升級DDR內(nèi)存芯片后:

銅厚對阻抗的影響在實際設(shè)計中如何驗證?

銅厚對阻抗的影響在實際設(shè)計中,主要通過仿真驗證和實測驗證相結(jié)合來確保準確性。作為國內(nèi)領(lǐng)先的PCB測量儀器、智能檢測設(shè)備等專業(yè)解決方案供應(yīng)商,班通科技自研推出了國內(nèi)首款國產(chǎn)替代手持式銅厚測試儀

Altium Designer集成庫如何進行離散編輯

集成庫是一個原理圖庫和PCB封裝庫對應(yīng)好封裝的一個集合庫,集成庫的方便就是可以直接調(diào)用,但是往往我們需要對封裝庫添加或者修改,集成庫是已經(jīng)封裝好了不能進行編輯,如果需要編輯我們需要先離散。

銅在微機電系統(tǒng)中的應(yīng)用

在 MEMS(微機電系統(tǒng))中,銅(Cu)因優(yōu)異的電學(xué)、熱學(xué)和機械性能,成為一種重要的金屬材料,廣泛應(yīng)用于電極、互連、結(jié)構(gòu)層等關(guān)鍵部件。

TSV工藝中的硅晶圓減薄與銅平坦化技術(shù)

本文主要講述TSV工藝中的硅晶圓減薄與銅平坦化。 硅晶圓減薄與銅平坦化作為 TSV 三維集成技術(shù)的核心環(huán)節(jié),主要應(yīng)用于含銅 TSV 互連的減薄芯片制造流程,為該技術(shù)實現(xiàn)短互連長度、小尺

銅基板抗壓測試不過,如何科學(xué)選擇材料?

銅基板作為電子產(chǎn)品中常見的散熱和導(dǎo)電載體,其性能直接關(guān)系到產(chǎn)品的可靠性和壽命。其中,抗壓性能是衡量銅基板機械強度的重要指標,特別是在工業(yè)應(yīng)用和高功率設(shè)備中更顯關(guān)鍵。如果銅基板在抗壓測試

KiCad 已支持導(dǎo)入 Altium 工程(Project)

“ ?9.0.3 的小版本更新中增加一個非常實用的功能:直接導(dǎo)入 Altium 的工程,省去了分別導(dǎo)入原理圖和 PCB 的麻煩。? ” ? Altium 導(dǎo)入器 從 ?8.0 開始,KiCad

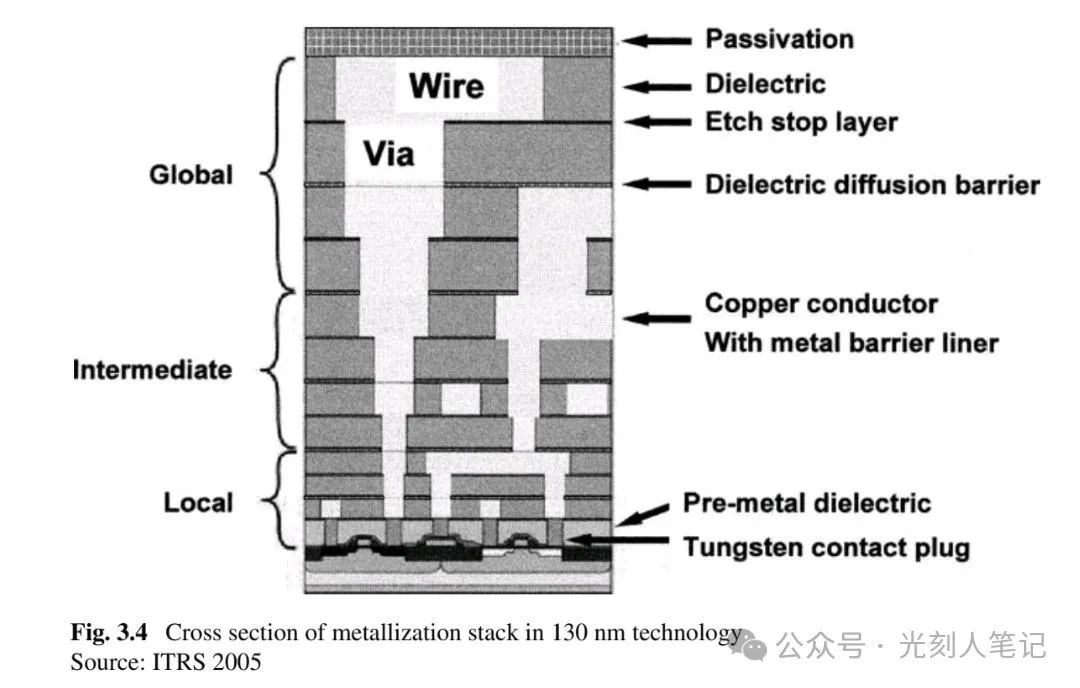

一文詳解銅互連工藝

銅互連工藝是一種在集成電路制造中用于連接不同層電路的金屬互連技術(shù),其核心在于通過“大馬士革”(Damascene)工藝實現(xiàn)銅的嵌入式填充。該工藝的基本原理是:在絕緣層上先蝕刻出溝槽或通孔,然后在溝槽或通孔中沉積

激光焊接技術(shù)在焊接銅端子工藝中的應(yīng)用

,激光焊接技術(shù)因其獨特的優(yōu)勢逐漸成為銅端子焊接的理想選擇。下面一起來看看激光焊接技術(shù)在焊接銅端子工藝中的應(yīng)用。 激光焊接技術(shù)在焊接銅端子工藝中

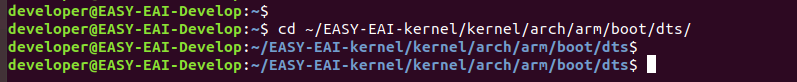

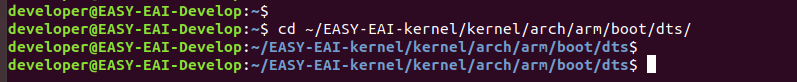

基于RV1126開發(fā)板修改CAN內(nèi)核設(shè)備樹

編輯設(shè)備樹文件,執(zhí)行以下指令可以修改nano的板級頭文件,如下圖所示。(比如基于MCP2515把復(fù)用為SPI1的硬件資源轉(zhuǎn)成CAN對源代碼進行修改)

基于RV1126開發(fā)板修改GPIO內(nèi)核設(shè)備樹

編輯設(shè)備樹文件,執(zhí)行以下指令可以修改nano的板級頭文件,如圖所示。(比如把復(fù)用為SPI1的硬件資源改成通用的GPIO對源代碼進行修改)

PCB設(shè)計整板鋪銅說明

在PCB(印制電路板)設(shè)計中,整板鋪銅是一個需要仔細考慮的問題。鋪銅,即在PCB的空白區(qū)域覆蓋銅膜,這一做法既有其顯著的優(yōu)勢,也可能帶來一些潛在的問題。是否整板鋪

純銅 vs 無氧銅網(wǎng)線:核心區(qū)別解析

電解法提煉,純度≥99.9%,但可能含微量雜質(zhì)(如氧、硫等)。 無氧銅:經(jīng)脫氧工藝處理,氧含量≤0.001%,雜質(zhì)總量更低,純度更高。 2. 導(dǎo)電性能 無氧銅更優(yōu): 銅中的氧會形成氧化

Altium中如何編輯修改敷銅

Altium中如何編輯修改敷銅

評論