最近在學(xué)習(xí)FPGA DSP相關(guān)設(shè)計,從濾波器開始學(xué)習(xí),最開始先生成兩個正弦信號,產(chǎn)生混頻信號,通過modelsim仿真來驗證設(shè)計。 本案例用Block Design方法進行設(shè)計(也可以選擇編寫.v文件的形式進行設(shè)計)。

信號源產(chǎn)生

本次案例用DDS IP核產(chǎn)生兩個簡單的正弦信號,為了方便后面觀察,這里分別產(chǎn)生一個4M和一個5M的正弦信號。

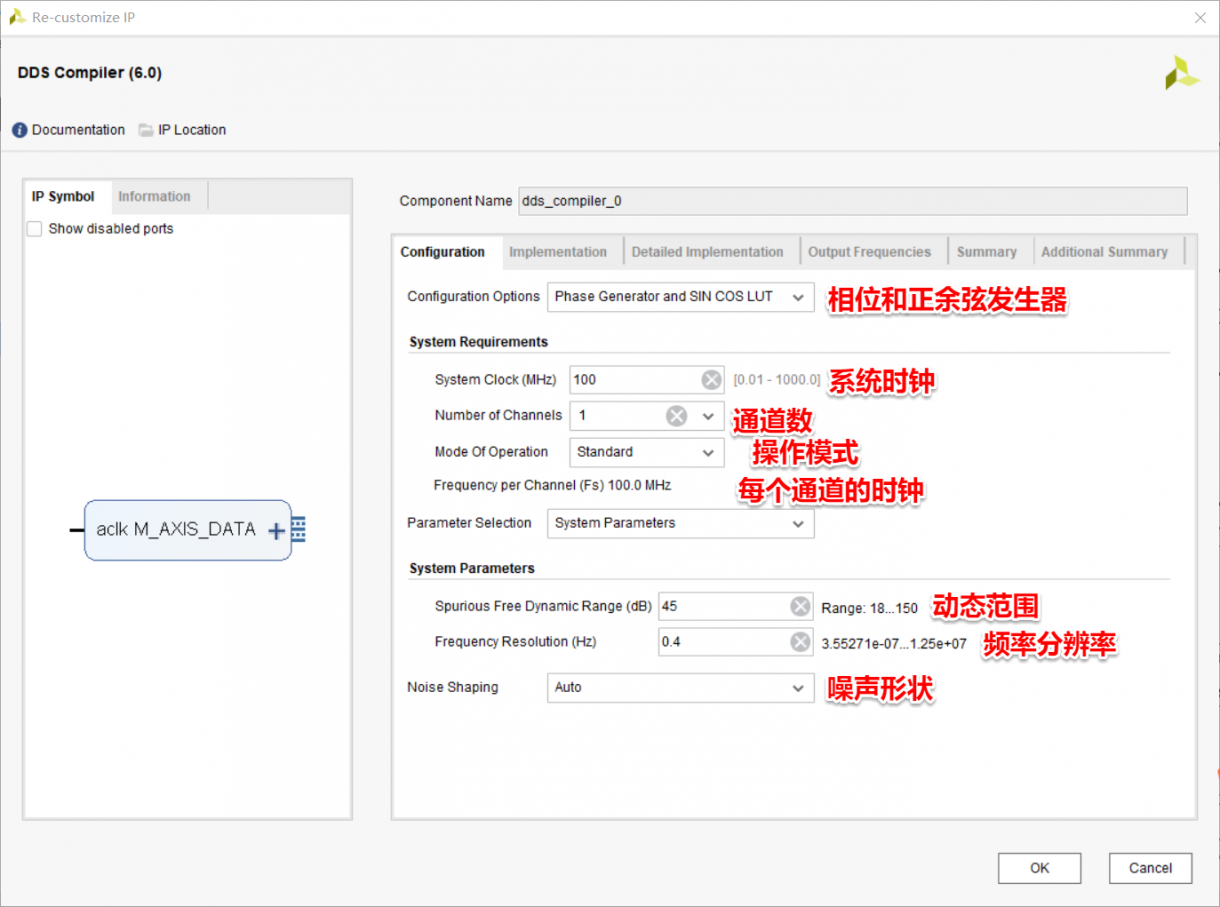

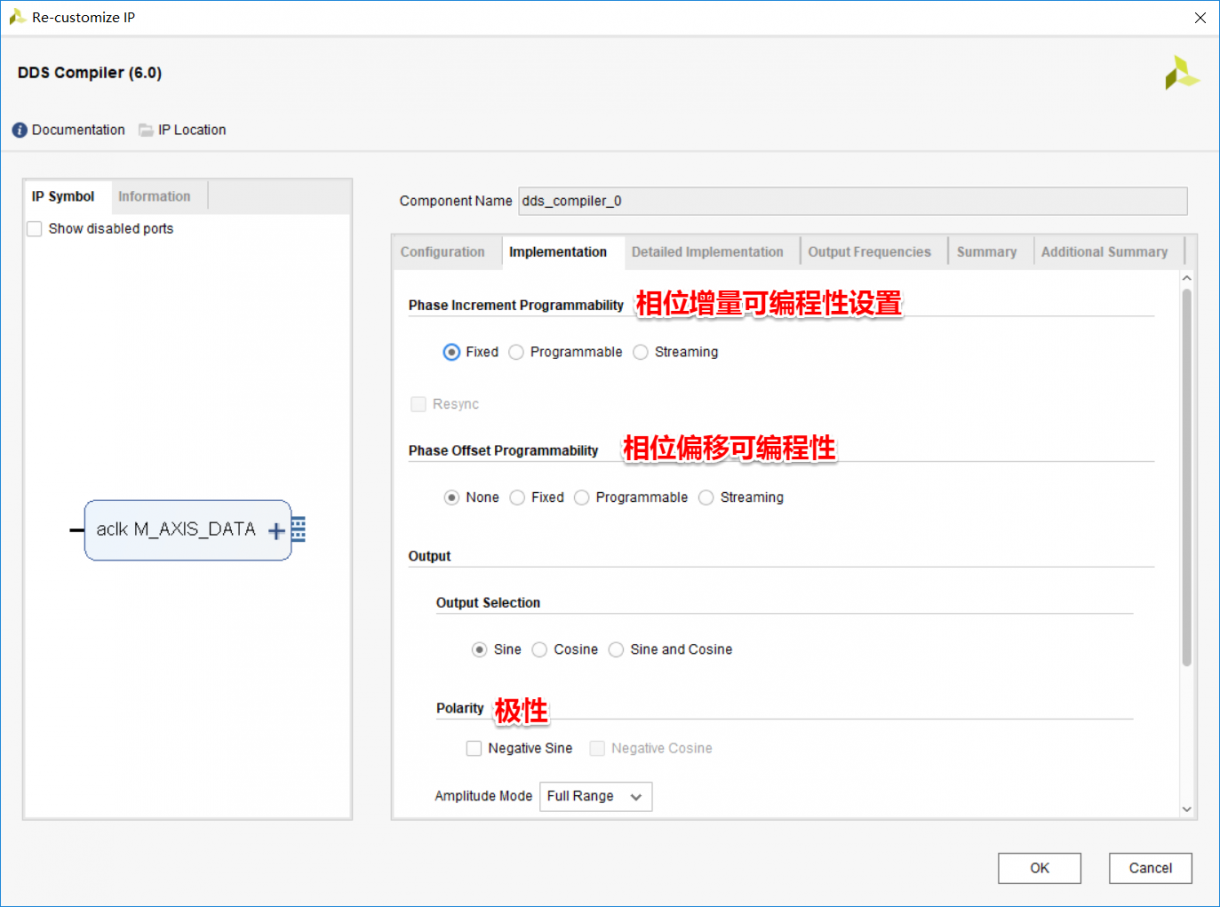

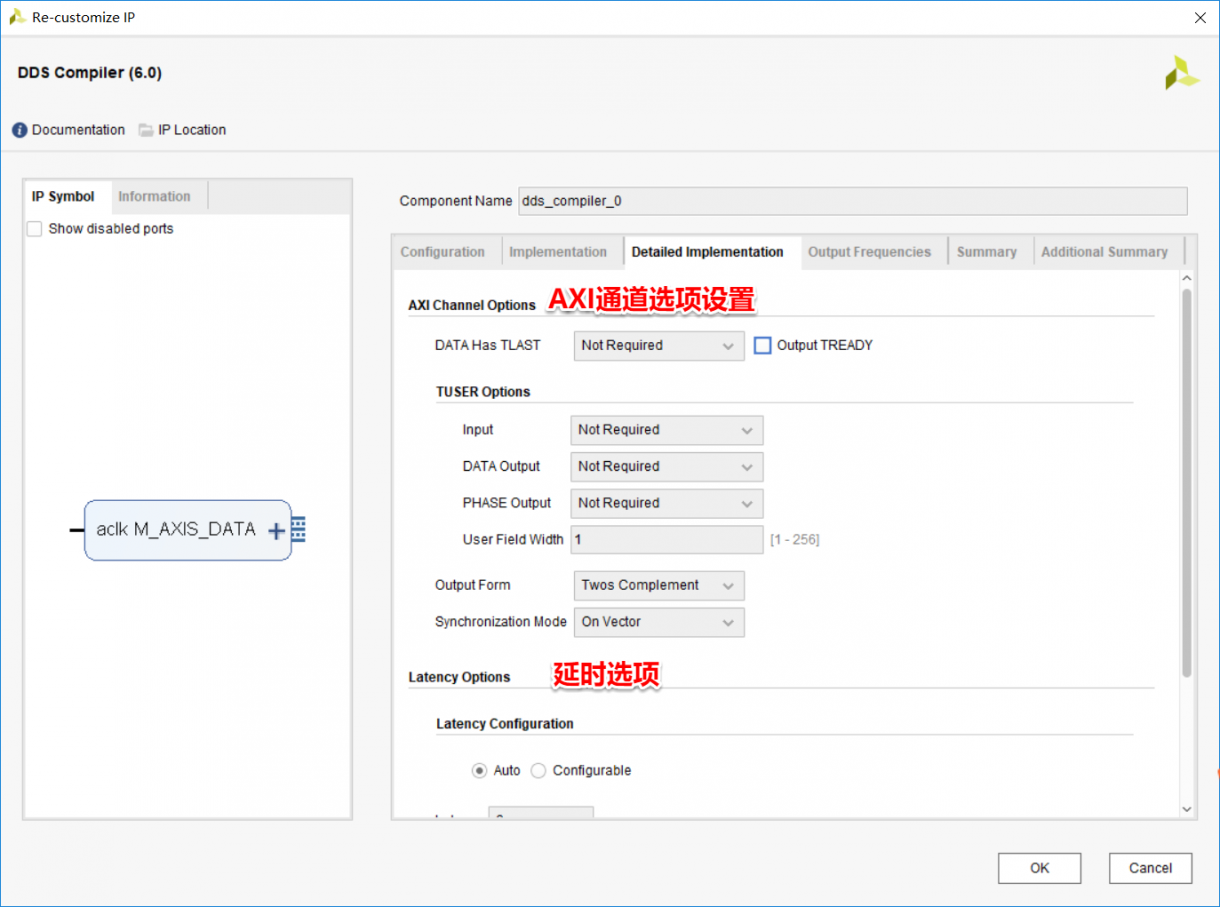

雙擊打開DDS IP核進入設(shè)置,對相關(guān)參數(shù)進行設(shè)置

本案例相關(guān)設(shè)置如下所示:

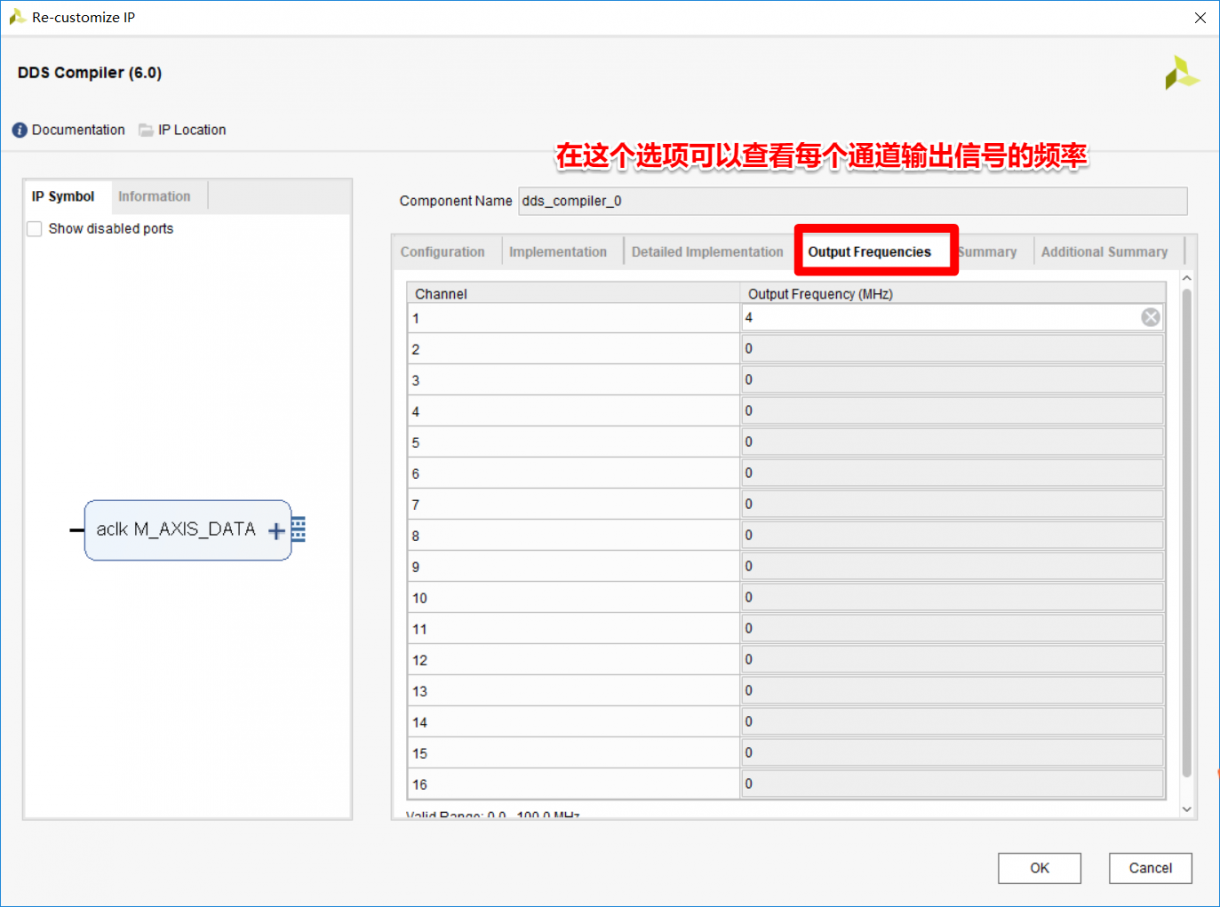

設(shè)置完相關(guān)參數(shù)之后,可以在Output Frequencies中查看頻率信息。

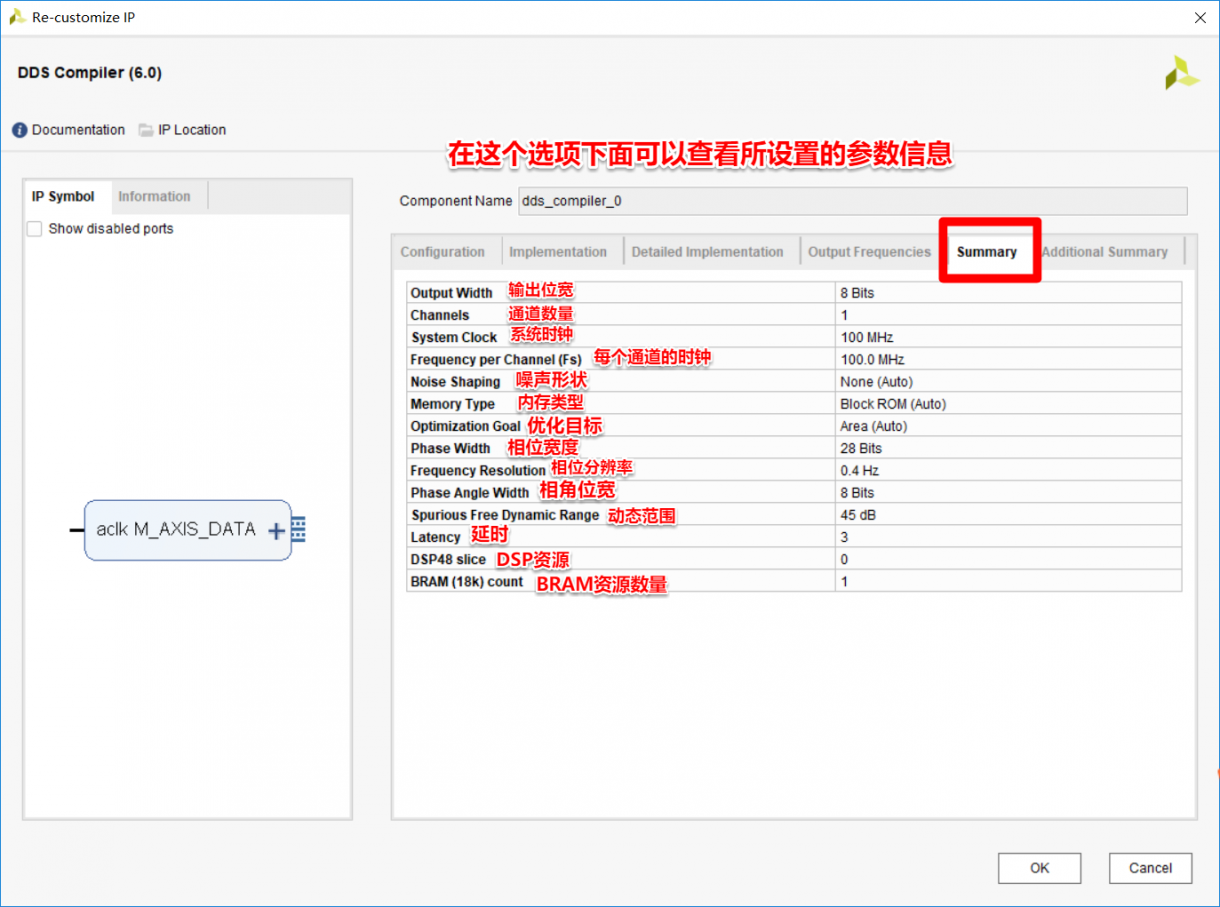

同樣的,在Summary選項中查看設(shè)置的參數(shù)信息

混頻

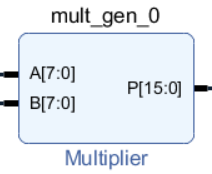

調(diào)用一個乘法器,將兩路正弦信號進行混頻,觀察混頻之后的信號。

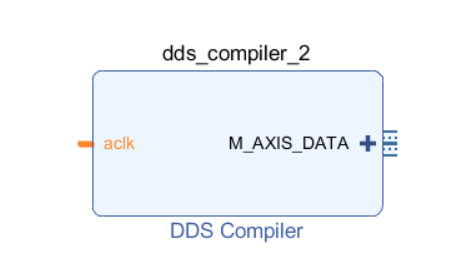

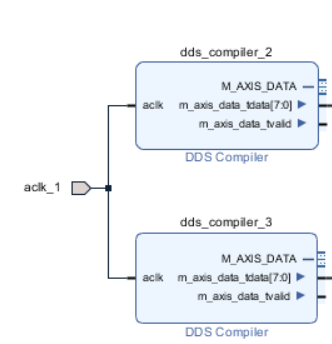

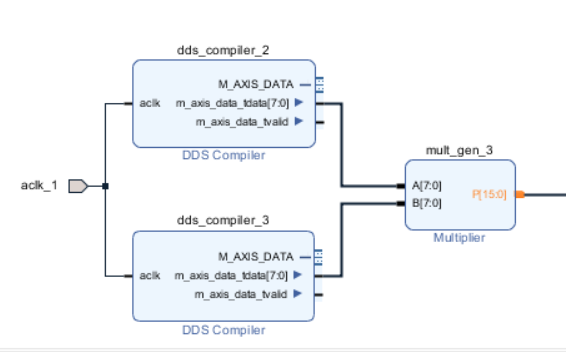

會產(chǎn)生一個aclk的輸入管腳,然后把另外一個DDS IP核的aclk引腳連接到aclk輸入管腳上。

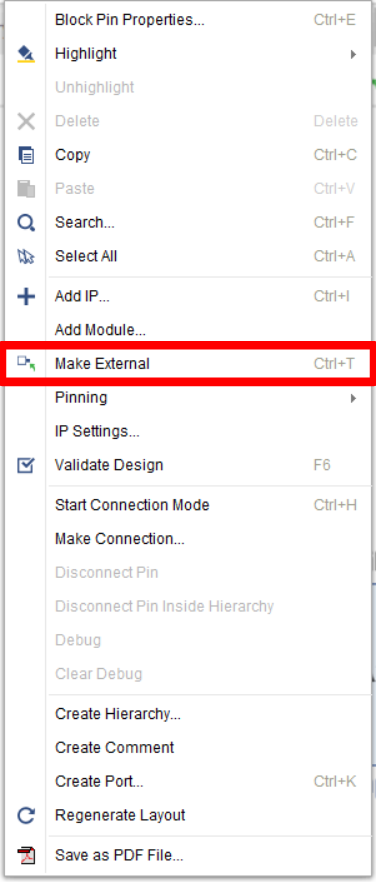

然后把兩個DDS的M_ASIS_DATA輸出管腳分別連接到mult_gen IP核的A和B上,之后,右鍵點擊P管腳,選擇make external自動生成輸出的管腳即可。

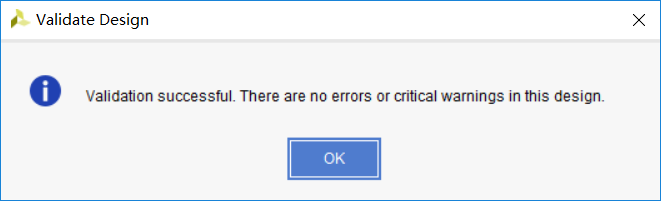

右鍵點擊空白處,選擇valid design,出現(xiàn)如下窗口,說明連接沒有錯誤。

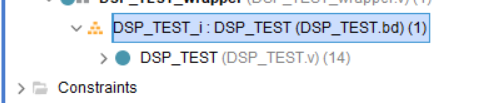

連線完成之后,ctrl+s保存一下工程,然后在source窗口里面,有一個類似于金字塔形狀的選項

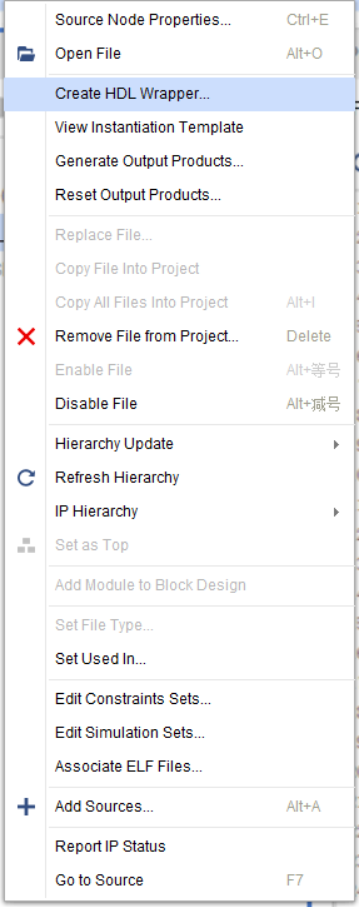

這個就是工程的BD文件,右鍵點擊,選擇create a HDL wapper,生成一個頂層文件。

仿真

工程建立完成以后,我們寫個TB文件對其進行仿真,測試代碼如下:

module tb_top(

);

reg aclk_0 ;

wire [31:0]S_0;

initial

begin

aclk_0 = 1;

end

always #5 aclk_0 = ~aclk_0 ;

DSP_TEST_wrapper DSP_TEST_wrapper_i

(.aclk_0(aclk_0),

.S_0(S_0));

endmodule

將測試文件添加進工程,點擊左側(cè)run simulation即可用modelsim進行仿真(需要將VIVADO和modelsim進行關(guān)聯(lián),在SIMULATION選項進行設(shè)置)

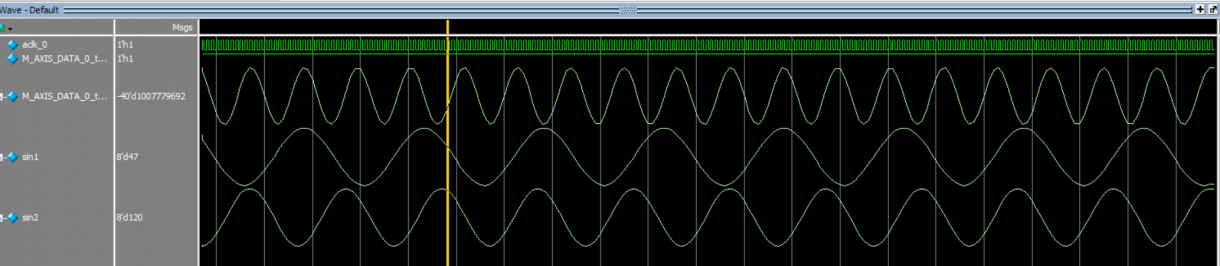

仿真結(jié)果如下圖所示(我將兩路正弦信號也連了管腳出來,便于仿真觀察,也可以在modelsim中把DDS IP的信號添加進來觀察,效果一樣)

編輯:hfy

-

dsp

+關(guān)注

關(guān)注

561文章

8247瀏覽量

366746 -

FPGA

+關(guān)注

關(guān)注

1660文章

22415瀏覽量

636496 -

濾波器

+關(guān)注

關(guān)注

162文章

8412瀏覽量

185747

發(fā)布評論請先 登錄

交流單相濾波器與三相濾波器的核心區(qū)別解析

通過vivado HLS設(shè)計一個FIR低通濾波器

Vivado仿真之后沒有出現(xiàn)仿真結(jié)果的解決方法

信號處理:指數(shù)移動平均 (EMA) 濾波器

有源濾波器與無源濾波器的區(qū)別

GNSS 低噪聲放大器前端模塊,集成前濾波器和后濾波器 skyworksinc

DC-DC和AC-DC開關(guān)電源的新型EMI濾波器設(shè)計方法

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

Sky5? 低電流 GNSS LNA 前端模塊,集成前置濾波器和后置濾波器 skyworksinc

基于 FPGA 的任意波形發(fā)生器+低通濾波器系統(tǒng)設(shè)計

OptiSystem應(yīng)用:增益平坦濾波器優(yōu)化

深入解讀智多晶FIR IP

基于Block Design方法的Vivado FIR濾波器設(shè)計與仿真

基于Block Design方法的Vivado FIR濾波器設(shè)計與仿真

評論