我們處在一個由數(shù)字計(jì)算機(jī)控制的模擬世界里。因此,物聯(lián)網(wǎng) (IoT) 設(shè)備的設(shè)計(jì)人員需要將模擬值高效地轉(zhuǎn)換為采樣數(shù)字表示。答案看似簡單,使用一個前置的模數(shù)轉(zhuǎn)換器 (ADC) 便能解決問題,然后 ADC 并非千篇一律。因此,設(shè)計(jì)人員需要了解各種拓?fù)洌约八鼈兣c應(yīng)用的對應(yīng)關(guān)系。

例如,ADC 可能設(shè)計(jì)用來優(yōu)化采樣率、功耗和精度等不同特征。本文將會討論一些常見 ADC 架構(gòu)的設(shè)計(jì)要求,然后介紹采用這些架構(gòu)的應(yīng)用,并展示其實(shí)現(xiàn)方法。

ADC 的作用

ADC 是一種常用的電子集成電路或模塊化器件,用于將模擬信號(通常為電壓)轉(zhuǎn)換為一系列經(jīng)采樣的離散數(shù)字表示(即數(shù)字)。ADC 執(zhí)行三種不同操作:采樣、量化和編碼。它們構(gòu)成了電壓計(jì)、示波器和頻譜分析儀等許多常見數(shù)字儀器的核心。它們還應(yīng)用于數(shù)字電路的前端,用于處理麥克風(fēng)、加速計(jì)、光學(xué)傳感器和其他需要將輸出轉(zhuǎn)換為數(shù)字域的變送器所提供的模擬信號,從而讓微處理器能夠處理這些數(shù)據(jù)。

目前人們已開發(fā)出多種 ADC 架構(gòu)或拓?fù)鋪韺δM信號進(jìn)行采樣和數(shù)字化。每種形式的 ADC 都有自己的特性、優(yōu)勢和不足之處。針對具體應(yīng)用選擇特定類型的 ADC,往往取決于速度、分辨率、精度、功耗和物理尺寸等測量要求。

ADC 的關(guān)鍵特征

ADC 必須執(zhí)行的第一項(xiàng)操作是對模擬信號進(jìn)行采樣。采樣操作由采樣和保持電路或跟蹤和保持電路執(zhí)行。采樣操作或奈奎斯特定理要求,采樣率必須高于信號帶寬的兩倍,才能從數(shù)字化樣本重建模擬信號。因此,ADC 的第一個重要特征就是采樣率,它決定了可以進(jìn)行數(shù)字化的最大信號頻率分量。

ADC 必須對每個樣本進(jìn)行量化,將采樣的電壓分解為有限數(shù)量的離散幅度電平。此特征通常描述為分辨率位數(shù)。例如,如果將信號分解為 8 位,則意味著存在 28 即 256 個離散電平。16 位 ADC 會將電壓范圍劃分為 65,536 個量化電平。

分辨率和最大采樣率均取決于 ADC 硬件。一般而言,ADC 的分辨率越高,最大采樣率越受限制。

ADC 的精度同時(shí)取決于分辨率和采樣率。分辨率會影響幅值精度和準(zhǔn)確性。其他影響幅值精度的因素還包括量化過程的線性度和垂直噪聲的影響。采樣率決定了定時(shí)精度和準(zhǔn)確性。

物理尺寸和功耗是另外兩個依賴電路拓?fù)涞膶傩浴K鼈儗τ谝恍┚哂谐叽缁蚩捎霉β氏拗频膽?yīng)用,例如物聯(lián)網(wǎng)設(shè)備或電池供電的便攜式儀器而言,是非常重要的考慮因素。物理尺寸和功耗高度依賴 ADC 拓?fù)洹?/p>

閃速、直接或并行?

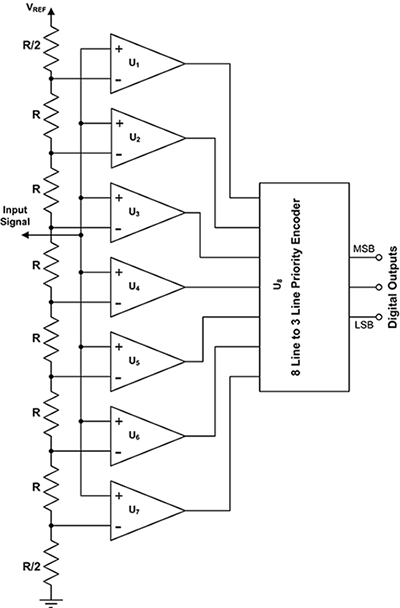

在概念上,最簡單的數(shù)字化儀莫過于閃速 ADC。閃速 ADC 也稱為直接或并行 ADC(圖 1)。

圖 1:閃速 ADC 使用多個閾值電壓均勻遞增的比較器,將模擬電壓轉(zhuǎn)換為數(shù)字值。該示例展示了一個具有 8 電平分辨率的 3 位 ADC。(圖片來源:Digi-Key Electronics)

閃速 ADC 的輸入通常源自采樣和保持或跟蹤和保持電路,模擬輸入在此電路中采樣并在轉(zhuǎn)換期內(nèi)保持恒定。經(jīng)采樣的信號被應(yīng)用于一系列模擬比較器,這些比較器的閾值電壓在 ADC 輸入電壓范圍內(nèi)均勻間隔,間隔值等于一個最低有效位 (LSB)。每個比較器的輸出會在輸入電壓超過分壓器為該比較器設(shè)定的閾值時(shí)改變狀態(tài)。圖中的示例顯示了一個 3 位 ADC,它需要 7 個比較器來生成 8 個可能的狀態(tài)。

一般情況下,一個 N 位閃速轉(zhuǎn)換器需要 (2N-1) 個比較器。比較器所產(chǎn)生的就是所謂的“溫度計(jì)碼”。輸入電壓越高,自底而上達(dá)到“1”狀態(tài)的比較器數(shù)量就越多。此代碼將應(yīng)用于一個優(yōu)先編碼器,并由該編碼器將其轉(zhuǎn)換為二進(jìn)制碼。

閃速轉(zhuǎn)換器的主要優(yōu)勢是速度。轉(zhuǎn)換時(shí)間僅包括比較器和解碼器的延遲。商用閃速轉(zhuǎn)換器的最大采樣率可達(dá)每秒 5 千兆次采樣 (GS/s)。閃速轉(zhuǎn)換器分辨率的限制因素就是所需要的比較器數(shù)量。8 位閃速 ADC 需要 255 個比較器。

分辨率每增加一位,該數(shù)量就會增加一倍。這意味著 ADC 的物理尺寸會隨分辨率呈指數(shù)級增長。此外還會造成另一項(xiàng)限制,即閃速轉(zhuǎn)換器所需的功率。這會限制它在線路供電型應(yīng)用中的使用。閃速分辨率的實(shí)際限制約為 8 位。

二進(jìn)制編碼

ADC 的二進(jìn)制輸出可采用多種方式進(jìn)行編碼。如果所轉(zhuǎn)換的信號為單極信號,則通常將其編碼為單極標(biāo)準(zhǔn)二進(jìn)制碼。此代碼將零值表示為全零 (0000…),將最大輸入值表示為全一 (1111…)。

如果信號為雙極信號,則通常表示為偏移二進(jìn)制或二的補(bǔ)碼二進(jìn)制。表 1 詳細(xì)說明了一個 4 位示例。

表 1:雙極數(shù)字信號的常見二進(jìn)制編碼。二的補(bǔ)碼二進(jìn)制是微處理器或數(shù)學(xué)處理器最常用的編碼方式。(圖片來源:Digi-Key Electronics)

二的補(bǔ)碼二進(jìn)制編碼是大多數(shù)基于微處理器或數(shù)學(xué)處理器的系統(tǒng)所用的編碼類型,因?yàn)榇司幋a有利于數(shù)學(xué)運(yùn)算。

流水線、分段式和兩步式 ADC

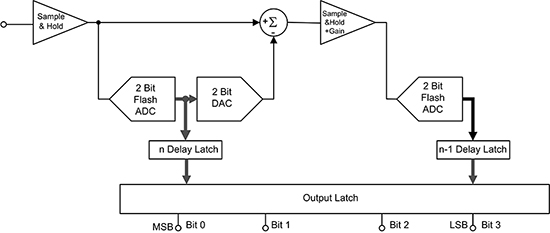

可通過將轉(zhuǎn)換操作分解為兩步或更多步并在每一級轉(zhuǎn)換較少的位數(shù),來減少閃速轉(zhuǎn)換器中的比較器數(shù)量。如果將閃速 ADC 拆分為兩個部分,則稱其為兩步式或分段式 ADC。如果將其拆分為兩個以上的部分,則稱其為流水線 ADC。兩步式 ADC 仍能以每秒幾百兆次采樣 (MS/s) 的速率進(jìn)行采樣(圖 2)。

圖 2:4 位兩步式或分段式 ADC 的功能框圖顯示,它將 4 位轉(zhuǎn)換器分解為兩個 2 位轉(zhuǎn)換器,以減少比較器的數(shù)量。(圖片來源:Digi-Key Electronics)。

此兩步式轉(zhuǎn)換器將需要 15 個比較器的 4 位轉(zhuǎn)換器分解為兩個 2 位的分段。每個分段使用三個比較器,共計(jì)六個比較器。該轉(zhuǎn)換器的工作原理是先轉(zhuǎn)換兩個最高有效位 (MSB)。第一個分段的數(shù)字輸出包含一個數(shù)模轉(zhuǎn)換器 (DAC),用于將信號轉(zhuǎn)換為模擬值,并從輸入信號中將其扣除。

所得的差值會被放大,并用于轉(zhuǎn)換兩個 LSB。然后在輸出鎖存器中捕獲組合結(jié)果。該轉(zhuǎn)換過程將會重復(fù)兩次,因此最大采樣率將會低于閃速轉(zhuǎn)換器的采樣率。例如,Analog Devices AD9203ARUZRL7 便是一個 10 位、40 MS/s 流水線 ADC,可用于解決高速模數(shù)轉(zhuǎn)換存在的問題。

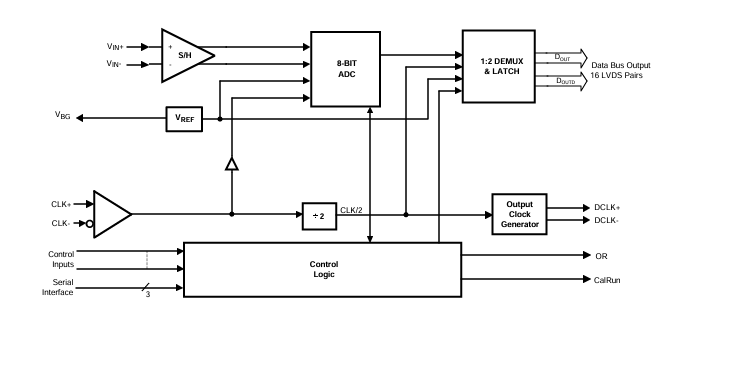

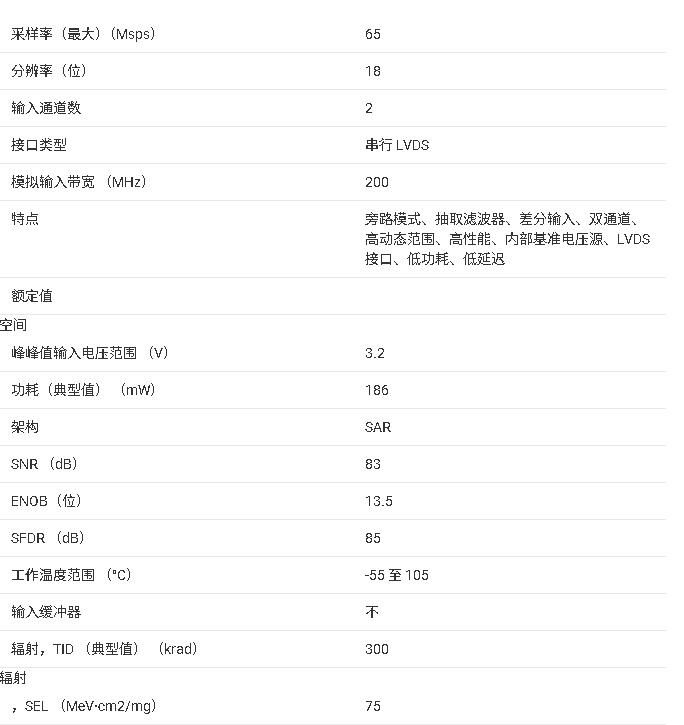

逐次逼近寄存器 (SAR) ADC

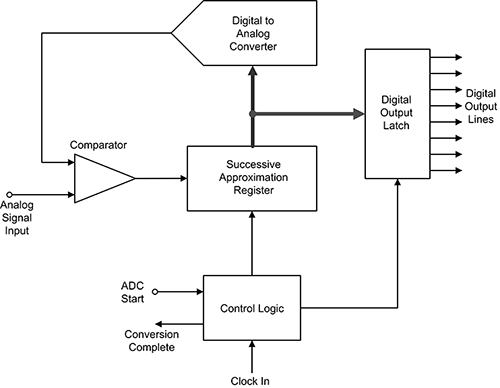

當(dāng)應(yīng)用需要更高的分辨率,同時(shí)不需要閃速或流水線 ADC 那么快的速度時(shí),逐次逼近寄存器 (SAR) 轉(zhuǎn)換器不失為一種不錯的選擇(圖 3)。SAR ADC 的分辨率為 12 到 16 位,采樣率高達(dá) 1 到 2 MS/s。

圖 3:SAR ADC 以中低功率要求實(shí)現(xiàn)了良好的分辨率。(圖片來源:Digi-Key)

與閃速 ADC 一樣,SAR ADC 使用前置采樣和保持或跟蹤和保持電路,在轉(zhuǎn)換過程期間維持樣本值。源自采樣和保持電路的信號將施加到比較器上。逐次逼近寄存器從量程中段開始,使用 DAC 將該值轉(zhuǎn)換為模擬電壓。

此“猜測”電壓將與比較器的信號輸入進(jìn)行比較。如果比較器輸出保持低電平,則將寄存器值遞增四分之一量程。基本上,寄存器值按照兩個步長因子降低或升高,直至比較器指示 DAC 轉(zhuǎn)換的寄存器內(nèi)容等于輸入信號電壓。這時(shí),轉(zhuǎn)換器會發(fā)出“轉(zhuǎn)換完成”的信號,并將數(shù)字值鎖存到輸出鎖存器中。

此轉(zhuǎn)換時(shí)間與 ADC 分辨率成正比,而分辨率取決于寄存器的長度。SAR ADC 以中低功率要求實(shí)現(xiàn)了良好的分辨率。例如,Maxim Integrated 的 MAX11665AUT-T 便是一款低成本、低功耗的 SAR ADC。作為一款每秒 500 千次采樣 (kS/s) 的 12 位 SAR ADC,它非常適合對傳感器輸出進(jìn)行數(shù)字化。

雙斜率積分 ADC

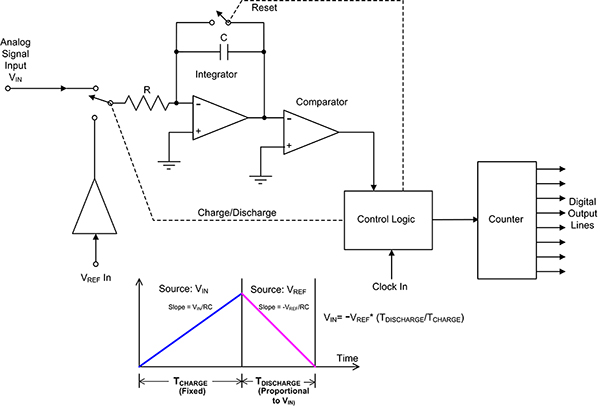

積分 ADC 具有高分辨率,同時(shí)可最大限度降低噪聲影響。雙斜率 ADC 是最常見的積分 ADC(圖 4)。

圖 4:雙斜率積分 ADC 的方框圖中包含的圖表顯示了如何使用充電/放電時(shí)間確定未知的輸入電壓。(圖片來源:Digi-Key Electronics)

一開始,輸入連接到積分器。輸入信號對電容器 C 進(jìn)行固定時(shí)間充電。充電時(shí)間結(jié)束后,積分器被連接到基準(zhǔn)電壓。這會將電容器放電到比較器所確定的零值。同時(shí)有一個計(jì)數(shù)器會測量電容器放電所用的時(shí)間。該時(shí)間與充電周期內(nèi)施加于電容器的輸入電壓成正比。借助已知的充電時(shí)間與測量的放電時(shí)間之間的簡單關(guān)系,即可計(jì)算出輸入電壓。

由于信號輸入被應(yīng)用于積分器,因此積分器的均化效應(yīng)會將任何噪聲信號的影響降至最低。雙斜率轉(zhuǎn)換器是需要高精度的高分辨率應(yīng)用的理想選擇。常見的分辨率為 12 到 16 位,最大采樣率可達(dá) 100 KS/s。

雙斜率 ADC 最廣為人知的應(yīng)用是數(shù)字電壓計(jì)(DVM 或 DMM)。Maxim Integrated 的 ICL7109CPL+ 型 12 位三態(tài)輸出 ADC 便是一種雙斜率轉(zhuǎn)換器,適用于以高達(dá)每秒 30 次的速率測量壓力、速度或流量等模擬信號。

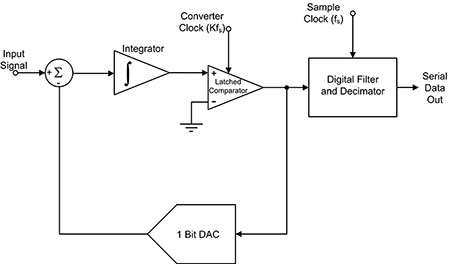

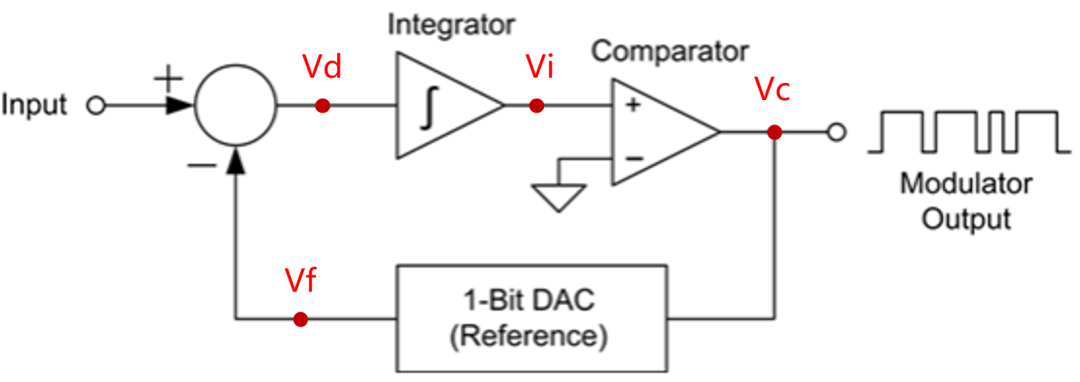

三角積分 ADC:低頻率、高分辨率

三角積分 ADC 可針對低頻信號提供最高的分辨率(16 到 24 位)。與雙斜率 ADC 一樣,它是另一種類型的積分?jǐn)?shù)字化儀(圖 5)。輸入信號通過一個加法器施加到積分器。積分器的輸出隨即施加于一個閂鎖比較器,并在其中與零電壓(接地)信號進(jìn)行比較。如果積分輸出不為零,則會反饋比較器輸出,從而使積分器輸出更接近零。以轉(zhuǎn)換器的時(shí)鐘速率重復(fù)此過程,直至積分器輸出達(dá)到零。比較器輸出構(gòu)成一個串行數(shù)據(jù)流,即轉(zhuǎn)換器的數(shù)字輸出。

三角積分 ADC 的采樣速率遠(yuǎn)高于設(shè)計(jì)采樣率要求的速率。

請注意,圖中的轉(zhuǎn)換器時(shí)鐘速率快于輸出樣本的時(shí)鐘速率(比例因子為 K)。此“過采樣”提供的額外樣本將被用于對轉(zhuǎn)換器輸出進(jìn)行數(shù)字濾波。使用抽取器將輸出采樣率恢復(fù)至指定的樣本時(shí)鐘速率。

Analog Devices 的 AD7734BRUZ 型 ADC 是一款 24 位、4 通道三角積分?jǐn)?shù)字化儀,適用于各種工藝和工業(yè)控制應(yīng)用。

圖 5:三角積分 ADC 在音頻、工藝和工業(yè)控制應(yīng)用中廣泛用于低頻信號的高分辨率數(shù)字化。(圖片來源:Digi-Key)

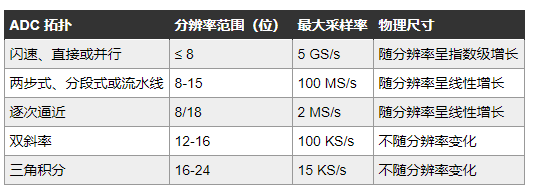

表 2 概括了所討論的五種 ADC 類型的分辨率和最大采樣率。

表 2:本文所討論的五種 ADC 類型的 ADC 工作特征。(圖片來源:Digi-Key Electronics)

拓?fù)溥x擇示例

以一個應(yīng)用為例:該應(yīng)用對一個使用 40 kHz 變送器的便攜式超聲測距儀的信號進(jìn)行數(shù)字化。目標(biāo)反射為發(fā)射脈沖幅度的 -40 dB (1/100)。

必須以至少兩倍于 40 kHz 信號頻率的速率進(jìn)行信號采樣。最好以 40 kHz 的四倍或更高倍數(shù)進(jìn)行采樣,因此目標(biāo)采樣率范圍為 160 kHz 或更高。而且,最好設(shè)置不低于預(yù)期值 40 dBm 10 倍的分辨率,即 60 dB。根據(jù)經(jīng)驗(yàn)規(guī)則,每 6 dB 需要 1 位分辨率,因此需要 10 位以上分辨率的 ADC。 此外,作為便攜式儀器,還需要考慮功耗問題。參考表 2,逐次逼近轉(zhuǎn)換器成為最佳選擇。前面提到的 SAR ADC 示例器件 Maxim Integrated MAX11665AUT-T 便非常適合這一應(yīng)用。

總結(jié)

由于無法同時(shí)兼顧最大采樣率和分辨率,因此 ADC 的選擇主要在于這兩項(xiàng)特征的權(quán)衡。根據(jù)具體應(yīng)用,物理尺寸和功耗等其他考慮因素也可能起著重要作用,在選擇過程中應(yīng)給予應(yīng)有的重視。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

129968 -

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555943 -

工業(yè)控制

+關(guān)注

關(guān)注

38文章

1660瀏覽量

91501

發(fā)布評論請先 登錄

米爾T113核心板的農(nóng)機(jī)中控屏顯方案解析

高性能低功耗8位1.5GSPS ADC081500深度剖析

ADC3683-SP 技術(shù)文檔總結(jié)

ADC3648/ADC3649 ADC 產(chǎn)品文檔總結(jié)

ADC3568/ADC3569 ADC 產(chǎn)品文檔總結(jié)

ADC3548/ADC3549 ADC 產(chǎn)品文檔總結(jié)

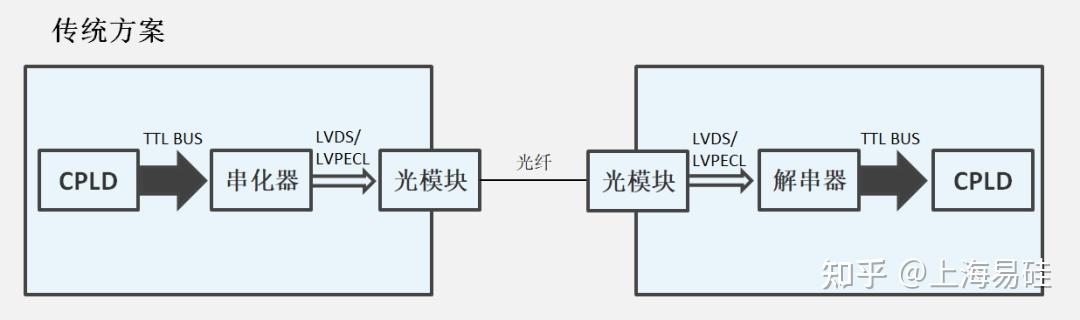

光端機(jī)新設(shè)計(jì):AG32 + MS21112S 極簡架構(gòu)實(shí)現(xiàn)高性能低成本替代

全網(wǎng)首發(fā),Multisim實(shí)現(xiàn)Σ-Δ型ADC原理仿真

介紹三種常見的MySQL高可用方案

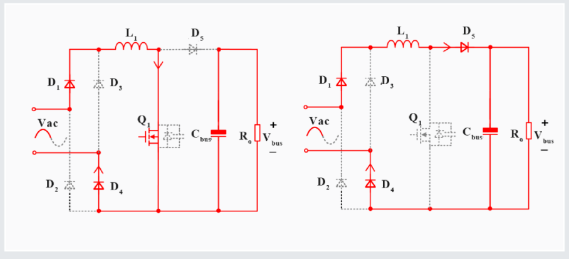

常見的PFC拓?fù)?b class='flag-5'>架構(gòu)及控制方法

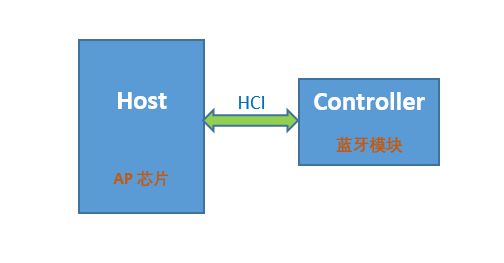

三種藍(lán)牙架構(gòu)實(shí)現(xiàn)方案(藍(lán)牙協(xié)議棧方案)

ADC的五大架構(gòu)及其工作原理

常見ADC架構(gòu)的設(shè)計(jì)應(yīng)用及實(shí)現(xiàn)方案

常見ADC架構(gòu)的設(shè)計(jì)應(yīng)用及實(shí)現(xiàn)方案

評論