作者:貓叔 科學(xué)計(jì)算Tech微信公眾號(hào)

?在前面的章節(jié)中,我們用了很多Tcl的指令,但有些指令并沒(méi)有把所有的參數(shù)多列出來(lái)解釋,這一節(jié),我們就把約束中的Tcl指令詳細(xì)講一下。

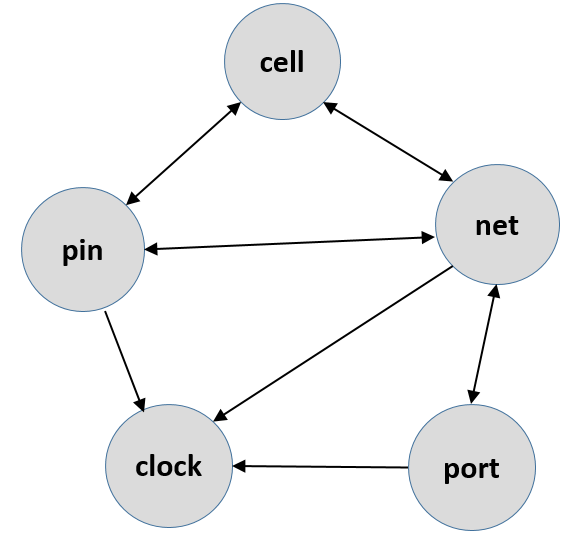

我們前面講到過(guò)get_pins和get_ports的區(qū)別,而且我們也用過(guò)get_cells、get_clocks和get_nets這幾個(gè)指令,下面就通過(guò)一張圖直觀展現(xiàn)它們的區(qū)別。

get_clocks后面的對(duì)象是我們之前通過(guò)create_clocks或者create_generated_clocks創(chuàng)建的時(shí)鐘,不在硬件上直接映射。

我們?cè)賮?lái)看下各個(gè)命令的屬性。

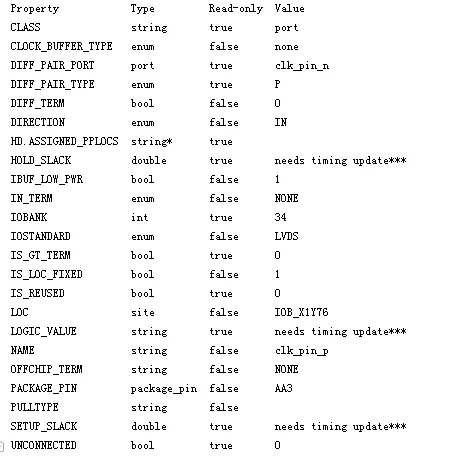

1. port

我們可以通過(guò)Tcl腳本查看port的所有屬性,比如上面的wave_gen工程中,有一個(gè)port是clk_pin_p,采用如下腳本:

set inst [get_ports clk_pin_p] report_property $inst

顯示如下:

get_ports的使用方法如下:

# 獲取所有端口 get_ports * # 獲取名稱中包含data的端口 get_ports *data* # 獲取所有輸出端口 get_ports -filter {DIRECTION == OUT} # 獲取所有輸入端口 all_inputs # 獲取輸入端口中名字包含data的端口 get_ports -filter {DIRECTION == IN} *data* # 獲取總線端口 get_ports -filter {BUS_NAME != ""}

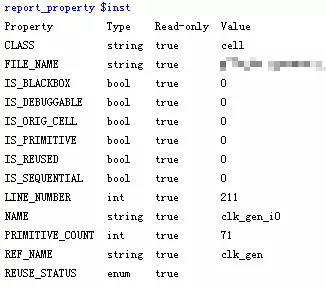

2. cell

按照上面的同樣的方式,獲取cell的property,如下:

get_cells的使用方法如下:

# 獲取頂層模塊

get_cells *

# 獲取名稱中包含字符gen的模塊

get_cells *gen*

# 獲取clk_gen_i0下的所有模塊

get_cells clk_gen_i0/*

# 獲取觸發(fā)器為FDRE類型且名稱中包含字符samp

get_cells -hier filter {REF_NAME == FDRE} *samp*

# 獲取所有的時(shí)序單元邏輯

get_cells -hier -filter {IS_SEQUENTIAL == 1}

# 獲取模塊uart_rx_i0下兩層的LUT3

get_cells -filter {REF_NAME == LUT3} *uart_tx_i0/*/*

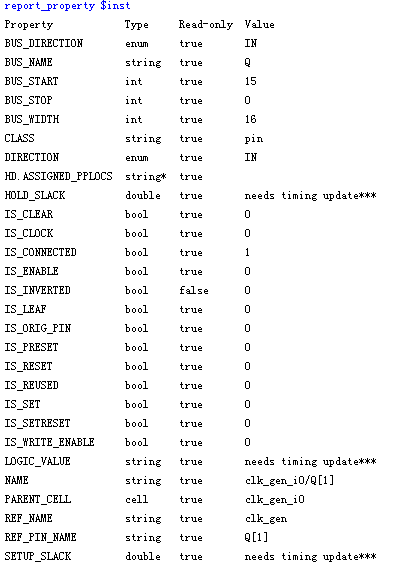

3. pin

獲取pin的property,如下:

get_pins的使用方法如下:

# 獲取所有pins get_pins * # 獲取名稱中包含字符led的引腳 get_pins -hier -filter {NAME =~ *led*} # 獲取REF_PIN_NAME為led的引腳 get_pins -hier -filter {REF_PIN_NAME == led} # 獲取時(shí)鐘引腳 get_pins -hier -filter {IS_CLOCK == 1} # 獲取名稱中包含cmd_parse_i0的使能引腳 get_pins -filter {IS_ENABLE == 1} cmd_parse_i0/*/* # 獲取名稱中包含字符cmd_parse_i0且為輸入的引腳 get_pins -filter {DIRECTION == IN} cmd_parse_i0/*/*

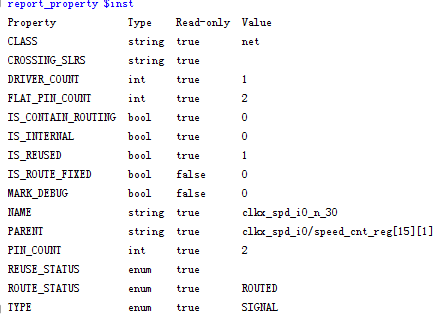

4. net

獲取pin的property,如下:

get_nets的使用方法如下:

# 獲取所有nets

get_nets *

# 獲取名稱中包含字符send_resp_val的網(wǎng)線

get_nets -hier *send_resp_val*

get_nets -filter {NAME =~ *send_resp_val*} -hier

# 獲取穿過(guò)邊界的同一網(wǎng)線的所有部分

get_nets {resp_gen_i0/data4[0]} -segments

# 獲取模塊cmd_parse_i0下的所有網(wǎng)線

get_nets -filter {PARENT_CELL == cmd_parse_i0} -hier

# 獲取模塊cmd_parse_i0下的名稱中包含字符arg_cnt[]的網(wǎng)線

get_nets -filter {PARENT_CELL == cmd_parse_i0} -hier *arg_cnt[*]

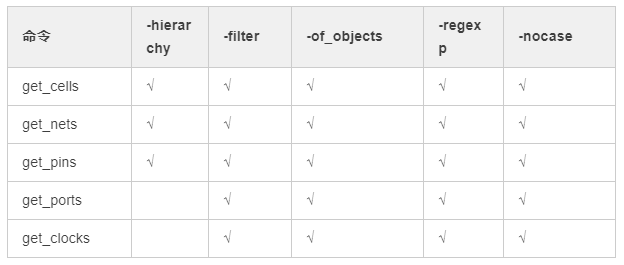

這5個(gè)tcl指令的常用選項(xiàng)如下表:

?這5個(gè)Tcl命令對(duì)應(yīng)的5個(gè)對(duì)象之間也有著密切的關(guān)系,下圖所示的箭頭的方向表示已知箭頭末端對(duì)象可獲取箭頭指向的對(duì)象。

以wave_gen中的clk_gen_i0模塊為例來(lái)說(shuō)明上面的操作:

# 獲取模塊的輸入引腳

get_pins -of [get_cells {clk_gen_i0/clk_core_i0}] -filter {DIRECTION == IN}

# 已知引腳名獲取所在模塊

get_cells -of [get_pins clk_gen_i0/clk_core_i0/clk_in1_n]

# 已知模塊名獲取與該模塊相連的網(wǎng)線

get_nets -of [get_cells {clk_gen_i0/clk_core_i0}]

# 已知引腳名獲取與該引腳相連的網(wǎng)線

get_nets -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

# 已知時(shí)鐘引腳獲取時(shí)鐘引腳對(duì)應(yīng)的時(shí)鐘

get_clocks -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

需要注意的是:

1. -hier不能和層次分隔符“/”同時(shí)使用,但“/”可出現(xiàn)在-filter中

2. 可根據(jù)屬性過(guò)濾查找目標(biāo)對(duì)象

3. -filter中的屬性為:“==”(相等)、“!=”(不相等)、"=~"(匹配)、"!~"(不匹配),若有多個(gè)表達(dá)式,其返回值為bool類型時(shí),支持邏輯操作(&& ||)

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636354 -

TCL

+關(guān)注

關(guān)注

11文章

1807瀏覽量

91527 -

時(shí)序約束

+關(guān)注

關(guān)注

1文章

120瀏覽量

13962

發(fā)布評(píng)論請(qǐng)先 登錄

Vivado時(shí)序約束中invert參數(shù)的作用和應(yīng)用場(chǎng)景

輸入引腳時(shí)鐘約束_Xilinx FPGA編程技巧-常用時(shí)序約束詳解

開源RISC-V處理器(蜂鳥E203)學(xué)習(xí)(二)修改FPGA綜合環(huán)境(移植到自己的Xilinx FPGA板卡)

在Windows10上運(yùn)行vivado使用tcl文件創(chuàng)建E203項(xiàng)目路徑錯(cuò)誤的問(wèn)題

win10環(huán)境下使用vivado生成.bit與.mcs文件

蜂鳥e203移植fpga上如何修改約束文件

技術(shù)資訊 I Allegro 設(shè)計(jì)中的走線約束設(shè)計(jì)

云知聲攜手TCL空調(diào)煥新智能家電體驗(yàn)

圖解環(huán)路設(shè)計(jì)及控制技術(shù)探討

PLL技術(shù)在FPGA中的動(dòng)態(tài)調(diào)頻與展頻功能應(yīng)用

電機(jī)繞組滾動(dòng)烘干爐防爆安全技術(shù)探討

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

一文詳解Vivado時(shí)序約束

FPGA約束中的Tcl指令技術(shù)探討

FPGA約束中的Tcl指令技術(shù)探討

評(píng)論