FPGA 設計是有章可循的,如果用的是 Xilinx 的 FPGA,這個“章”就是 UG949。最新版的 UG949 是 2020.1 版本,整個文檔共六大章節 306 頁。對于如此之多的內容該如何消化吸收呢?首先,了解一下 UG949 的背景信息。

UG949 是什么?

UG949 是很多工程師的經驗總結,這些經驗總結告訴我們在實現 FPGA 設計時該如何去做,例如:PCB 設計時的注意事項、什么才是良好的代碼風格、時序約束該怎么做、時序收斂有哪些方法等等。

為什么要用 UG949?

隨著微電子工藝的不斷發展,FPGA 的規模也越來越大,例如出現了多 die 芯片(SSI 器件),隨之 FPGA 設計也越來越復雜,這意味著發現設計潛在的問題并解決也變得愈發困難。

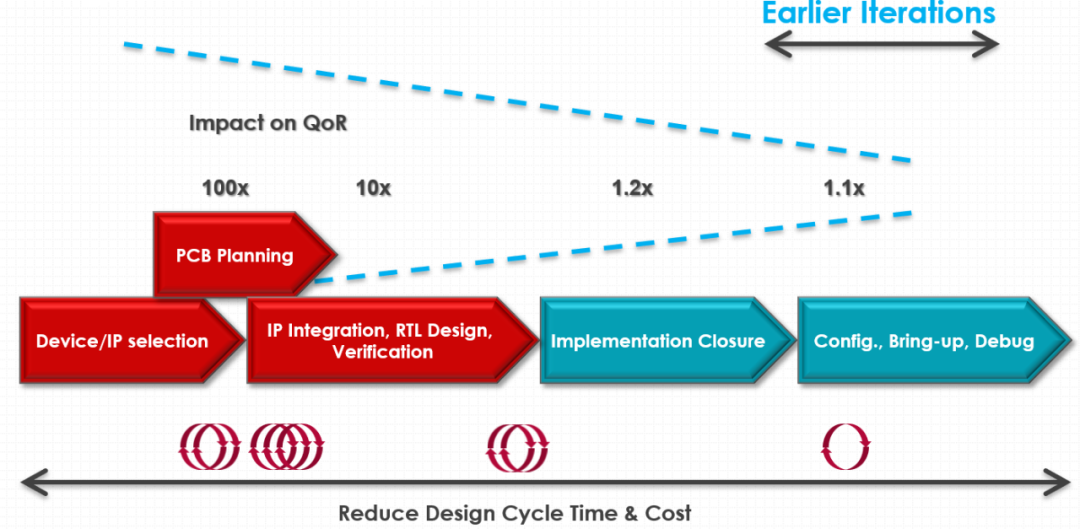

好在 Xilinx 推出了新一代開發工具 Vivado,同時 UG949 也應運而生。從而,工程師們可以遵循 UG949 的設計方法最大可能地避免一些問題并從中找到一些解決問題的方法。簡言之,UG949 的核心思想就是盡可能地幫工程師在設計初期發現問題并解決問題,最大化地提升開發效率,降低迭代周期。這是因為問題發現地越晚,解決起來越困難。

UG949 面向哪些對象?

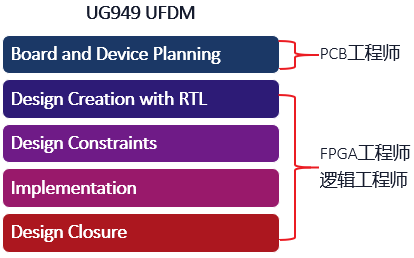

UG949 不僅僅是面向 FPGA 工程師,也面向 PCB 工程師和邏輯工程師,三類工程師均可從中受益。這是因為 UG949 既涵蓋了片外板級相關內容,例如 DDR 存儲器接口電路設計規則、高速收發器電路設計規則、FPGA 配置電路設計規則、系統級功耗解決方案等,也涵蓋了片內設計規則的相關內容,例如設計流程、代碼風格、時序約束和時序收斂等,如下圖所示。

如何閱讀 UG949?

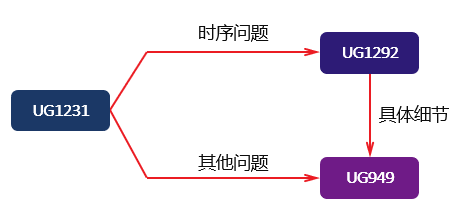

事實上,跟 UG949 相關的文檔包括 UG1231、UG1292 和 XTP301。如果把 UG949、UG1231 和 UG1292 打包看作一部字典的話,那么 UG949 就是字典的正文,UG1231 就是字典的索引(只有兩頁),UG1292 則是字典部分內容的濃縮精華版。既然是字典,我們就不需要從頭到尾一頁一頁地讀,而是根據工作需求結合索引,做到有的放矢,達到事半功倍。

例如,如果你是 PCB 工程師,打開 UG1231,瀏覽到 PCB Designer 部分,會引導你查看 UG949 的 Board and Device Planning 章節,除此之外,如果設計中用到 DDR 存儲器,還需要根據 Memory Interface IP Design Checklists 對相關電路進行檢查核對,同時根據芯片型號選擇相應的 Schematic Design Checklists 對相關電路進行檢查核對。

如果你是邏輯工程師,已到了設計的中后期,需要處理時序違例問題,打開 UG1231,瀏覽到第 2 頁,會引導你查看 UG949 Design Closure 章節。這章內容的核心部分之一是 Timing Closure,共 88 頁。這 88 頁內容已濃縮到 UG1292 中,因此時序問題可首先查看 UG1292。

閱讀流程如下圖所示。

如何使用 UG949?

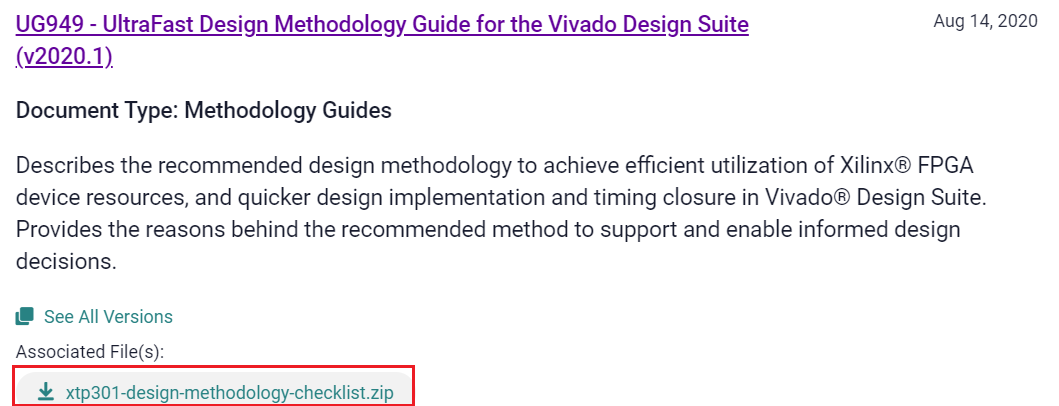

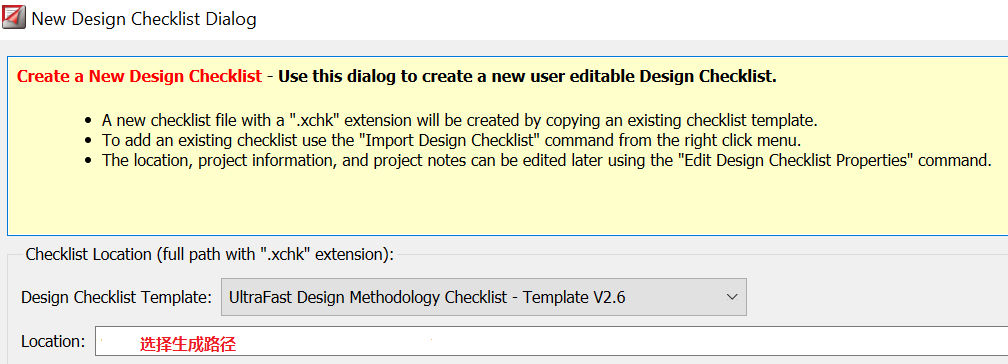

為了幫助工程師們有效地使用和借鑒 UG949 中的設計方法,Xilinx 專門提供了 UFGM 檢查表 XTP301。這個表格可以從 Xilinx 官網下載,也可以從 Documentation Navigator 直接生成,如下圖所示。

原文標題:300 多頁方法論,Xilinx FPGA 設計竟然有”章”可循?

文章出處:【微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636282 -

Xilinx FPGA

+關注

關注

1文章

29瀏覽量

7387

原文標題:300 多頁方法論,Xilinx FPGA 設計竟然有”章”可循?

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

MC-306 標記 NRND 之后:32.768 kHz RTC 晶體的工程替代思路與選型要點

使用Xilinx 7系列FPGA的四位乘法器設計

Xilinx FPGA串行通信協議介紹

請問如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發板上?

將蜂鳥E203的內核移植到fpga之后該怎么進行二次開發呢?

開源RISC-V處理器(蜂鳥E203)學習(二)修改FPGA綜合環境(移植到自己的Xilinx FPGA板卡)

商品詳情頁內容更新接口設計與實現

一文詳解xilinx 7系列FPGA配置技巧

凱米斯科技iDO-306熒光法溶解氧傳感器:精準測量,智慧守護水質

IGBT模塊吸收回路分析模型

Xilinx Shift RAM IP概述和主要功能

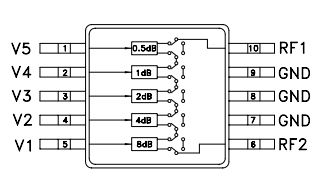

HMC306AMS10/306AMS10E 0.5 dB LSB GaAs MMIC 5位數字衰減器技術手冊

足足306頁Xilinx FPGA ,對于如此之多的內容該如何消化吸收呢?

足足306頁Xilinx FPGA ,對于如此之多的內容該如何消化吸收呢?

評論