PCB設(shè)計人員通常會忽略的PCB基板材料的一個方面是基板介電常數(shù)對PCB中信號完整性的影響。色散存在于任何材料中,這會使數(shù)字信號失真,尤其是在設(shè)備以非常高的速度切換時。設(shè)計人員在為其下一個設(shè)備選擇合適的基板時,需要在成本,性能和其他材料特性之間進(jìn)行權(quán)衡。

您應(yīng)該使用高k或低k PCB基板材料嗎?

回答這個問題實際上是在考慮介電常數(shù)和其他PCB基板材料屬性之間的折衷。一些PCB基板材料(例如Rogers高速層壓板或其他陶瓷材料)具有更理想的光學(xué)特性,但成本更高。這些其他材料在制造過程中可能更難以使用,因此它們也帶來更高的制造成本。某些PCB基板材料更適合與RF電路和組件配合使用,并且可能是在極高速度和高頻下運行的關(guān)鍵任務(wù)應(yīng)用的最佳選擇。

雖然我們通常考慮介電常數(shù)的虛部,但從布局的角度來看,實部(即折射率)也很重要。介電常數(shù)的實部決定電磁波在材料中傳播的速度,而虛部則決定電磁波在材料中傳播的增益或損耗。就PCB設(shè)計而言,介電常數(shù)和走線幾何形狀將決定信號如何沿走線傳播。

標(biāo)準(zhǔn)FR4基板的介電常數(shù)約為4.5,盡管基板中使用的編織圖案會影響介電常數(shù)的精確值。陶瓷填充的PTFE基板的介電常數(shù)可以從?3調(diào)整到?10,并且通過使用不同的填料和粘結(jié)材料可以將損耗降低一個數(shù)量級。調(diào)整對PCB基板材料中的分散性的影響各不相同,盡管最好的材料制造商將掌握這些數(shù)據(jù)以供設(shè)計人員使用。

實際部分:傳播延遲和阻抗

如果您記得物理學(xué)上的101類,那么您就會知道折射率(即介電常數(shù)的實部的平方根)決定了電磁波在材料中傳播的速度。跡線上的信號速度取決于有效介電常數(shù),該有效介電常數(shù)由跡線的幾何形狀和PCB基板材料的介電常數(shù)確定。

注意,對于給定的基板材料,帶狀線的有效介電常數(shù)將大于微帶線。如果查看微帶線和帶狀線的阻抗方程式,則意味著在特征阻抗計算中不應(yīng)包括介電常數(shù)的虛部。相反,阻抗僅由基板介電常數(shù)的實部和走線幾何形狀確定。

走線上的信號速度會影響到傳輸線行為的轉(zhuǎn)變。跡線越長,信號的傳播時間就越長。考慮傳輸線效應(yīng)以及阻抗匹配和端接要求的關(guān)鍵閾值是傳播延遲大于信號上升時間的?35%。

虛部:損耗正切,寄生和損耗

介電常數(shù)的虛部(也稱為耗散因數(shù)或損耗角正切)決定了信號在走線時的損耗。總體上,帶電磁波的走線有三種主要的損耗來源:

l介電損耗:這是由于PCB基板材料中感應(yīng)極化波的大小和相位而引起的。這與介電常數(shù)的虛部有關(guān),虛部與襯底的電導(dǎo)率成比例。

l跡線中的電阻加熱:由于跡線中的薄層電阻,一些電磁能被轉(zhuǎn)換為熱量。注意,由于集膚效應(yīng),在高頻下,跡線的薄層電阻可能會很大。

l寄生:基板具有一些殘余電導(dǎo),這允許信號中的某些電流流向返回線。襯底介電常數(shù)的實部也決定了寄生電容。這兩個術(shù)語共同確定損耗正切。

通常不考慮的其他三個損失來源是:

l插入損耗:這在傳輸線中很重要,與特性阻抗,信號頻率,走線幾何形狀和有效介電常數(shù)有關(guān)。

l輻射損耗:任何振蕩電流都會發(fā)射電磁波,從而將能量帶離電路。

l導(dǎo)體的粗糙度:電磁場將集中在導(dǎo)體的粗糙邊緣附近,從而導(dǎo)致這些區(qū)域的電阻損耗更大。

PCB中走線的傳輸線模型和阻抗模型通常會省略介電常數(shù)的虛部,但是走線的幾何形狀和嵌入PCB基板材料中的幾何形狀會通過更改有效介電常數(shù)(實部和虛部)來影響損耗。

微帶上的信號比帶狀線上的信號損耗更低,因為帶狀線跡線被電介質(zhì)包圍。這是因為該波部分通過導(dǎo)線周圍的電介質(zhì)行進(jìn),并且會遭受基板的電介質(zhì)損耗。由于導(dǎo)體與PCB基板材料之間的界面處的連續(xù)性,這些波將耦合回到跡線中,這決定了信號沿導(dǎo)體導(dǎo)引時的損耗。當(dāng)與電阻加熱一起考慮時,這解決了上面的前兩點。

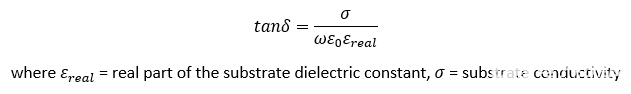

當(dāng)與介電常數(shù)的實部一起考慮時,分別與實部和虛部相關(guān)的襯底的寄生電容和電導(dǎo)率確定損耗角正切。可以用以下公式來總結(jié):

?

?

最初可以得出的結(jié)論是,生產(chǎn)出的體積較小且必須在非常高的速度或頻率下保持信號完整性的設(shè)備應(yīng)使用損耗較低的材料。從傳播延遲的角度來看,使用較低的介電常數(shù)是有益的,盡管它會對PCB中走線和傳輸線的特征阻抗產(chǎn)生混合影響。需要仔細(xì)建模才能確定下一個高速或高頻系統(tǒng)介電常數(shù)的實部和虛部的可接受范圍。

隨著設(shè)計變得更加復(fù)雜,并正確地建模PCB基板材料的介電常數(shù),診斷信號完整性問題可能會非常棘手。強大的信號完整性和功率完整性工具在Sigrity的寬帶SPICE包為設(shè)計者提供了他們需要診斷介電常數(shù)對信號完整性的高速和高頻系統(tǒng)的影響的工具。這種獨特的工具考慮了用于各種電路分析的一系列IC封裝。

-

電路板設(shè)計

+關(guān)注

關(guān)注

1文章

132瀏覽量

17420 -

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4932瀏覽量

95643 -

線路板設(shè)計

+關(guān)注

關(guān)注

0文章

61瀏覽量

8480 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3515瀏覽量

6510

發(fā)布評論請先 登錄

低介電常數(shù)與高介電常數(shù)的高分子材料:從機理、結(jié)構(gòu)到應(yīng)用的全面解析

E4990A阻抗分析儀測量絕緣材料介電常數(shù)的測試步驟

如何用Keysight E4990A阻抗分析儀搞定PCB材料Dk/Df測試

技術(shù)資訊 I 信號完整性與阻抗匹配的關(guān)系

串?dāng)_如何影響信號完整性和EMI

高頻高速PCB板材材料技術(shù)解析與應(yīng)用趨勢

了解信號完整性的基本原理

醫(yī)療PCB基板材質(zhì)大揭秘:選錯材質(zhì)可能致命!

趨勢觀察 高頻通信時代,Dk值為何成了PCB設(shè)計“生命線”?

信號完整性測試基礎(chǔ)知識

PCB的介質(zhì)損耗角是什么“∠”?

技術(shù)資訊 | 信號完整性測試基礎(chǔ)知識

PCB基板材料的介電常數(shù)和信號完整性

PCB基板材料的介電常數(shù)和信號完整性

評論