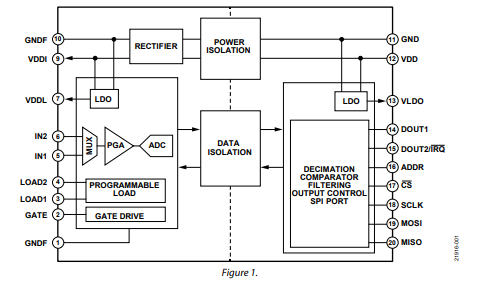

第二篇以德州儀器(TI)的高速ADC芯片——ads52j90為例,介紹完了4線SPI配置時序。本篇將以該芯片SPI結構為例,具體介紹如何利用verilog實現4線SPI配置時序。

無論實現讀還是寫功能,都先要提供SCLK。假如FPGA系統工作時鐘40MHz,我們可以利用計數器產生一個n分頻的時鐘作為SCLK,本例中n取8,SCLK頻率5MHz。SCLK產生的代碼如下:

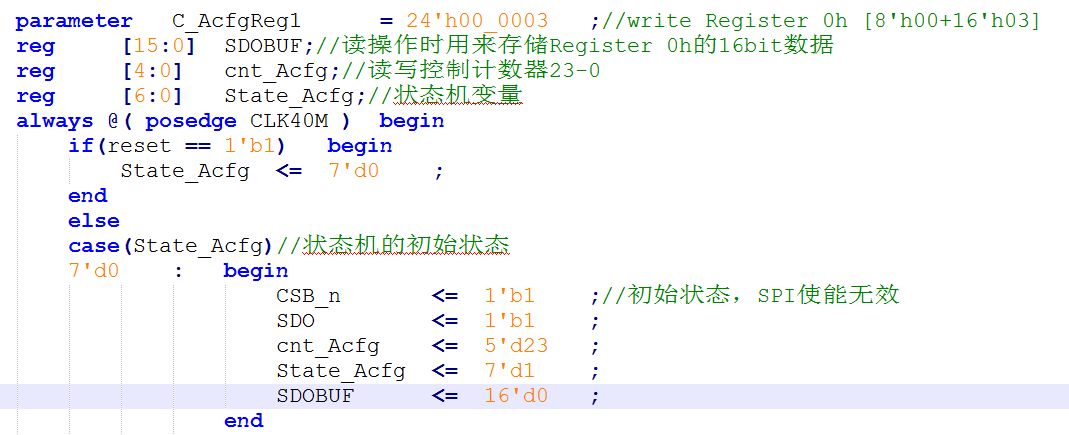

SCLK時鐘有了,接下來我們建立一個狀態機實現讀和寫功能:

初始化狀態的下一個狀態就是寫寄存器操作了,每次SCLK的上升沿寫入數據:

寫完一個寄存器參數,CSB先拉高。接下來在進入下一個狀態,本篇例子下一個狀態的操作是讀取對應寄存器地址的數據。我們首先需在SCLK的上升沿寫入8bit的寄存器地址,接下來在SCLK的下降沿讀取16bit的數據。

到此,讀寫操作都完成了。代碼上的注釋可以便于大家理解,大家還可以仿真看一下波形加深理解。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

30文章

1374瀏覽量

114530 -

SPI

+關注

關注

17文章

1885瀏覽量

101264 -

ADC芯片

+關注

關注

3文章

88瀏覽量

21089

原文標題:FPGA通過SPI對ADC配置簡介(四)---Verilog實現4線SPI配置

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

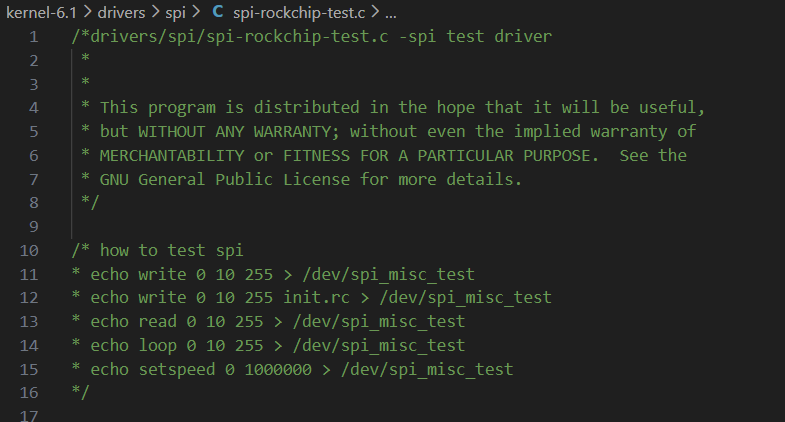

RK?平臺?SPI?開發完全指南(驅動?+?配置?+?測試?+?優化)

Linux 平臺 SPI 驅動已形成完善的開發體系,支持 Master/Slave 雙模式、多速率適配及靈活配置。本文基于 Rockchip 官方開發指南,從功能特性、驅動配置、測試驗證到優化方案

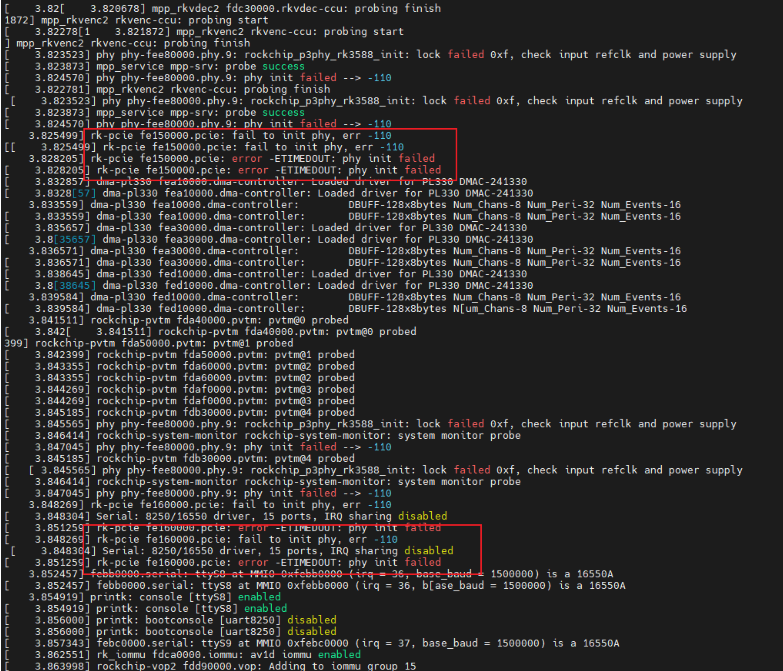

實戰復盤:RK3588 SPI+PCIe3x4方案啟動修復,從節點配置到驅動適配全解析

? ? ? 在 RK3588 嵌入式項目中, “ 接口配置不匹配 ” 是高頻踩坑點 —— 近期 基于 linux6.1 內核 調試 SPI 閃存 +PCIe3x4 外設 方案時,就遇到了 “eMMC

FPGA實現基于SPI協議的Flash驅動控制芯片擦除

本篇博客具體包括SPI協議的基本原理、模式選擇以及時序邏輯要求,采用FPGA(EPCE4),通過SPI通信協議,對flash(W25Q16BV)存儲的固化程序進行芯片擦除操作。

GPIOB模擬spi的方法及lcd屏幕的接入

越高,數據傳輸速率越快。由于spi接口較為簡單,同時《RISC-V架構與嵌入式開發快速入門》書中也詳細介紹過,在此原理部分介紹從略。

二、spi接口及lcd主要代碼實現

lcd所需的GPIOB的

發表于 10-30 07:59

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRA

數字電壓表設計教程之使用FPGA實現SPI協議通訊

LTC2308通過一個標準4線SPI數字接口進行通信。LTC2308模數轉換芯片有8個ADC通道和12位的分辨率,輸入信號時鐘頻率范圍不超過500KHz,按照Nyquist采樣定理則建議輸入信號在250KHz以下。

【RA4L1-SENSOR】SPI點亮16級灰階OLED顯示屏

瑞薩 R7FA4L1BD4CFP 有 1 個 SPI 接口,除此之外,還有 6 個 SCI 接口可以實現 Simple SPI 功能,這次使用 SP

發表于 06-09 01:14

ADE1202雙通道可配置隔離式數字輸入技術手冊

輸入或接觸輸入。DOUTx 引腳上的 ADE1202 數字輸出信號反映用戶可配置信號調理后的輸入信號狀態。SPI 協議支持尋址,允許多達八個套件共享一個 4 線

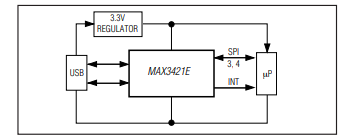

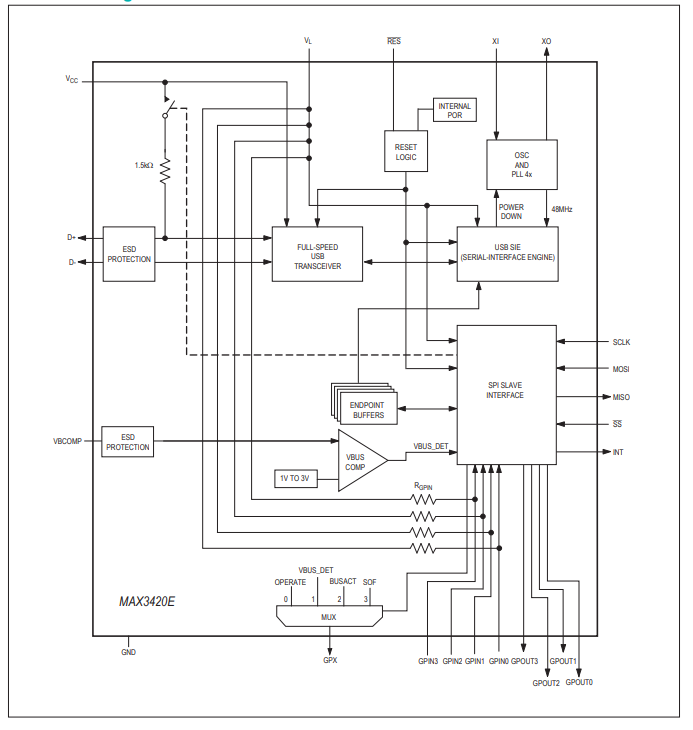

MAX3421E USB外設/主機控制器,SPI接口技術手冊

串行接口引擎(SIE)處理底層USB協議,如錯誤校驗和總線重試。通過頻率高達26MHz的SPI?接口訪問寄存器組,實現MAX3421E的控制。利用簡易的3線或

【RA-Eco-RA4M2開發板評測】SPI點亮16級灰階OLED顯示屏

瑞薩 RA4M2R7FA4M2AD3CFP 有 1 個 SPI 接口,除此之外,還有 6 個 SCI 接口可以實現 Simple SPI 功能,這次使用 RA

發表于 05-05 15:12

AD7606C-18的硬件串行模式,如何使用三線SPI?

問題,八個通通道輸入均連在一起,結果如下圖所示。

但是當我使用三線SPI模式讀取數據時,數據就錯亂了,即使SCLK頻率降低到5MHz,數據也是完全錯亂的。我可以確定三線模式下,SCLK,BUSY之間的

發表于 04-28 07:49

如何利用verilog實現4線SPI配置時序

如何利用verilog實現4線SPI配置時序

評論